窗口看门狗verilog代码是多少

-

led闪烁的Verilog代码

以下是一个简单的Verilog代码,用于控制FPGA板上的LED闪烁。代码使用了时钟分频器来控制LED的闪烁速度,通过一个计数器来确定LED的状态(开/关)。 这个代码将时钟分频到了1秒,LED会每秒钟切换一次状态。你可以根据自己的需要调整闪烁速度,只需要修改COUNTER_MAX的值即可。

-

【Verilog编程】线性反馈移位寄存器(LFSR)原理及Verilog代码实现

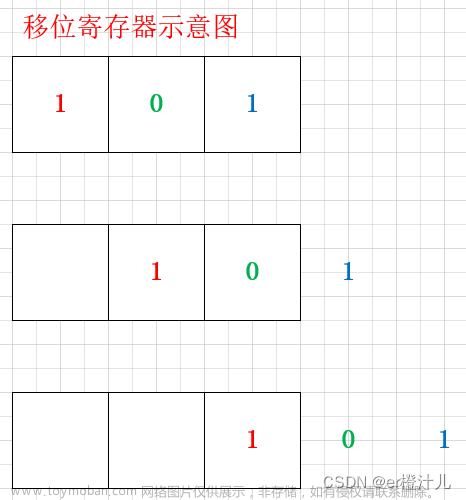

移位寄存器 :指若干个寄存器排成一列,每个寄存器中存放1bit二进制数据(0或1),每个时钟周期向左或向右移动一个bit。下图所示为一个向右移动的移位寄存器。 反馈移位寄存器(Feedback Shift Register,FSR) :每个时钟脉冲,移位寄存器向右移动一位,则移位寄存器的左左侧就

-

CRC校验Verilog代码在线生成

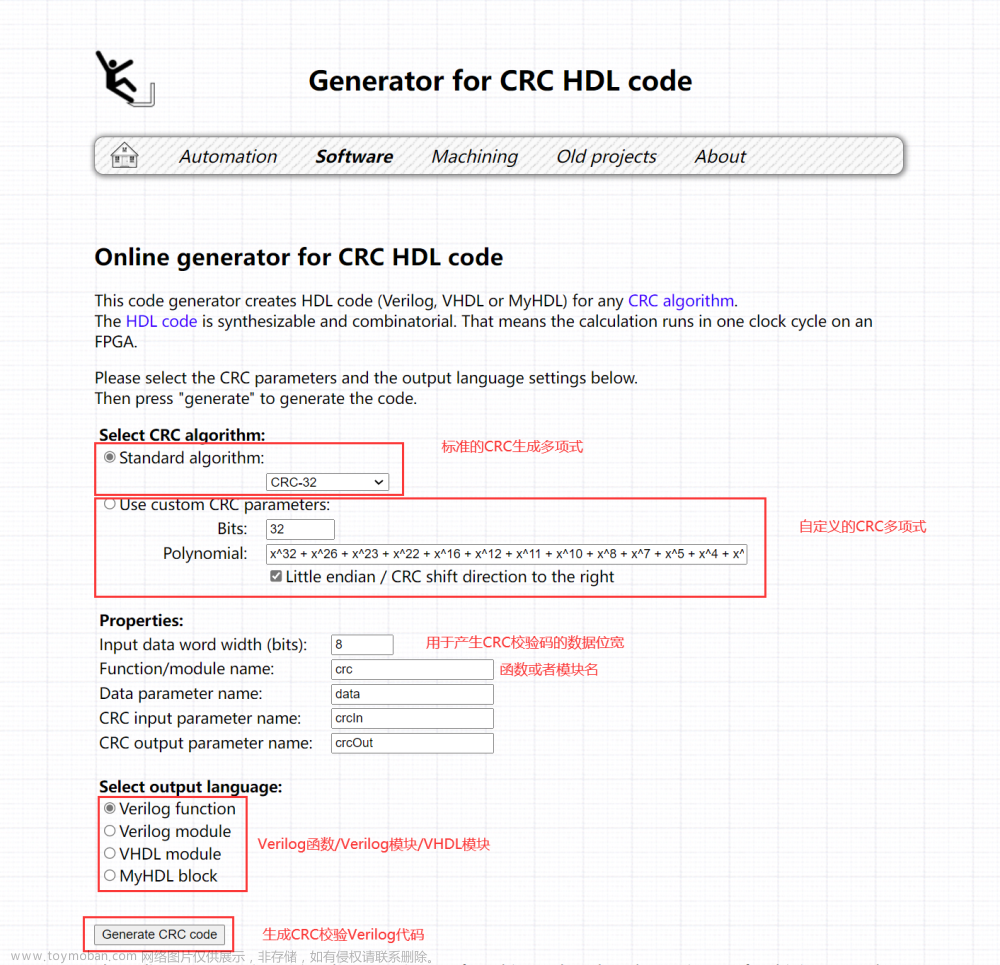

在FPGA设计的过程中,在有些场景下,我们需要用到CRC(Cyclic Redundancy Check)校验码,比如以太网报文、信道编码等。对应的,我们需要编写相应的Verilog代码用于计算对应的CRC校验码。我们可以根据CRC校验的原理自己编写一个产生CRC校验码的Verilog模块,也可以通过在线网站进

-

vcs+verdi仿真Verilog代码

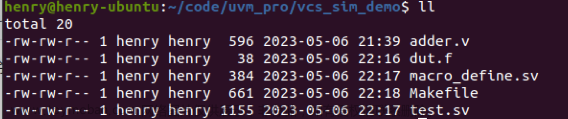

我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。 源文件内容如下: 我们再定义一个宏定义的文件: 我们需要再定义一个testbench文件: 再定义一个filelist文件: dut.f 最后就是需要一个Makefile文件了: 总的文件如下: 执行 make all : 跑完后如下

-

弹球游戏Verilog代码Quartus仿真

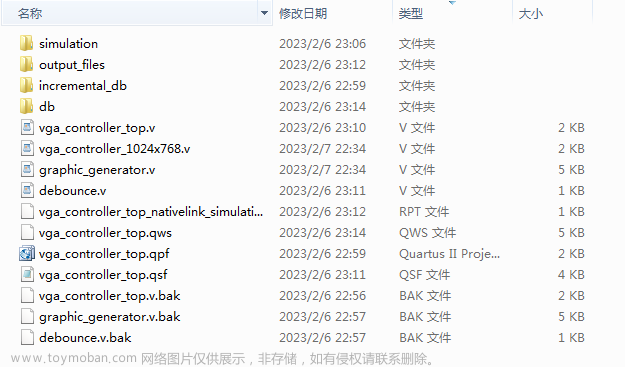

名称:弹球游戏Verilog代码Quartus仿真(文末获取) 软件:Quartus 语言:Verilog 代码功能: 设计要求 查阅FPGA、VGA接口标准等相关资料文献。 2.编写HDL代码实现νGA显示模块和按键输入模块,并下载到开发板进行测试。 3.图像分辨率不低于1024*768,目标移动方块50*50,移动弹板为20*100。

-

VSCODE-Verilog开发插件/(代码格式化+Verilog文件树显示+一键例化+UCF转XDC+代码错误检查+语法高亮)

VSCODE插件,可实现功能: 变量对齐 逗号对齐 括号对齐 快捷键:CTRL + L 例化的代码自动复制到剪切板 快捷键:ctrl+shift+p :输入 Convert_instance 正常顺序转换 可实现序号的从小到大的排列 快捷键:ctrl+shift+p :输入 Convert UCF to XDC NORMAL ORDER 或 Convert UCF to XDC SORT ORDER ucf, xdc, do, tcl 语法

-

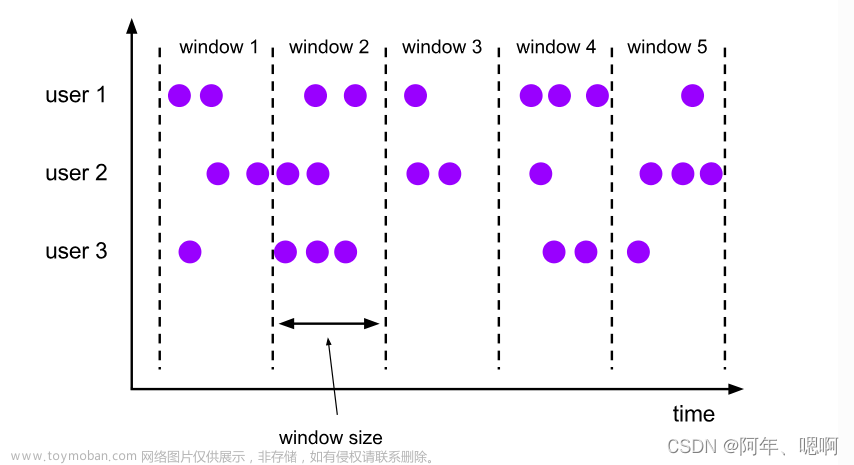

Flink窗口分类简介及示例代码

水善利万物而不争,处众人之所恶,故几于道💦 1. 流式计算 Flink作为一个流式处理引擎,被设计用来处理无限数据集,理论上来说,无限数据集是一种不断产生,源源不断的数据集,说白了就是你不知道这个数据流它啥时候结束,这就是无限数据集。 流式计算的思

-

通过代码实现窗口界面布局的方法

在QWidget窗口中添加相关事件resizeEvent()函数并编写相关功能代码: 运行效果如下:

-

Verilog手撕代码(6)分频器

分频就是生成一个新时钟,该新时钟的频率是原有时钟频率的整数分之一倍,新周期是原有周期的整数倍。 再简单来说,让你手撕一个四分频电路,就是写代码生成一个周期是原来四倍的时钟,如果手撕一个三分频电路,就是写代码生成一个周期是原来三倍的时钟。 如图为

-

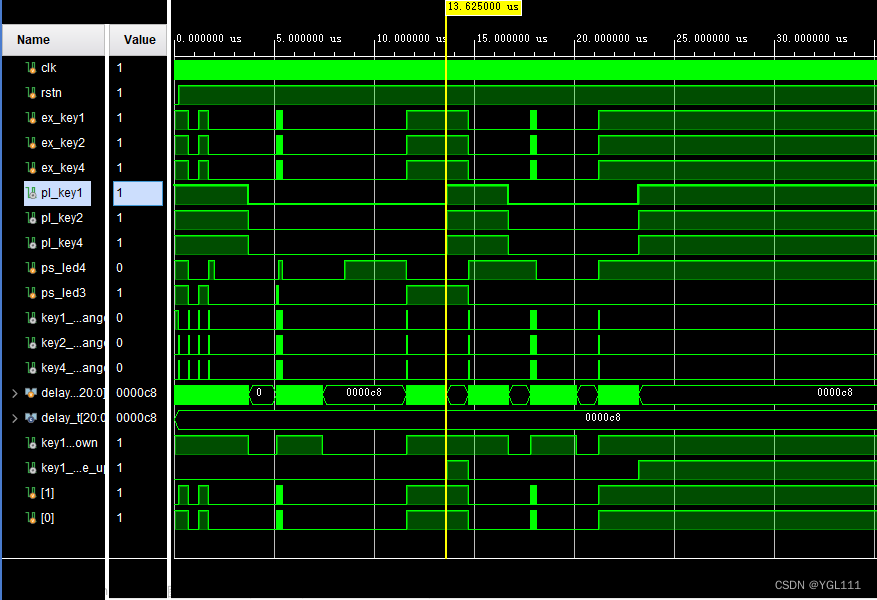

用verilog编写按键消抖代码

本代码在按键按下和松开情况下均能消抖,消抖延时20ms(时钟频率为100MHz时)。 代码如下 module key3_led2( //from system input input clk, input rstn, //from external input to pl input ex_key1, //按键从PL端输入 //from pl to ps output reg pl_key1 //处理

-

verilog中产生方波的代码

其中: 1)通过更改 square_wave_period对方波的周期进行调整 2)通过更改square_wave_amp_H对方波的高幅值进行调整 3)通过更改square_wave_amp_L对方波的低幅值进行调整

-

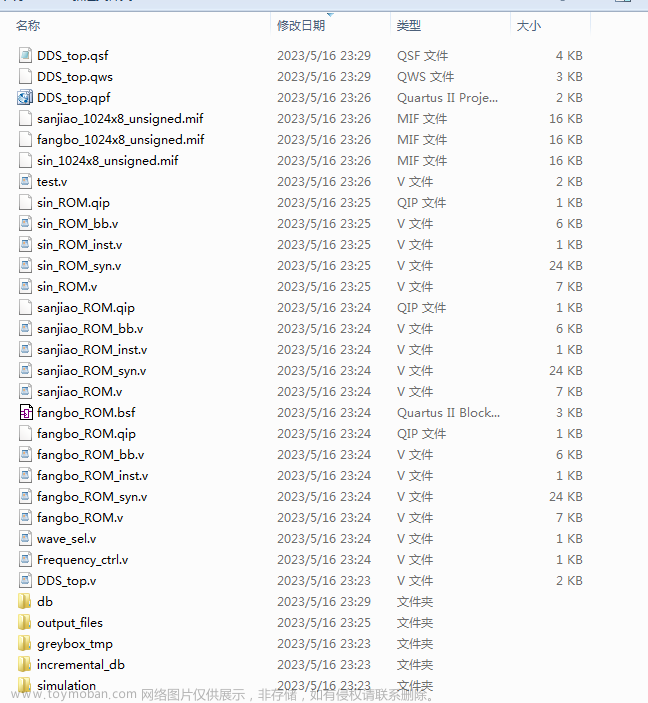

QuartusDDS信号发生器Verilog代码仿真

名称:QuartusDDS信号发生器Verilog代码仿真(文末获取) 软件:Quartus 语言:Verilog 代码功能: DDS信号发生器 可以输出正弦波、方波、三角波 可以改变波形的频率 1. 工程文件 2. 程序文件 3. 程序编译 4. RTL图 5. Testbench 6. 仿真图 整体仿真图 方波ROM模块 三角波ROM模块 Sin波ROM模块

-

python代码调出cmd命令行窗口并在cmd窗口中执行指定的命令

有时候,我们需要在python代码中打开 cmd命令行窗口,并在新打开的命令行cmd窗口中执行特定的命令, 其实,这个操作很容易,不过在网上找了一圈,都是没有说明白, 这里总结发布一下, 导入 os 模块 import os os.system( \\\' start cmd.exe /K C:\\\\Users\\\\admin\\\\AppData\\\\Roaming\\\\360se6\\\\Applicati

-

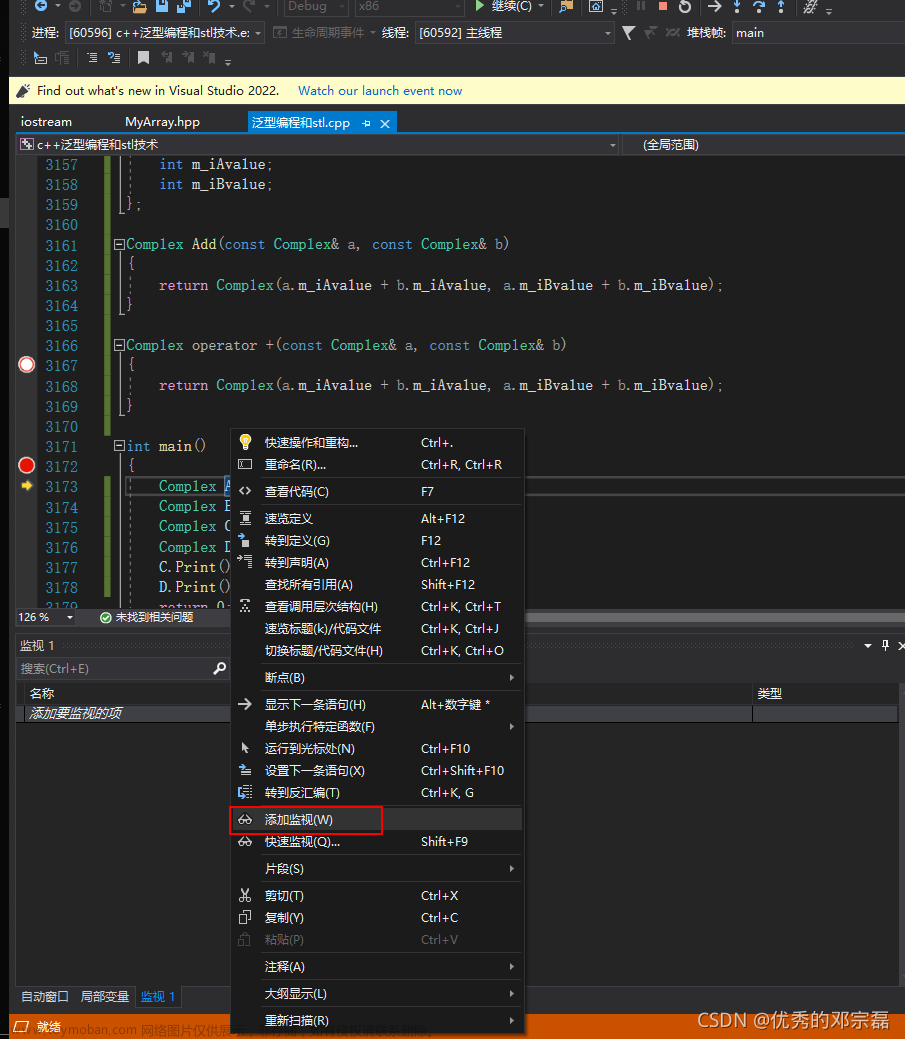

c++代码调试工具,监视/快速监视窗口:

代码调试,监视/快速监视: 程序处于调试状态时,可以使用监视(watch)窗口和快速监视(quick watch)命令执行变量值得查看、改变等操作。 快速监视: 方法: 在调试的状态下,将鼠标放在变量上,右键弹出菜单,点击“快速监视”,可以打开一个快速监视窗口,该窗口会

-

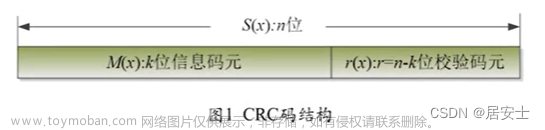

CRC校验码详解+Verilog实现(含代码)

目录 CRC码简介 CRC校验码生成步骤 CRC码生成多项式 CRC校验码Verilog实现 CRC即循环冗余校验,是一种数字通信中的常用信道编码技术。其特征是信息段和校验字段的长度可以任意选定 CRC码是由2部分组成的,前部分是信息码,后部分是校验码,如果CRC码长共 n bit,信息码长

-

Verilog手撕代码(7)数据位宽转换

数据位宽转换器,一般常用于模块接口处,比如一个电路模块的输出数据位宽大于另一个模块的输入数据位宽,此时就需要进行数据位宽转换。比如SATA控制器中,内部数据位宽为32bit,但外部物理收发器PHY的接口通常为16bit,或者8bit,在不使用FIFO进行缓存的情况下,可以使用

-

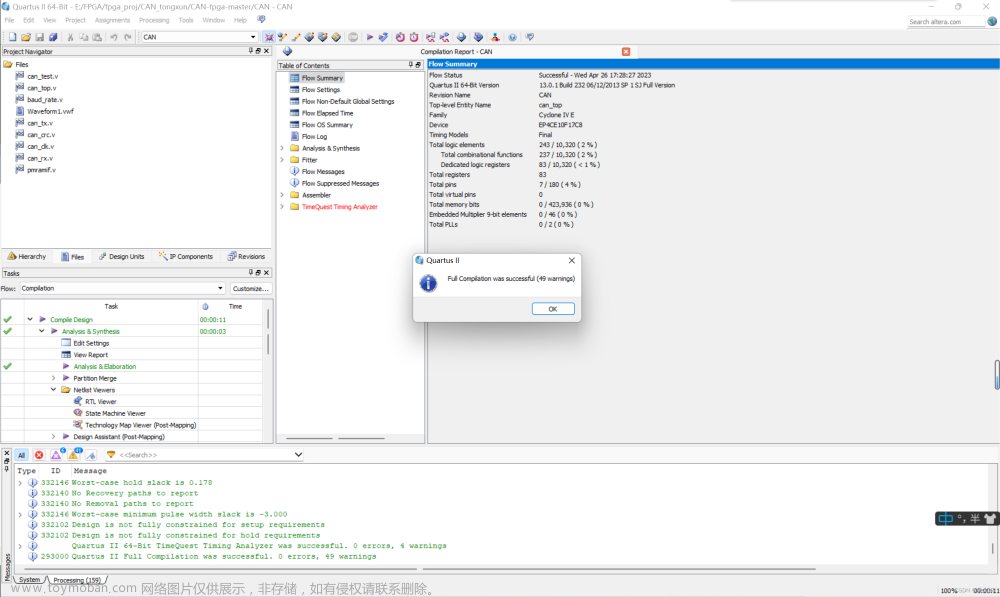

基于FPGA的CAN通讯verilog代码设计

FPAGA本篇文章参考github网站的开源项目can-FPGA-master编写改进 在调试过程中,发现该项目无法在quartus pro13.0的环境下运行通过,代码存在错误,并且对于EP4系列的芯片来说有太多的IO口,无法在烧录,所以笔者对此进行了改进。 can_top模块 can_tx传输数据模块 can_rx接收数据模块

-

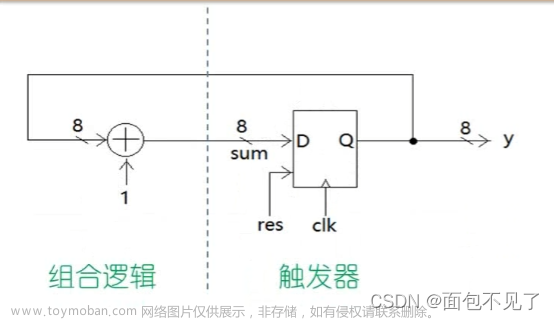

Verilog学习记录(一):时序逻辑代码设计和仿真

本次学习的内容来自B站:Verilog零基础入门 其他相关引用以贴上原链接 时序逻辑电路 一、计数器 1.原理及代码实现 2.Modelsim仿真 二、四级伪随机码发生器 1.原理及代码实现 2.Moselsim仿真 总结 时序逻辑电路是数字逻辑电路的重要组成部分,时序逻辑电路又称,主要由 存储电路

-

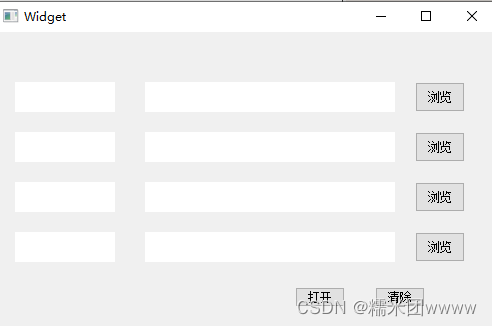

qt 窗口实现打开文件夹浏览资源(纯代码实现,后附代码)

新建 widget 项目可参考 QT入门初学者——如何新建一个工程项目(详细)_guuuuug的博客-CSDN博客_qt新建工程 实现界面,点击浏览会打开文件夹 选中文件,窗口显示文件名,文件路径 过长的文字会在最后显示...,鼠标悬浮在文字栏会显示全部文字。 点击右下角打开可以实现打

-

基2-booth乘法器原理及verilog代码

对于一个n位的有符号二进制数B,首位是0则B可以表示为: 首位是1,B[n-2:0]是实际数字的补码,所以可以得到 。 可以得到合并的公式如下所示: 将公式展开: 除了n-1项外的每一项乘2之后再减去本身: 根据2^i重构公式: 为了统一形式,添加一项B[-1],初始值为0.注意这里的B