-

STM32-ADC多通道数据采集:理论与实践

本文详细介绍了STM32-ADC多通道数据采集的理论基础和实践应用。文章首先解释了ADC的基本概念和特性,然后详细阐述了ADC采样的过程和注意事项。接着,文章深入讲解了多通道采集模式的轮询和DMA两种方法,并给出了具体的代码实现。

-

4通道高速数据采集卡推荐哪些呢

FMC141是一款基于VITA57.4标准的4通道2.8GSPS/2.5GSPS/1.6GSPS采样率16位DA播放FMC子卡,该板卡为FMC+标准,符合VITA57.4与VITA57.1规范,16通道的JESD204B接口通过FMC+连接器连接至FPGA的高速串行端口。 该板卡采用TI公司的DAC39J84芯片,该芯片是一款具有JESD204B接口的低功耗、16位4通道2.8GSPS数模

-

多通道数据采集器的FPGA实现

多通道数据采集器的FPGA实现 数据采集器是一种常见的设备,用于从多个输入源同时采集数据。在本篇文章中,我们将使用FPGA(现场可编程门阵列)来实现一个多通道数据采集器,并使用Matlab进行验证和分析。我们将介绍FPGA的基本原理以及如何使用Matlab进行仿真和验证。 F

-

数据采集专家----4通道AD采集子卡推荐

FMC136是一款4通道250MHz采样率16位AD采集FMC子卡,符合VITA57规范,可以作为一个理想的IO模块耦合至FPGA前端,4通道AD通过高带宽的FMC连接器(HPC)连接至FPGA从而大大降低了系统信号延迟。 该板卡支持板上可编程采样时钟和外部参考时钟以及采样时钟,多片板卡还可以通过触发(

-

AD7616单通道SPI模式采集数据

AD7616支持并口及SPI串行通讯,使用单片机采用单线SPI读数据时一直无法正确运行。 1.排查硬件设计,包括模式选择,复位逻辑等,没有问题。 2.用FPGA与AD7616通讯正常,排除7616自身单线模式无法工作的原因。 3.更换时序逻辑完全一致的其他芯片,如AD8686,一切正常。 使用逻辑

-

基于FPGA的多通道数据采集系统Verilog设计

基于FPGA的多通道数据采集系统Verilog设计 随着科技的不断发展,数据采集在许多领域变得越来越重要。为了满足高速、高精度和多通道数据采集的需求,基于FPGA的多通道数据采集系统成为了一种常见的解决方案。本文将介绍如何使用Verilog语言设计一个基于FPGA的多通道数据采

-

STM32-ADC多通道数据采集:理论与实践

本文详细介绍了STM32-ADC多通道数据采集的理论基础和实践应用。文章首先解释了ADC的基本概念和特性,然后详细阐述了ADC采样的过程和注意事项。接着,文章深入讲解了多通道采集模式的轮询和DMA两种方法,并给出了具体的代码实现。

-

FPGA 68013 USB2.0 多通道数据采集,工程验证过

FPGA 68013 USB2.0 多通道数据采集,工程验证过 FPGA 68013 USB2.0 多通道数据采集,工程验证过 随着科技的发展和信息技术的不断进步,数据采集技术在各个领域的应用越来越广泛,其中,多通道数据采集技术尤为重要。在这种技术领域中,FPGA 68013 USB2.0 多通道数据采集技术成为

-

基于FPGA的多通道数据采集系统Verilog设计嵌入式

基于FPGA的多通道数据采集系统Verilog设计嵌入式 在本文中,我们将介绍基于FPGA的多通道数据采集系统的Verilog设计,该系统可用于同时采集和处理多个通道的数据。我们将详细讨论系统的设计原理和实现步骤,并提供相应的Verilog源代码。 系统概述 多通道数据采集系统是一种

-

STM32-微项目10-ADC多通道采集+DMA数据转移

一、微项目实现目标: 由于ADC多通道采集在规则组中只有一个寄存器CR,实际上在多通道采集时刻,需要把每一个同都的数据及时传出,否则上一个通道的数据会被当前通道的数据给覆盖掉。 二、微项目硬件配置需求: stm32F103C8T6核心板一块 0.96寸OLED显示,用于显示计数 三

-

基于ARM+FPGA+AD的多通道精密数据采集仪方案

XM 系列具备了数据采集仪应具备的“操作简单、便于携带、满足各种测量需求”等功能的产品。具有超小、超轻量的手掌大小尺寸,支持8 种测量模块,还可进行最多576 Ch的多通道测量。另外,支持省配线系统,可大幅削减配线工时。使用时不必担心配线工时或配线错误、断

-

STM32CubeMx配置ADC(多通道采集+DMA读取数据)(HAL库开发)

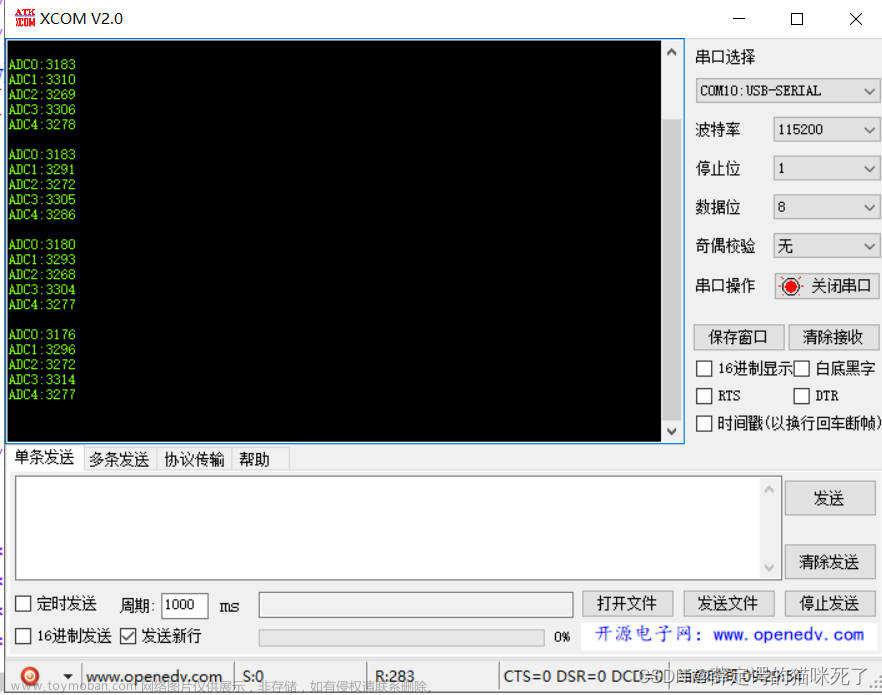

目录 1、函数配置过程(这是标准库配置过程): 2、STM32CubeMx配置过程 3、main函数源文件 采集5路ADC数据,并用串口printf()函数打印出来。 实验现象: ADC转换的初始条件: 1、使能 2、触发源条件完成(这个需要自己配置)利用:HAL_ADC_Start_DMA()函数; ADC中HAL开发优势就是,

-

【N32L40X】学习笔记11-ADC规则通道采集+dma数据传输

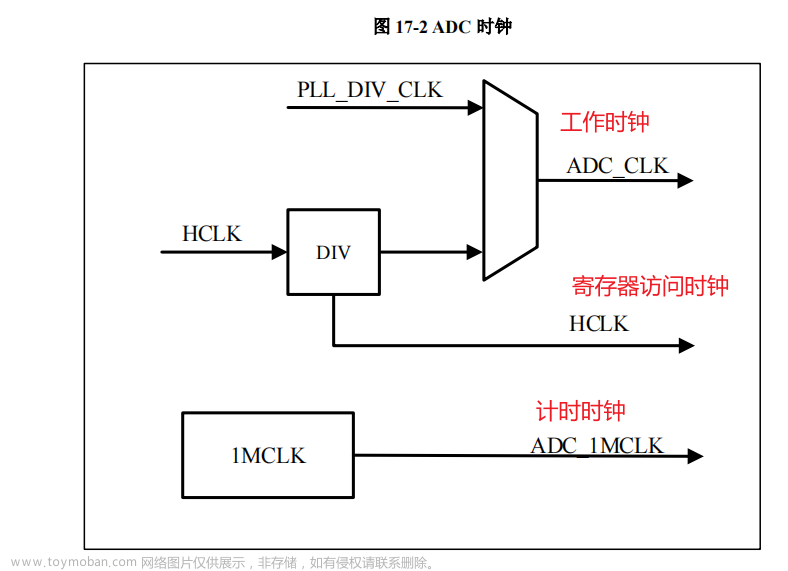

支持 1 个 ADC,支持单端输入和差分输入,最多可测量 16 个外部和 3 个内部源。 支持 12 位、10 位、8 位、6 位分辨率。 ADC 时钟源分为 工作时钟源、采样时钟源和计时时钟源 仅可配置 AHB_CLK 作为 工作时钟源 。 可配置 PLL 作为 采样时钟源 ,最高可到 64MHz,支持分频 1,2,4,6,8,

-

基于FPGA+JESD204B 时钟双通道 6.4GSPS 高速数据采集设计(三)连续多段触发存储及传输逻辑设计

本章将完成数据速率为 80MHz 、位宽为 12bits 的 80 路并行采样数据的连续多 段触发存储。首先,给出数据触发存储的整体框架及功能模块划分。然后,简介 MIG 用户接口、设置及读写时序。最后,进行数据跨时钟域模块设计,内存控制 模块设计以实现连续多段触发存储。触发

-

基于FPGA+JESD204B 时钟双通道 6.4GSPS 高速数据采集模块设计(二)研究 JESD204B 链路建立与同步的过程

基于 JESD204B 的采集与数据接收电路设计 本章将围绕基于 JESD204B 高速数据传输接口的双通道高速数据采集实现展 开。首先,简介 JESD204B 协议、接口结构。然后,研究 JESD204B 链路建立与同 步的过程。其次,研究基于 JESD204B 子类 1 的多器件同步方案。最后,将完成 双通道同步