-

Java中StopWatch秒表的用法详解 | 自定义和Apache Commons实现

本文详细探讨了如何在Java中创建和使用StopWatch秒表,介绍了自定义实现和Apache Commons库提供的实现。

-

vivado数字秒表verilog代码ego1开发板电子秒表跑表

名称:vivado数字秒表verilog代码ego1开发板电子秒表跑表 软件:VIVADO 语言:Verilog 代码功能: 数字秒表设计 1、秒表的设计精确到10毫秒(0.01秒) 2、可通过按键控制秒表启动、暂停、复位 3、数码管显示分、秒、毫秒 本代码已在ego1开发板验证,开发板如下,其他开发板可以修

-

基于Multisim仿真数字秒表

目录 一、设计要求 二、仪器选用 三、电路实现 1.实现计时范围00.00—99.99s 2.实现清零功能 3.实现校停功能 四、电路仿真 1.计时范围00.00—99.99s; 2.具有清零,校停功能; 1.计数器:选用具有清零,保持功能的计数器即可 这里使用的是74LS160十进制计数器,功能表如下: 2.显示

-

FPGA巩固基础:秒表的设计

6位8段数码管,低三位显示毫秒计数,最高位显示分钟,其余两位显示秒计数。 开始案件与暂停按键,复位按键直接全部归零。 扩展部分:每计满一次,led移位一次。 首先按键信号经过消抖再用,然后把产生的标志信号传给控制模块,由于控制逻辑很简单就把这部分控制

-

Verilog秒表计时器设计

Verilog秒表计时器设计 设计一个基于Verilog的秒表计时器,该计时器可以在嵌入式系统中使用。下面是详细的设计说明和相应的源代码。 设计说明: 秒表计时器是一种常见的计时工具,可以用于测量时间间隔。在嵌入式系统中,我们可以使用Verilog语言来实现一个简单的秒表计

-

Verilog设计倒计时秒表

目录 一.设计要求 二.模块总和 三.模块设计 1.顶层模块 2.分频模块 3.计数模块 4.倒计时模块 5.数码显示模块 6.管脚约束代码 四.引脚分配 五.演示视频 ①.用基于NEXY4 DDR开发板自带的时钟驱动电路,要求计时精确; ②.用开发板上的低 7 个开

-

基于VHDL语言的计时秒表设计

设计一个带有开始与暂停的计时秒表,秒表的最低位是0.1秒,显示格式为0.00.00.0;带有复位开关。 步骤一:设计分析 1.系统底层设计模块分析 根据系统的设计要求,系统的底层设计主要由分频器模块、十进制计数器模块、六十进制计数器模块、多位数码管显示模块组成。 2.输

-

基于51单片机的自制秒表

基于LCD1602显示屏的自制秒表,可完成计时,暂停,继续,清零功能 1.1、实现功能 输入参数为延时时间长度,单位为毫秒,用于短暂延时 1.2、设计原理 从STC-ISP 中生成的延时1ms的代码修改得到的延时任意时间的函数 1.3、代码实现 2.1、实现功能 检测四个独立按键

-

基于FPGA的数字秒表设计(完整工程)

目录 概述 设计功能 数字秒表设计的目的 模块仿真 设计代码 概述 该设计是用于体育比赛的数字秒表,基于FPGA在Quartus II 9.0sp2软件下应用VHDL语言编写程序,采用ALTRA公司CycloneII系列的EP2C8Q208芯片进行了计算机仿真,并给出了相应的仿真结果。本设计有效的克服了传统的数字秒表

-

单片机C51计时器秒表

鱼弦:CSDN内容合伙人、CSDN新星导师、全栈领域创作新星创作者 、51CTO(Top红人+专家博主) 、github开源爱好者(go-zero源码二次开发、游戏后端架构 https://github.com/Peakchen) 单片机C51(或称8051)计时器秒表的实现原理如下: 原理解释: C51微控制器通常包括多个计时器/计数器,可

-

FPGA学习—通过数码管实现电子秒表模拟

请参阅博主以前写过的一篇电子时钟模拟,在此不再赘述。 https://blog.csdn.net/qq_54347584/article/details/130402287 项目说明:本次项目是为了通过数码管实现秒表模拟。其中,六位数码管分别显示秒表的分位,秒位,毫秒位(由于毫秒有三位,在此只取百位和十位),其中分位和秒位

-

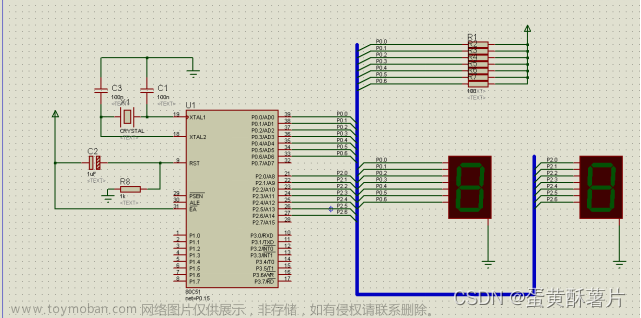

单片机原理及应用 实验五 电子秒表显示器

单片机原理及应用(C51版) 功能: 绘制实验电路原理图,程序开始时显示“00”;当1s产生时,秒计数加1;秒表显示器计数到59后,自动从“00”开始。 目的:掌握定时/计数器的中断法工作原理,熟悉C51编程与调试方法。 步骤: 1.根据实验要求绘制所需电路原理图,如下图所

-

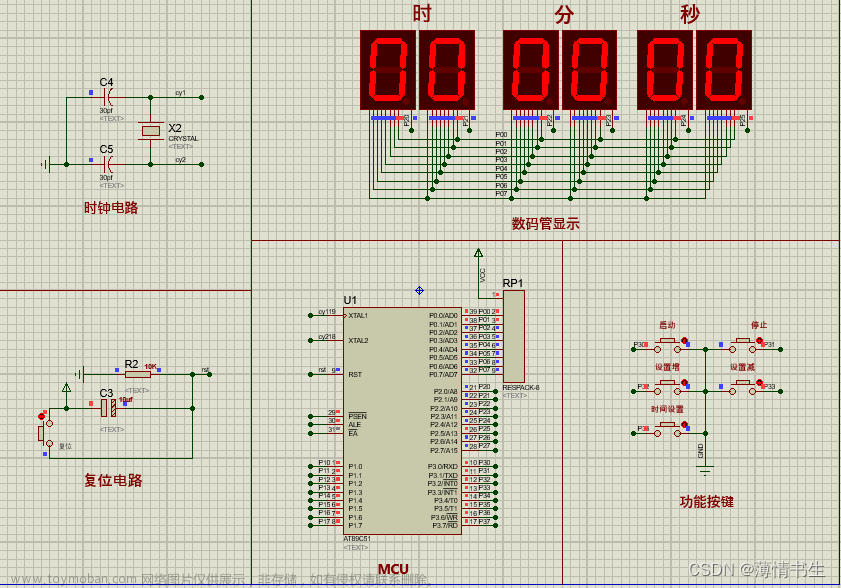

基于51单片机的倒计时秒表proteus仿真设计

目录 一、设计背景 二、实现功能 三、仿真演示 四、源程序 近年来随着科技的飞速发展,单片机的应用正在不断的走向深入。本文阐述了基于单片机的数字电子秒表倒计时设计,倒计时精度达0.05s了,解决了传统的由于倒计时精度不够造成的误差和不公平性,是各种

-

51单片机——秒表(定时器扫描独立按键和数码管)

这次实验主要是用定时器来定时扫描独立按键和数码管,代替两个模块函数中的延时函数。用定时器定时扫描的好处就是,主函数中的延时并不会影响按键的检测和数码管的扫描,只会影响响应速度。因为定时器是溢出就会执行中断程序,是定时的扫描。 改进的