软件基于 quartusII 13.1版本,开发板基于Intel DE2-115。

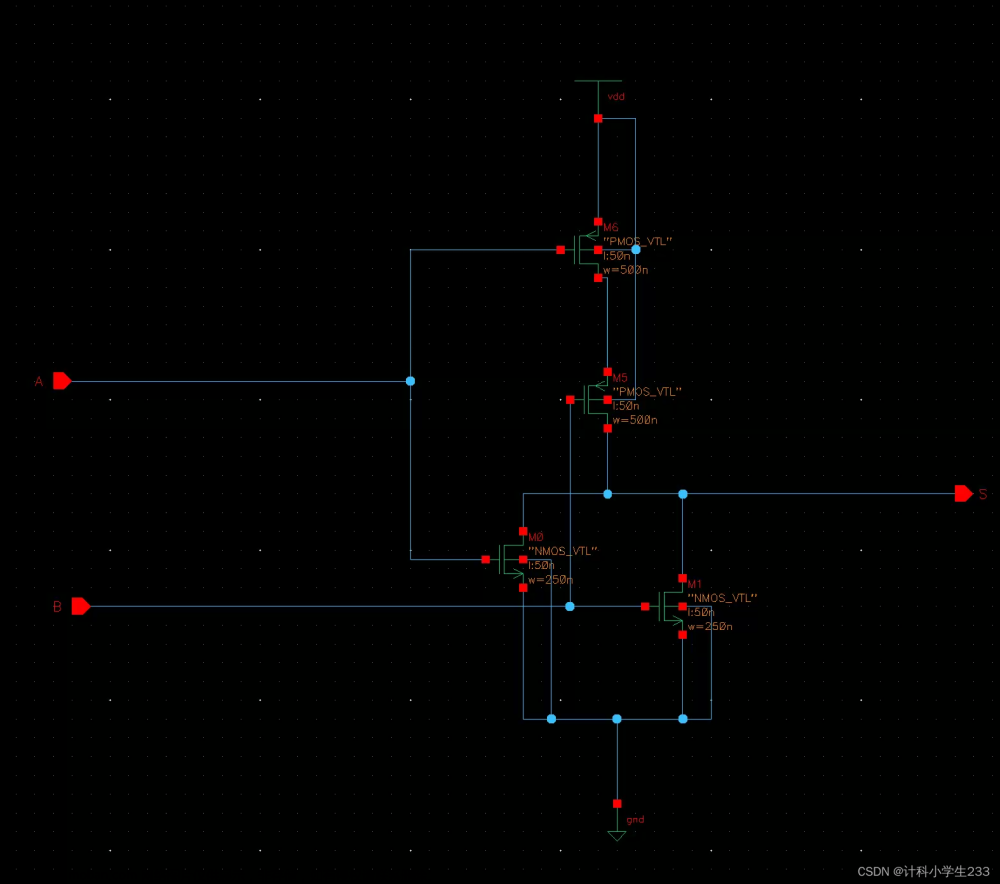

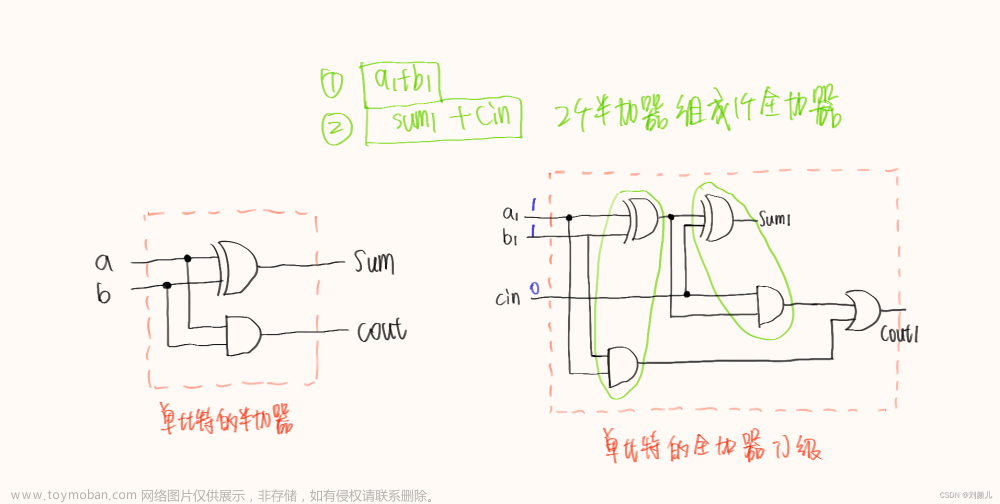

一、新建工程设计半加器

1.新建并命名工程

2.选择芯片型号

3.新建半加器原理图

文章来源:https://www.toymoban.com/news/detail-400119.html

文章来源:https://www.toymoban.com/news/detail-400119.html

文章来源地址https://www.toymoban.com/news/detail-400119.html

文章来源地址https://www.toymoban.com/news/detail-400119.html

到了这里,关于Quartus-II利用两个半加器实现简单全加器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!