最近遇到一个问题,直接往FPGA里烧写bit文件有时候能成功,有时候不能成功。假如先往PROM里写程序,不断电,再通过JTAG往FPGA里写程序,就一定烧不进去。

直接上结论:

在Generate Programming File的选项里把Enable Internal Done Pipe的选项勾选上,或许问题就可以解决了。

原理

FPGA 的配置寄存器中有一个叫COR寄存器(配置选项寄存器)。这个寄存器的第25位是DONE_PIPE。VIRTEX II 系列的手册里对这一位的描述是这样的:

Add a pipeline stage for the DONEIN signal. The DONEIN signal reflects the logic level on the DONE pin, not whether the device has released the DONE pin. This pipeline stage can be useful if the rise time on the DONE pin is slow, which could otherwise cause configuration to fail.

翻译过来是

为DONEIN信号添加管道级。DONEIN信号反映的是DONE引脚上的逻辑电平,而不是设备是否释放了DONE引脚。如果DONE引脚上的上升时间很慢,则此管道阶段非常有用,否则可能导致配置失败。

关于这些寄存器的说明可以看英文原版手册或者我复制粘贴的一篇VIRTEX II系列FPGA手册的翻译。

VIRTEX II 系列FPGA的配置部分文档的翻译阅读参考

ISE的默认选项里是不选中这个DONE_PIPE的(或者至少我用的10.1版本是这样的)。

问题的发现

发现问题的方法说简单很简单,说复杂很复杂。

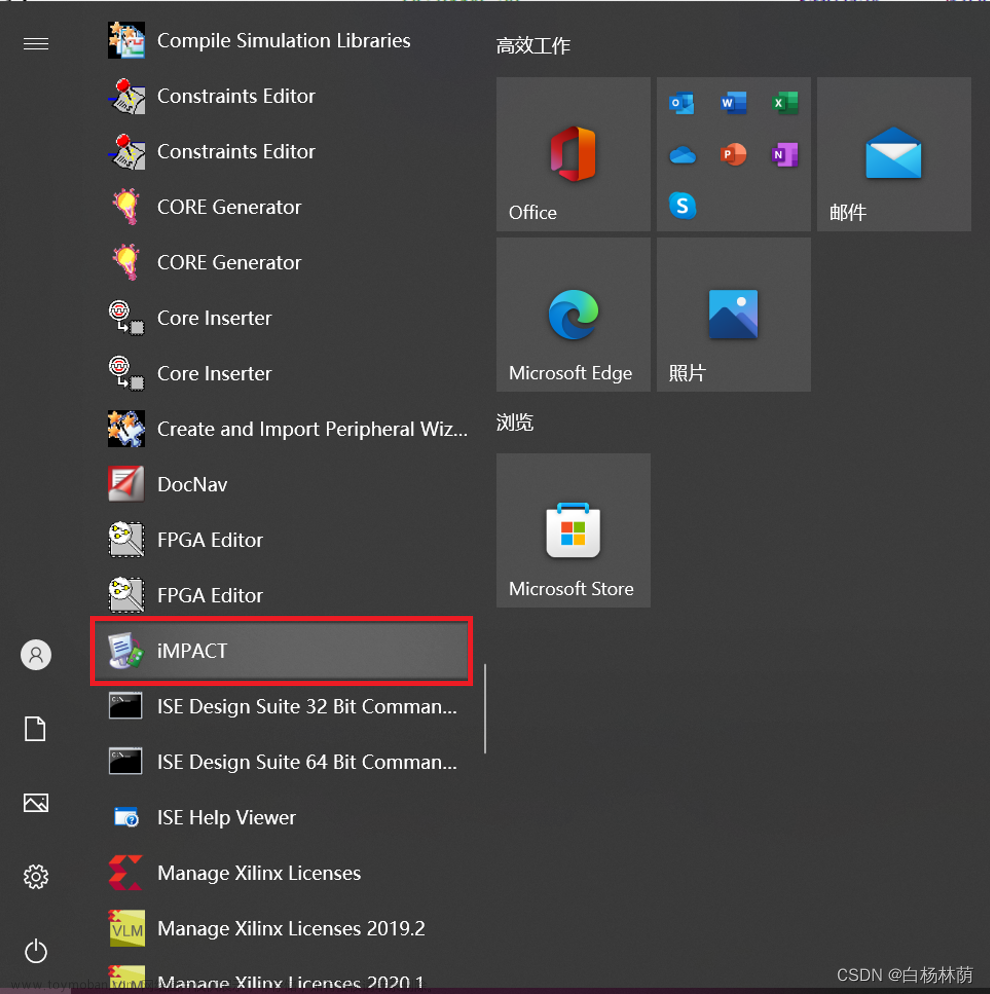

用逻辑分析仪抓JTAG下载信号,把数据存下来然后自己在EXCEL里写公式,把JTAG状态机和FPGA里的一些寄存器解析出来。

在EXCEL里发现我在CFG_IN指令下发送的数据是这样的:

文章来源:https://www.toymoban.com/news/detail-400822.html

文章来源:https://www.toymoban.com/news/detail-400822.html

0xAA995566是同步字

0x30012001选中的是COR寄存器

0xA0BF3D是往寄存器中写入的内容

很明显第25位写入的是0,也就是DONE_PIPE没有选中

当我尝试着在生成选项里勾选DONG_PIPE之后,下载就成功了。文章来源地址https://www.toymoban.com/news/detail-400822.html

到了这里,关于FPGA直接烧写.bit文件失败但是可以通过PROM配置的情况的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!