1、下列对异步信号进行同步的描述错误的是(C)。

A、采用保持寄存器加握手信号的方法寄存器

B、特殊的具体应用电路结构,根据应用的不同而不同

C、使用锁存器

D、异步FIFO

解析:

异步信号进行同步的方法:

1.具体电路,采用两级触发器,减少可能出现的亚稳态影响;

2.异步FIFO和DPRAM;

3.握手协议,有效使能后,确认。

2、FPGA的可编程是主要基于什么结构(A)。

A、查找表(LUT)

B、ROM可编程

C、PAL可编程

D、与或阵列可编程

解析:

FPGA: Field Programmable Gate Array现场可编程逻辑门阵列,基于LUT结构。

3、对时钟约束" create_clock -name clk100 -period 10 -waveform {0.00 5.00}[get_portsClkIn] "的表述不正确的是(B)。

A、周期为10ns

B、0到5ns期间为不定态

C、占空比为50%

D、时钟信号名称为"clk100"

解析:

翻译一下这个约束的意思是:创建一个时钟,名字叫clk100,周期为10ns,脉冲波形格式为5ns的时候跳变,实际时钟信号为ClkIn。

4、下列哪些语句不可以被综合成电路(A)。

A、initial

B、always

C、assign

D、for

解析:

综合说明编的代码可以对应出具体的电路,不可综合说明没有对应的电路结构。不可综合的代码编译通过,只能看到输出,不能实现电路,

1)所有综合工具都支持的结构: always,assign,begin,end,case,wire,ti,aupplO,supply1, reg, integer,default,for,function,and,nand,xor,xnor,buf,not, bufifo,buff1,notif0,notf1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parametera

2)所有综合工具都不支持的结构: time,defparam,$finish,fork,join,initial,delays,UDP,wait。

3)有些工具支持有些工具不支持的结构: casex, casez, wand,triand,wor, trior,real,disable,forever,arrays,memories, repeat,task,while。

5、片上可编程器件的英文缩写是(B)。

A、SOP

B、SOPC

C、SoC

D、SPI

解析:System On a Progammable Chip

6、下列关于同步和异步复位描述正确的是(C)。

A、同步复位是不受时钟影响

B、使用FPGA设计时芯片的异步复位和同步复位可随意替换使用

C、同步复位需要在时钟沿来临的时候才会对整个系统进行复位

D、同步复位最大的优点是,数据通路可以不依赖于时钟而复位可用

解析:

同步复位:复位信号和时钟同步,当时钟上升沿检测到复位信号,执行复位操作。

异步复位:不受时钟影响,只要复位信号有效,就会进行复位。

7、一个四位十六个状态的格雷码计数器,起始值为1001,经过100个时钟脉冲作用之后的值为(B)。

A、0101

B、0011

C、0110

D、0000

解析:

计算公式:b[n-1]=g[n-1], b[i]=gray[i]^b[i+1](i=[0,1.....n-2])

8、下列关于亚稳态描述错误的是(D)。文章来源:https://www.toymoban.com/news/detail-401568.html

A、电路处于中间状态的时间变长,使得电路"反应"迟钝的现象,叫做亚稳态

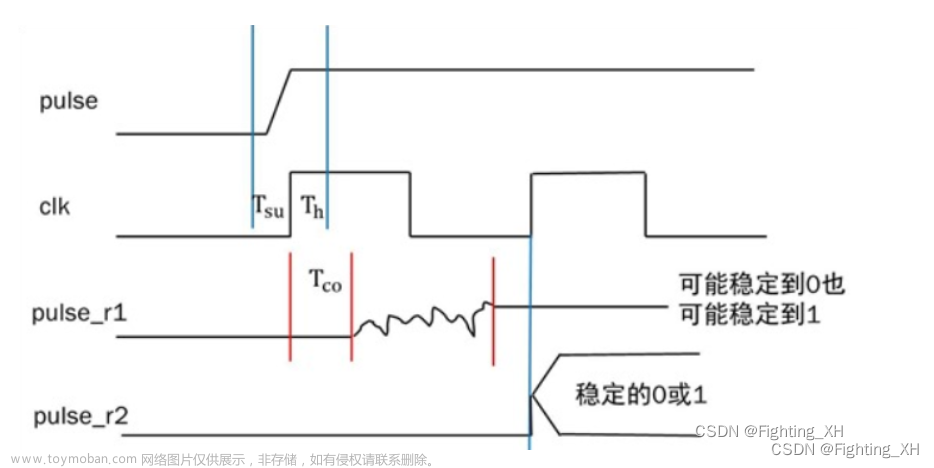

B、对于单比特控制信号采用二级触发器缓冲,可以几乎消除亚稳态

C、对于多比特数据可以采用握手的方式来消除亚稳态

D、异步FIFO不能用于解决亚稳态问题文章来源地址https://www.toymoban.com/news/detail-401568.html

到了这里,关于FPGA试题一(答案及解析)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!