FPGA教程目录

MATLAB教程目录

目录

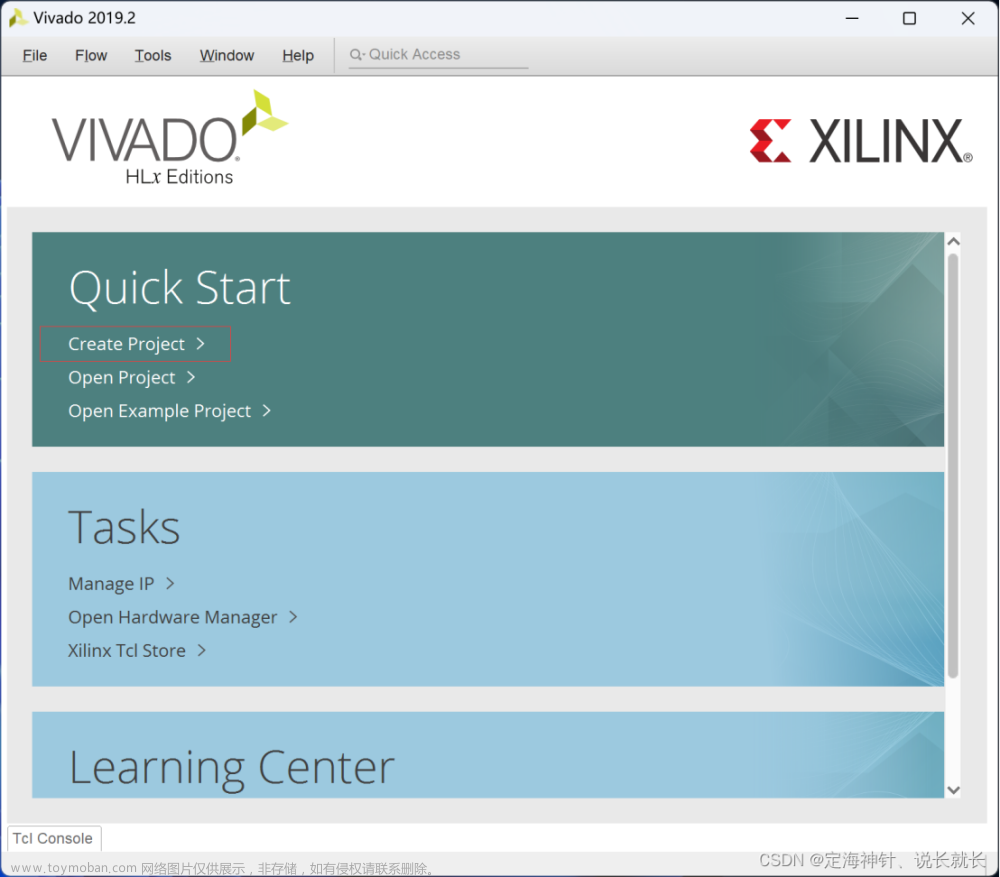

1.软件版本

2.RS编译码原理概述

2.1 RS编码原理文章来源:https://www.toymoban.com/news/detail-401969.html

2.2 R文章来源地址https://www.toymoban.com/news/detail-401969.html

到了这里,关于【FPGA教程案例89】编译码2——使用vivado核实现RS信道编译码的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!