欢迎大家学习郑州大学慕课计算机组成原理课程\doge

存储器概念

- 存储器是计算机系统中的记忆设备

- 用来存放程序和数据

- 存储器的性能已成为计算机系统的核心

存储器构成

存储介质

主要采用半导体器件和磁性材料

存储位元

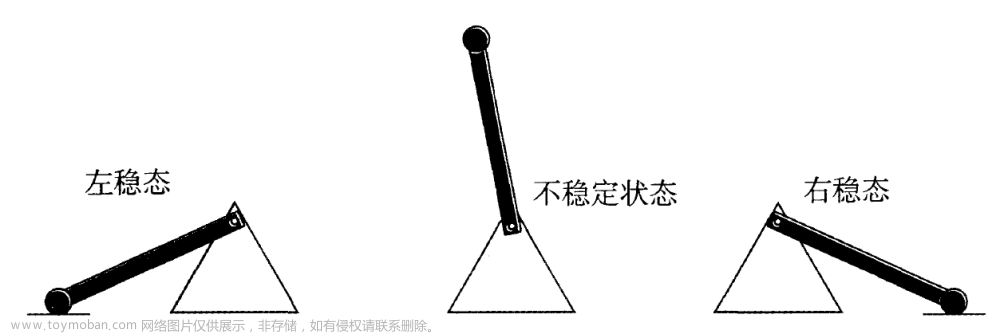

存储一位二进制代码,是存储器中最小的存储单元,一个双稳态半导体电路或一个CMOS晶体管或磁性材料都可以构成一个存储位位元

存储单元

由若干个存储位元组成一个存储单元

存储器

由许多存储单元组成一个存储器

存储单元的编制

- 字存储单元

存放一个机器字的存储单元,相应单元地址称为字地址

- 字节存储单元

存放一个字节的单元,相应的地址称为字节地址

- 按字编址的计算机

计算机可编址的最小单位是字存储单元

- 按字节编址的计算机

计算机可编址的最小单元是字节单元

一个机器字可以包含数个字节,一个字存储单元可以占用多个字节单元

存储器的分类-1

半导体存储器:

采用超大规模集成电路工艺制成芯片

- 体积小

- 功耗低

- 存储时间短

- 断电后信息丢失

磁表面存储器:

在金属或塑料基体的表面涂上一层磁性材料作为记录介质

磁芯存储器:

由硬磁性材料做成环状元件,在磁芯中穿有驱动线和读出线

- 信息可长期保存

- 不会轻易丢失

光记录存储器:

用激光在记录介质上进行读写的存储器

- 可长期保存信息

存储器的分类-2

随机存储器:

任何一个单元都可以随机的存取,且存储时间与存储单元的物理位置无关,即对存储器中的任意一个单元的写入和读出的时间是一样的

顺序存储器:

存储器只能按照某种顺序来存取,即存储时间的长短与信息在存储体上的位置有关

- 磁带

半顺序/直接 存储器:

对存储器的访问介于以上两者之间,既不能随机的访问任何一个存储单元,也不是完全的按照顺序存取

- 磁盘

存储器分类-3

RAM:

存储器工作过程中既可以读出也可以写入

用来存放当前运行的程序和数据,并可在程序运行过程中反复更改其内容

ROM:

只可以读出不能够写入

常用来存放不变或基本不变的程序和数据(如监控程序、引导和加载程序等)

存储器分类-4

易失性存储器:

断电后信息消失的存储器

非易失性存储器:

断电后仍能够保存信息

存储器分类-5

主存的分类

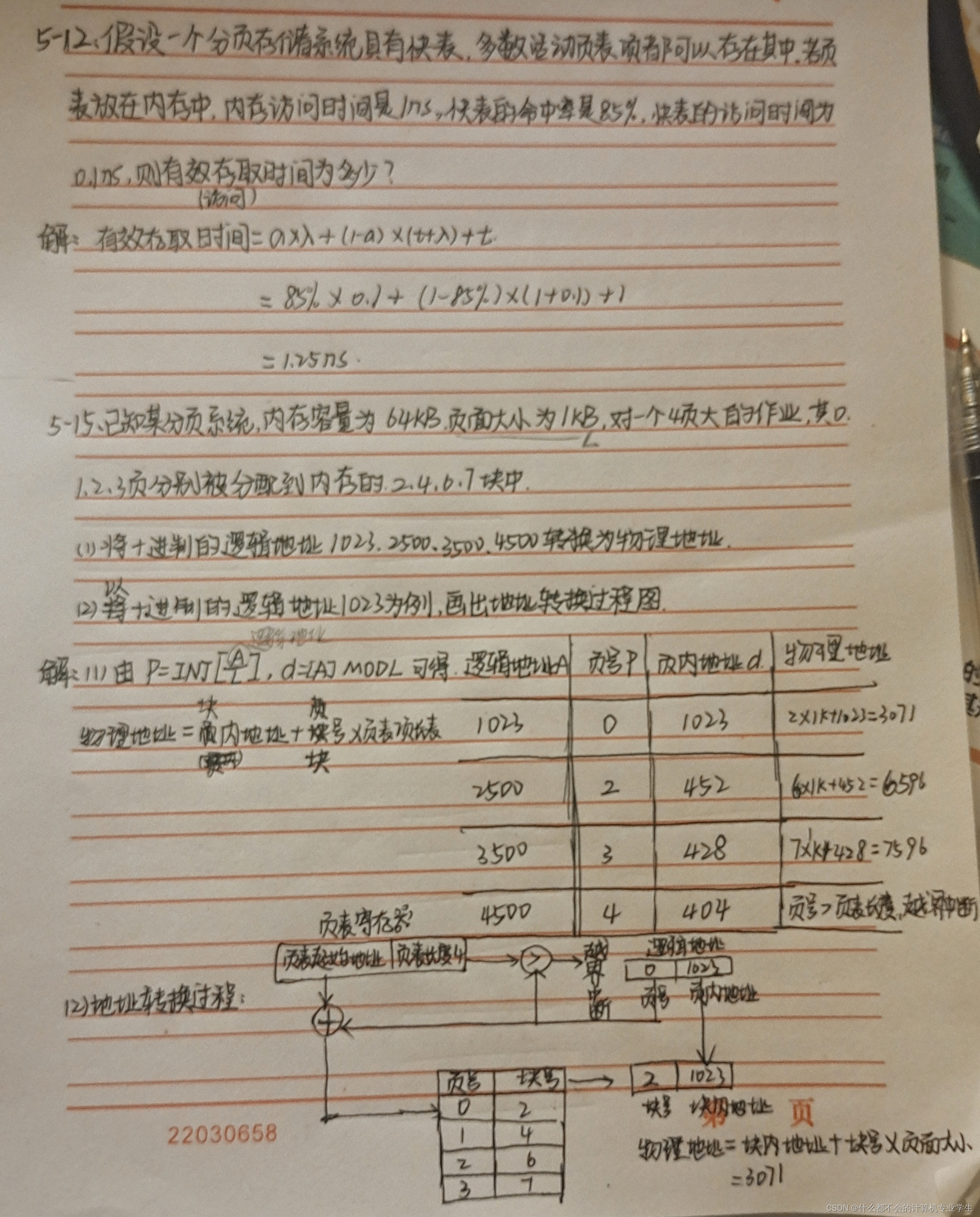

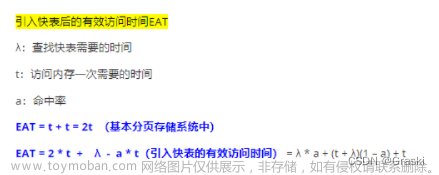

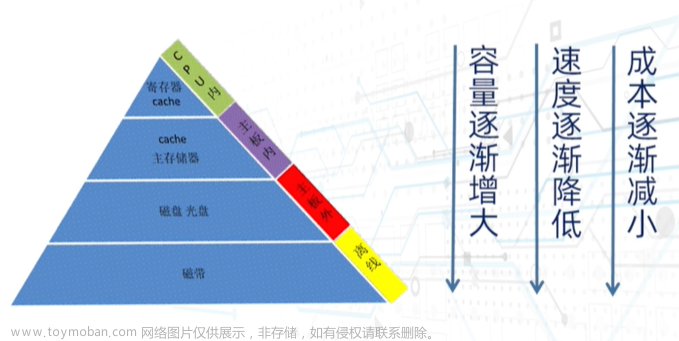

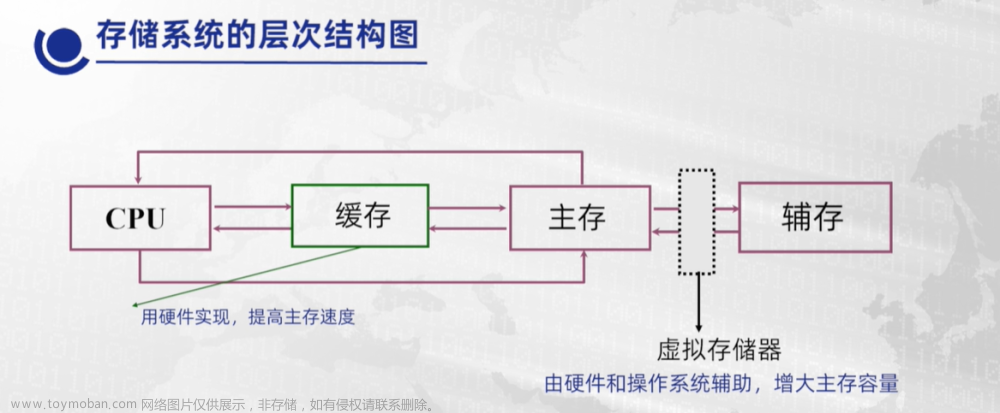

存储系统的层次结构

衡量存储器性能的指标:

- 速度

- 容量

- 每位价格

由于容量大导致速度低,速度高导致每位价格高的冲突,在一种存储器中兼顾三方是困难的,因此构建多级的存储系统解决三者的矛盾问题

程序的局部性原理

程序和数据一般都连续性存储,CPU访问存储器时,无论是读取指令还是存取数据,在一个较短的时间间隔内,所访问的存储的单元都趋向于一个较小的连续区域中

即在某一段时间内,系统会频繁的访问某一局部的存储器地址空间,而对范围以外的地址空间很少访问

- 时间局部性

最近被访问的信息很可能还要被访问

- 空间局部性

最近被访问的临近地址的信息也可能被访问

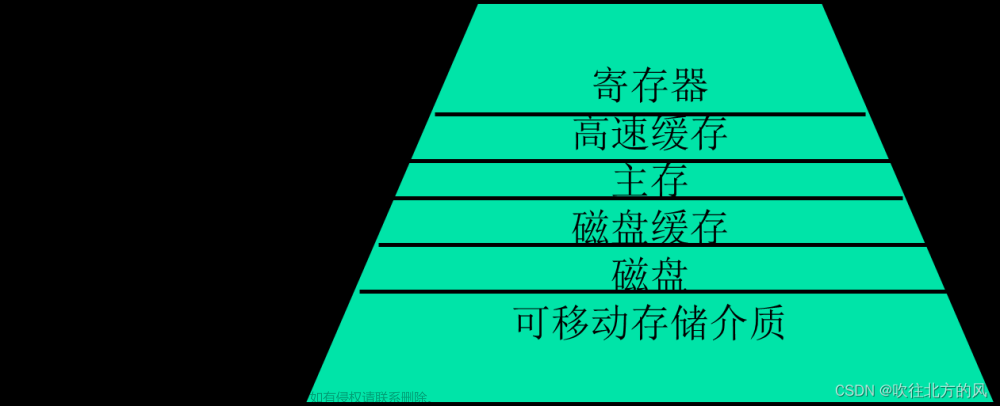

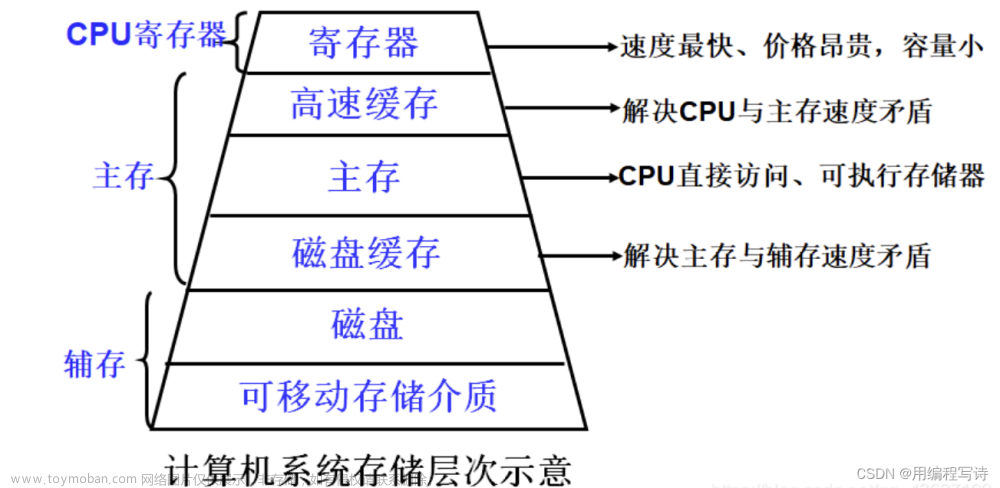

上图是多级存储系统的金字塔结构图

缓存主存层次主要解决CPU和主存层次速度不匹配的问题,在主存和缓存之间增加辅助硬件,将CPU近期要用的数据调入缓存,由于缓存容量小,需要不断地将主存的内容调入缓存,从CPU看,速度接近缓存的的速度,容量是主存的容量,每位价格接近于主存的价格,由于缓存和主存之间的数据调动都是由硬件自动完成的,他对系统程序员和应用程序员都是透明的

主存辅存层次主要解决系统的容量问题,辅存不能直接和CPU交换信息,但他的容量比主存大很多,并且具有非易失性,可以长期存储暂时不需要的信息,当CPU需要这些信息时,再将这些信息调入主存,主存和辅存之间的数据调用是操作系统系统和硬件之间共同完成的,主存和辅存之间的不断发展逐渐形成了虚拟存储器

存储器的主要技术指标

| 指标 | 含义 | 单位 |

|---|---|---|

| 存储容量 | 在一个存储器中可以容纳的存储单元总数 | 字或者字节数B、K、M、G、T |

| 存取时间 | 从接收到读写命令开始到信息被读出或者写入完成所需的时间 | ns |

| 存取周期 | 连续两次访问存储器的最小时间间隔 | ns(通常要比存取时间长) |

| 存储器带宽 | 单位时间内存储器所存取的信息量 | 位/秒 字节/秒 |

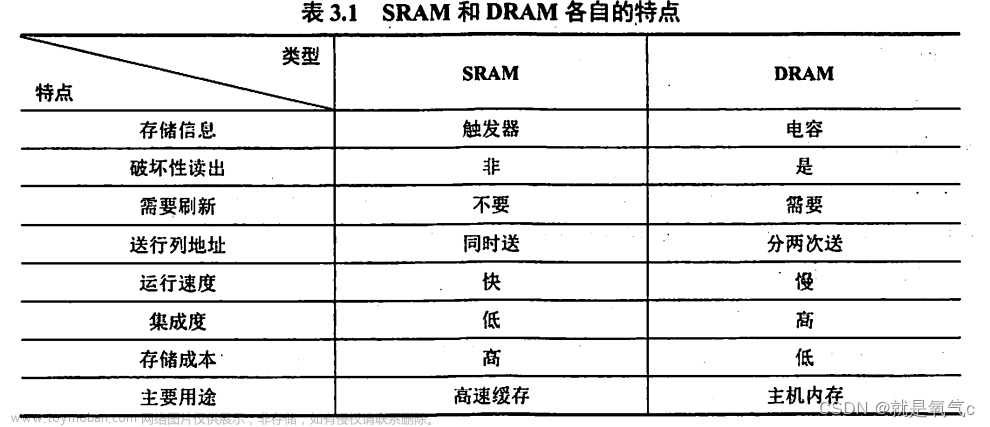

静态RAM存储器

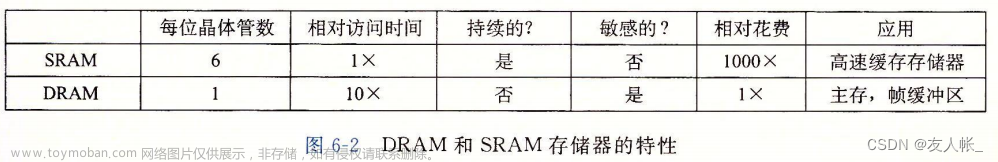

目前流行的主存是半导体存储器,按照制作工艺可以将其分为以下两种:

- 双极性

速度快,集成度低、功耗大、价格高

主要用于高速缓存

- MOS型

集成度高、功耗低、价格便宜、速度较慢

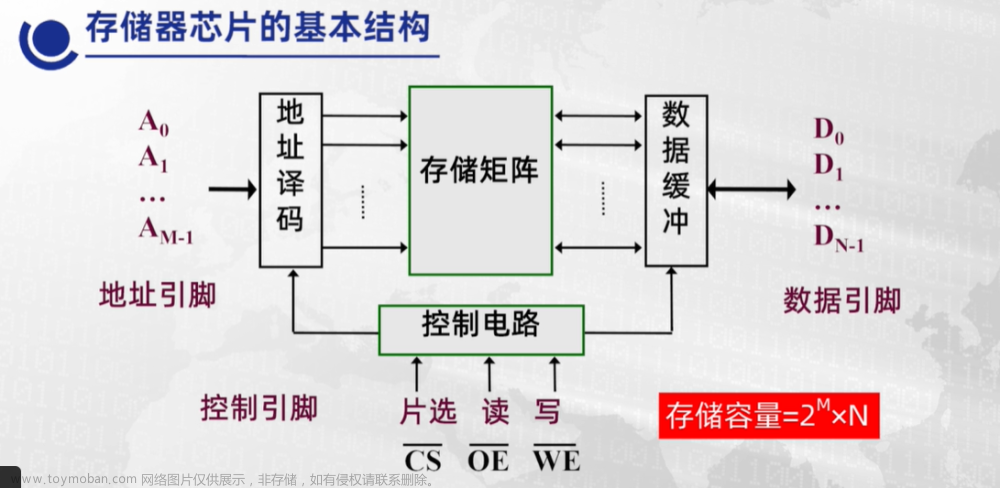

存储器芯片基本结构

存储容量等于存储单元的个数乘以单个存储单元的存储位数即

KaTeX parse error: Undefined control sequence: \cross at position 10: 存储容量=2^M\̲c̲r̲o̲s̲s̲ ̲N

M表示有M个地址引脚数,N表示有N个数据引脚数

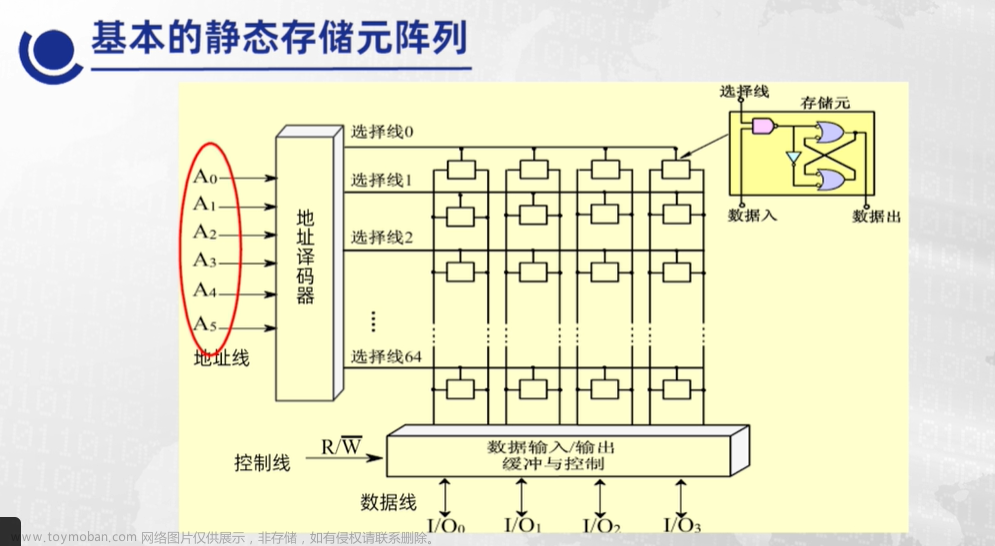

基本的静态存储元阵列

图中有六条地址线,四条数据线,表示每个存储单元存储四位数据,控制线控制写入读出,高电平表示Read读出、低电平Write写入有效

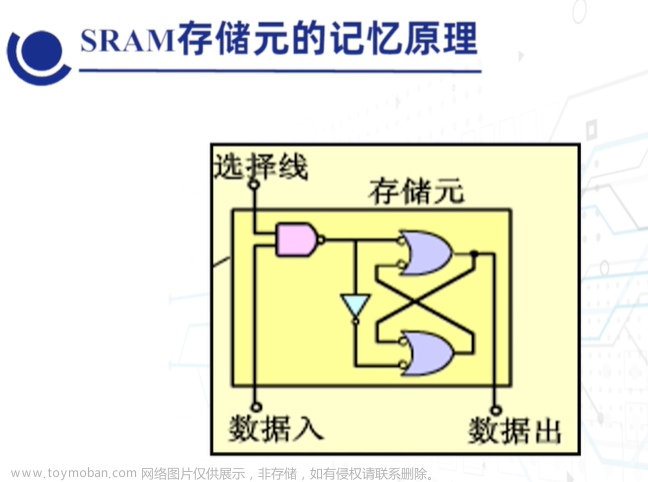

静态RAM存储器的存储元是用锁存器或者触发器电路来记忆数据的,通常一个SRAM存储元由六个MOS管组成,其中两个工作管交叉耦合构成一个双稳态触发器

选择线打开对应的与非门,然后由数据选择先控制写入的信号,为1则为1,为0则为0,下面的非或门起到巩固上面非或门输出的作用

因此只要不断电存储的信息就非常稳定,断电就会丢失

存储芯片内地址译码的方法

单译码方式

一根字选择线直接选中一个存储单元的各位,只用于一个地址译码器

优点是结构简单、速度快、适用于小容量

缺点是外围电路多、成本昂贵、结构不合理

双译码方式

将地址分为X向和Y向两部分、二级译码

- 第一级进行X向行译码和Y向列译码的独立译码

- 在存储元阵列中完成第二级的交叉译码

X和Y向两个译码器适用于大容量存储器

二者对比

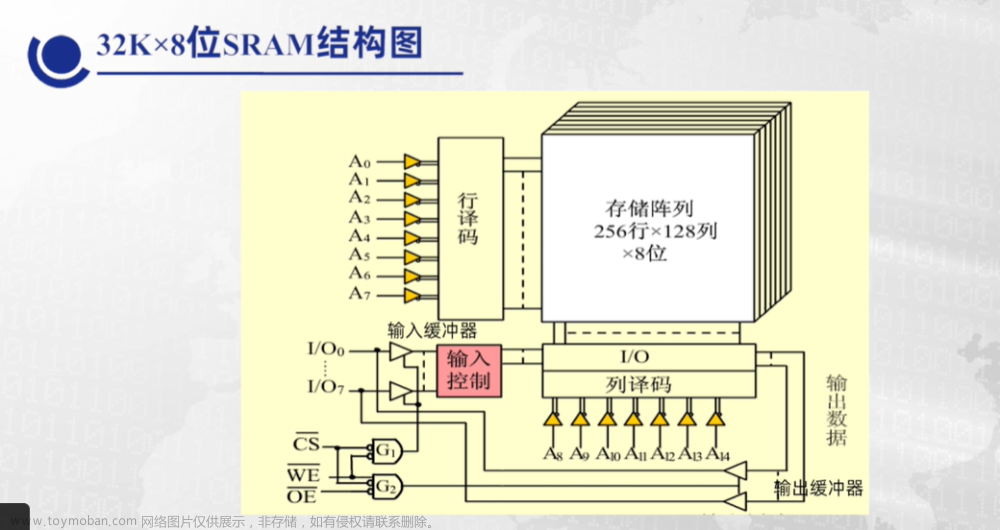

假设一个32K*8的存储元矩阵,由于32K= 2 15 2^{15} 215,因此需要十五位地址线,如果采用单译码方式,就需要 2 15 2^{15} 215根地址译码输出线来选择这么多的存储单元

如果采用双译码方式,将十五位地址分为X、Y两组,X为8为地址、Y为7为地址,利用X和Y译码器输出的交叉选择,同样可以确定这么大小的不同存储单元,而两个译码器的输出共仅需 2 8 + 2 7 = 384 2^8+2^7=384 28+27=384根线

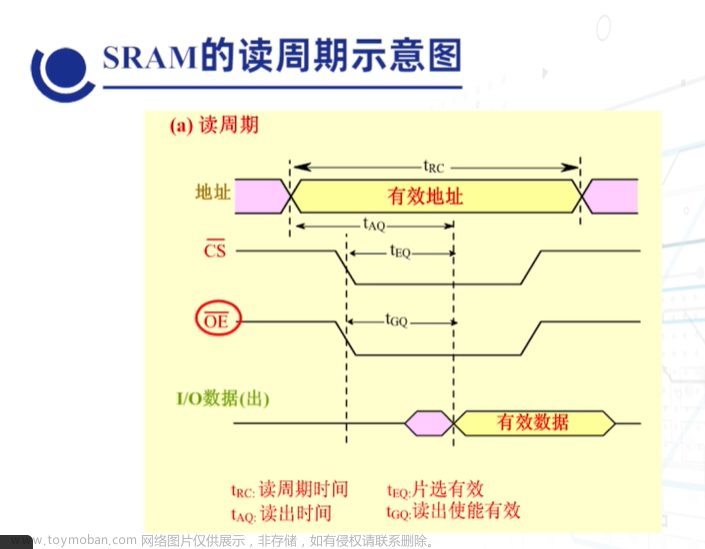

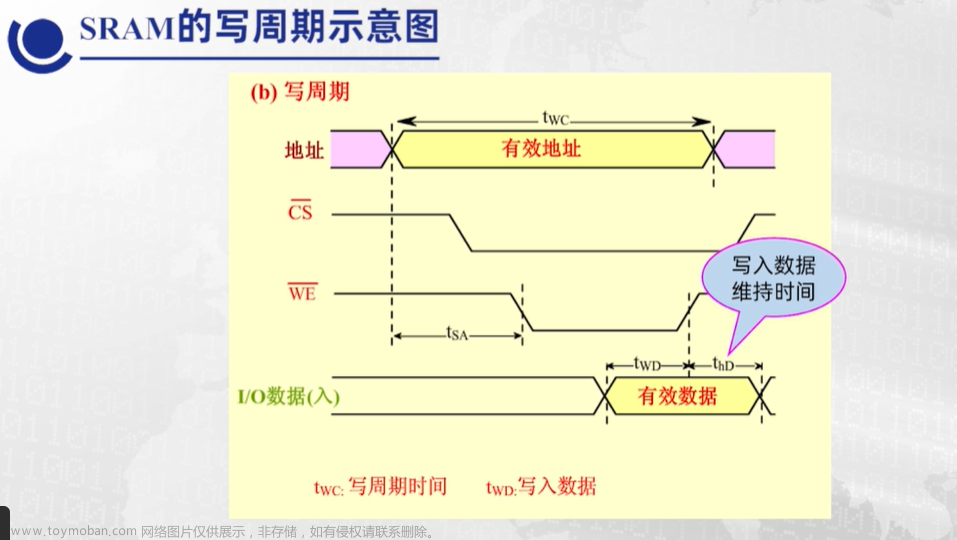

首先地址线有效,选中对应存储单元,然后片选信号和输出使能有效,可以读出数据

动态RAM存储器

动态RAM存储器存储元简化了结构,由一个MOS管和电容组成单管的记忆电路。

MOS管作为开关使用,栅极接高电位MOS管打开、接低电位MOS管关闭,所存储的信息是1还是0,由电容器的电荷体现,当电容充满电荷时表示为1,放电没有电荷时存储位0

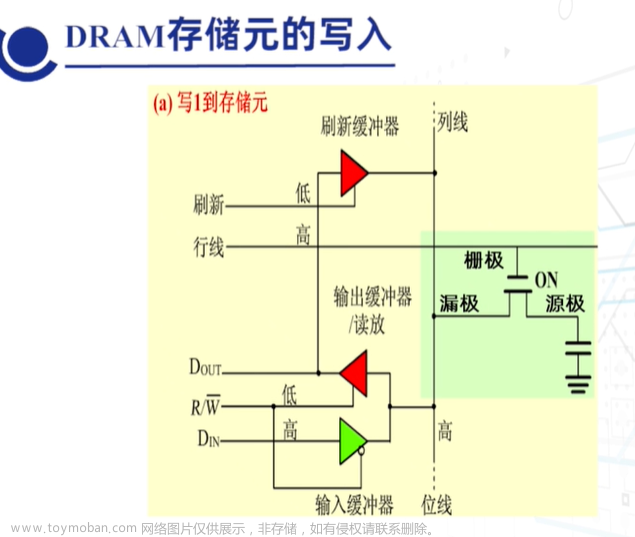

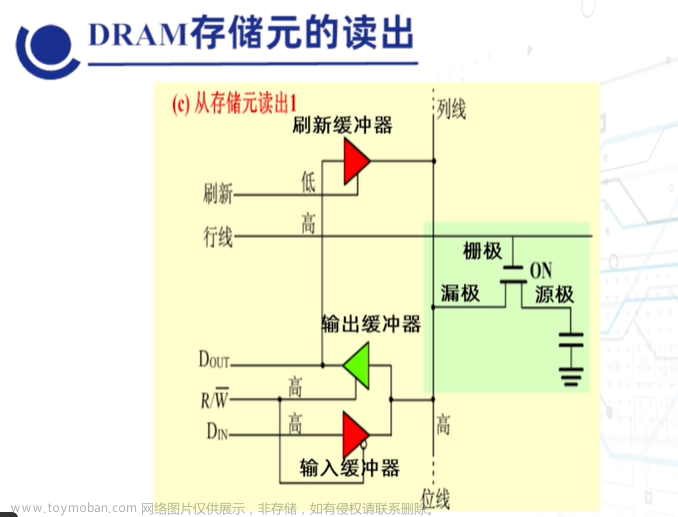

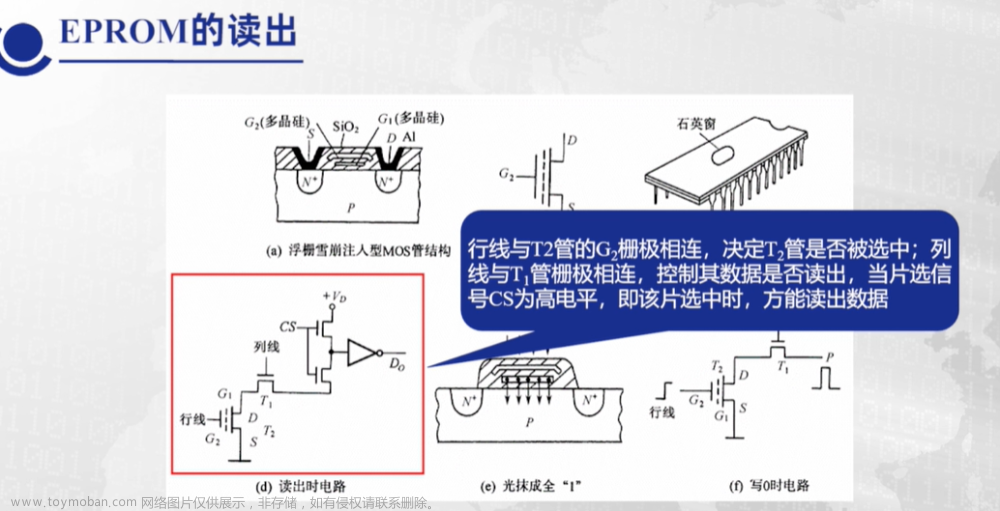

写1到存储元时,输出缓冲器和刷新缓冲器都关闭,输入缓冲器打开,输入的数据1经DIN送入到存储元位线上,此时行线为高,打开MOS管,漏极和源极接通,位线上的高电平给电容充电,就写入了1。写0时,同样的,但是此时位线上为低电平,因此电容放电,就写入了0。

在读出数据时,刷新缓冲器和输入缓冲器关闭,输出缓冲器打开,行列线选中对应存储单元,栅极为高,漏极源极接通,如果电容存储信息为1,则经由位线送到输出缓冲器输出到Dout,读出数据,读出数据会破坏电容上存储的信息,所以要把数据重新写入,也就是存储元的刷新操作

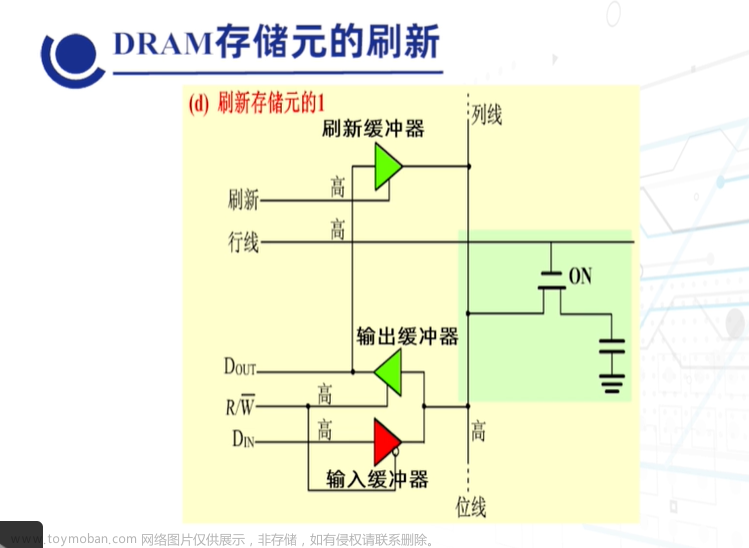

刷新操作时刷新缓冲器和输出缓冲器均打开,将Dout输出的数据重新写入存储单元

由于读写操作互斥,输入缓冲器和输出缓冲器一直处于互锁的状态

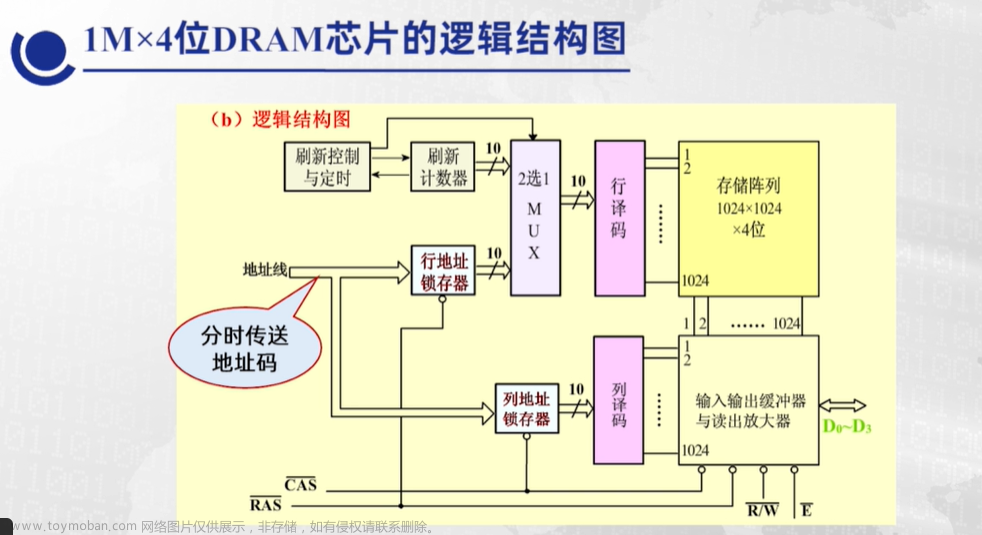

1M*4位DRAM芯片

按理说上图中芯片应该有二十个地址引脚,但是实际上只有十个

逻辑结构图,采用分时传送地址码

由于DRAM存储元电路所用器件少,其集成度高,所用容量大,这会增加芯片引脚数目,因此采用分时传送的方式。

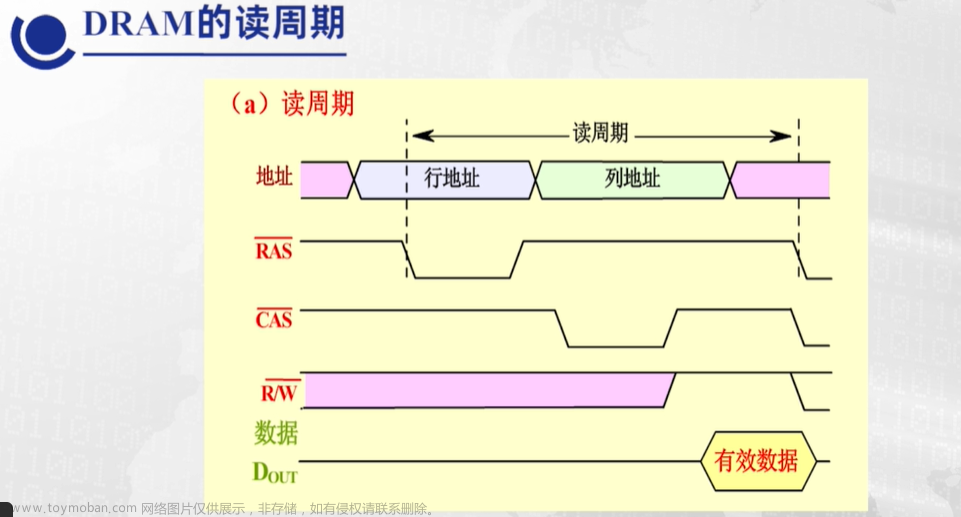

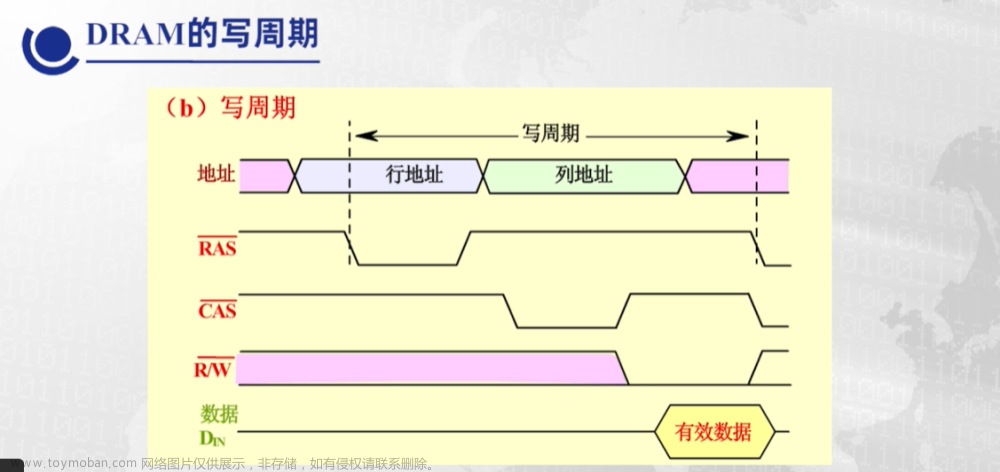

先选中地址信号 A 0 − A 9 A_0-A_9 A0−A9,由行选中信号RAS*打入到行地址锁存器,然后再传送地址码 A 10 − A 19 A_{10}-A_{19} A10−A19,由列地址选中信号CAS*打入列地址锁存器,分别经过行译码和列译码,选中对应存储单元

在DRAM的内部还增加了刷新计数器和相应的控制电路.

DRAM刷新时是按照行进行刷新,一次要刷新一行上的所有存储元

刷新操作与读写操作是交替进行的,通过二选一的多路开关来提供刷新行地址或正常读写的行地址

DRAM的刷新

- DRAM必须进行定期刷新

因为读操作会影响电容存储的数据,而就算不读取,电容也会随着时间发生电荷的泄露

- 刷新操作与读操作类似,不过无需送出数据

- 一次刷新选中一行中所有存储位元

- 内部有刷新电路

- 刷新方式有以下两种

- 集中式

- 分散式

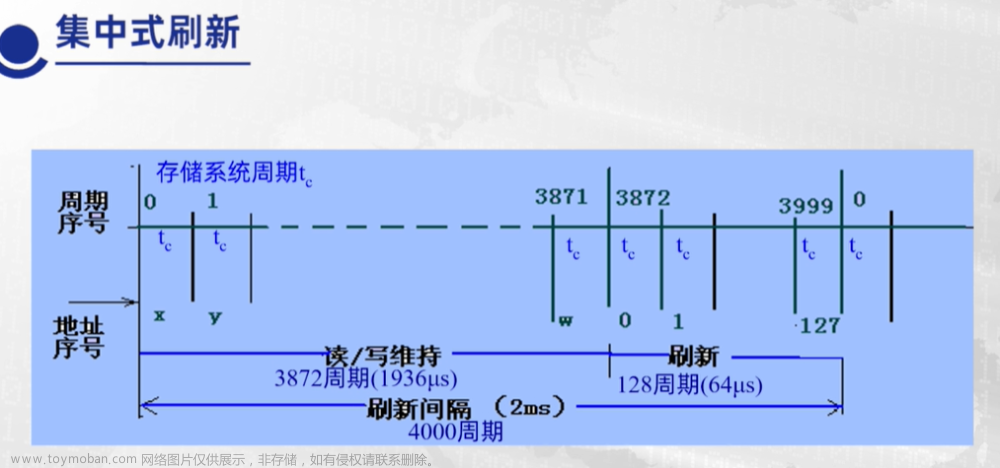

集中式刷新

集中式刷新是在规定的一个刷新周期内,对全部存储单元集中一段时间逐行进行刷新

特点为:

- 由于刷新工作集中进行,对芯片的正常读写周期不产生影响

- 同样由于刷新工作的集中进行,会造成芯片死时间过长的问题

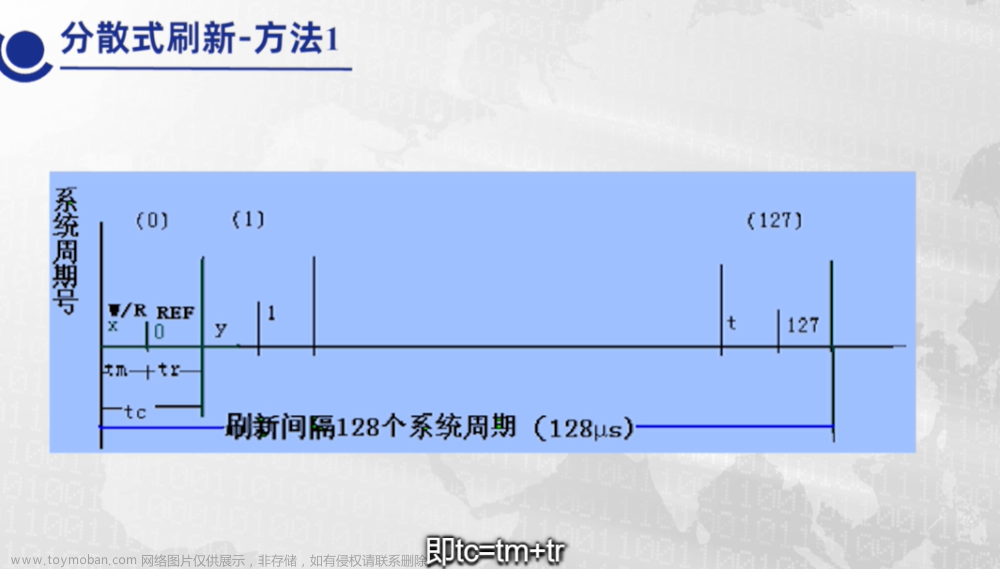

分散式刷新

- 将每行存储单元的刷新分散到每个存储周期完成

一个读写周期的前段用来进行读写操作,后段用来进行刷新,

- 增长了存储周期,降低了系统速度

- 刷新过于频繁

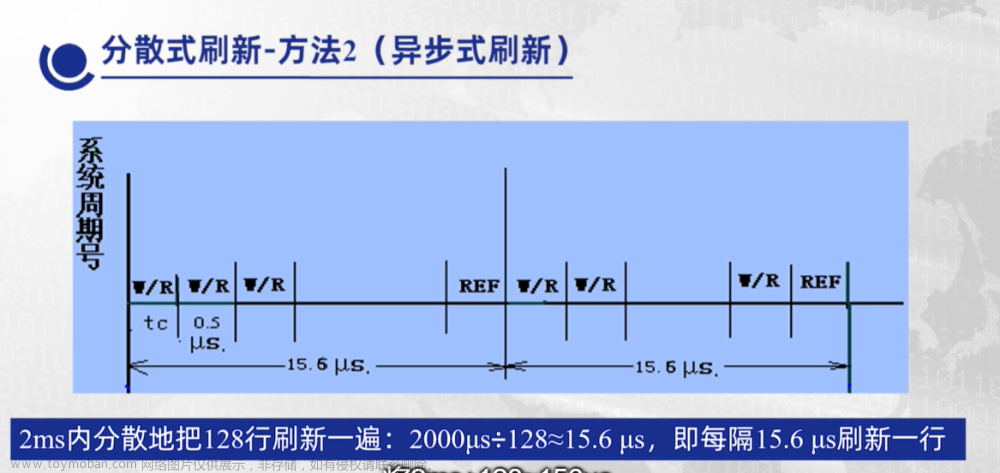

- 异步式刷新

没有集中刷新的死时间,并且保证了信息不会丢失

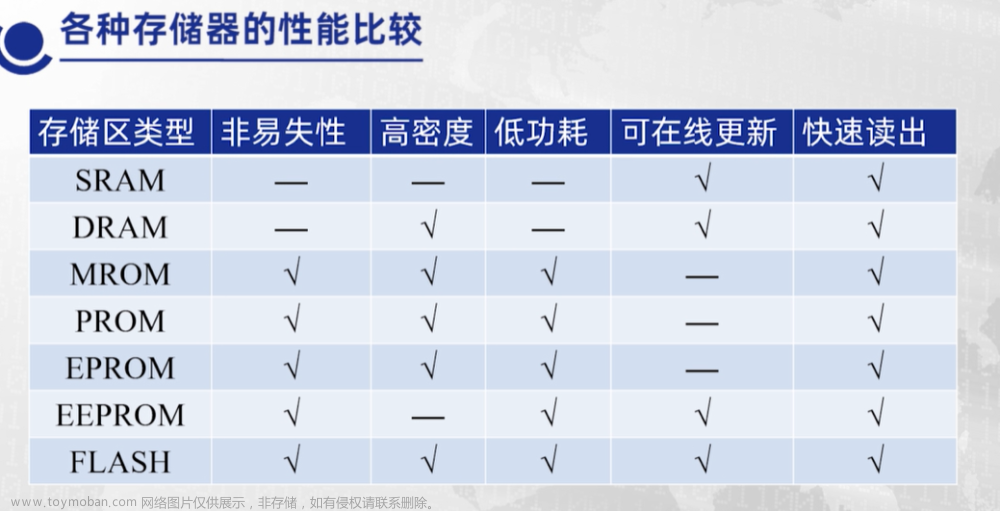

ROM只读存储器

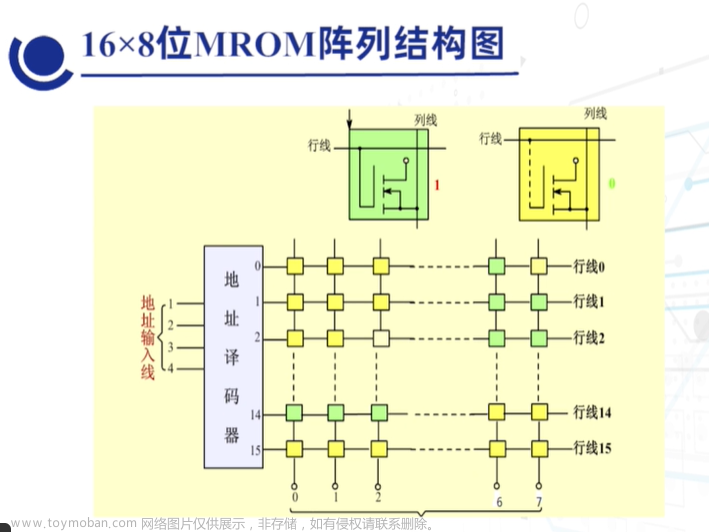

掩膜ROM(MROM)

- 存储内容固定的ROM,由掩膜工艺一次性制造

- 一旦ROM芯片做成,不能够改变其存储内容

- 用于存储广泛使用的具有标准功能的程序或数据,或用户定做的具有特殊功能的程序或数据

- 适宜没有更新需求的大批量应用

上图每一个行列交叉点是一个MOS单元,黄色的存储元表示存储零、绿色的存储元表示存储1.

当行线与MOS的栅极连接时,MOS管导通,列线上为高电平,表示该存储元存储1

当行线与MOS管的栅极不连接时,MOS管截止,表示存储的位0

这里的0/1在商家生产后就固定好了,用户没法改变,因此是纯粹的只读存储器

一次可编程存储器PROM

允许用户利用专门的设备(编程器)写入自己的程序和数据,但只能写入一次,一旦写入,其内容将无法再改变。PROM出厂时将所有单元制成0或者1,然后由用户需要自己将对应单元改为0或者1

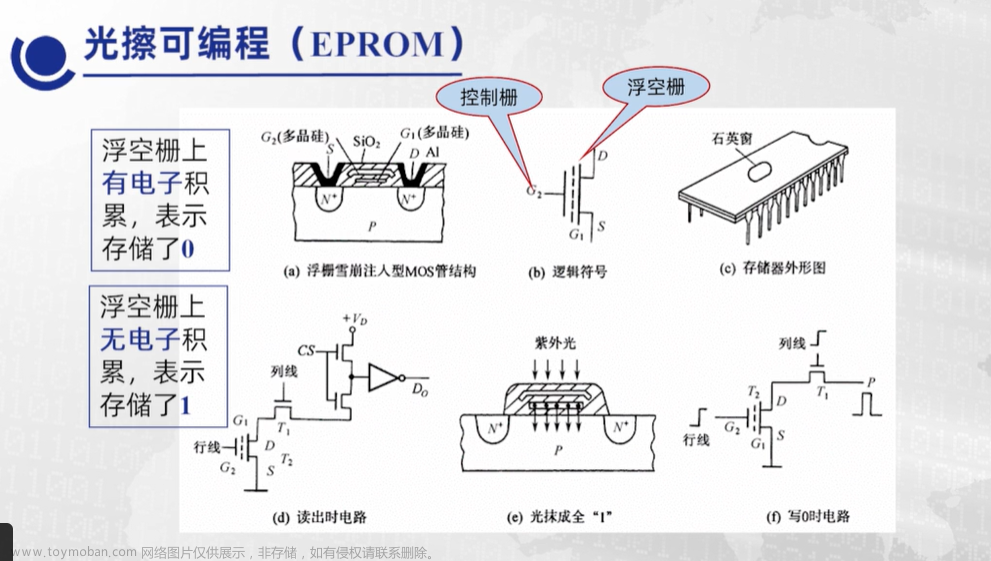

光擦可编程EPROM

电擦可编程EEPROM( E 2 P R O M E^2PROM E2PROM)

- 采用电擦除、且擦除速度快

- 不像光擦可编程需要将存储器从电路板拔下来在专门的仪器上操作,可以直接控制擦除

- 可以按单字节编程擦除、使用方便

- 容量比较小、单位成本高

- 可重复擦除的次数比较多

- 用于存储偶尔需要更新的系统配置信息、系统参数、加密保护数据或历史信息等

能否用EEPROM取代RAM呢?

不可以

- EEPROM的编程次数或者说改写次数虽然有很多次,但是还是有限的

- EEPROM的写入时间过长,比SRAM或者DRAM的时间长100-1000倍

Flash存储器

一种高密度电可擦除可编程的非易失性只读存储器

- 高密度表示具有很高的存储容量

- 电可擦除表示可以方便的反复多次改写

- 非易失性说明在没有电源的情况下它也可以长期保存

既有ROM的优点,又有RAM的优点

根据存储元工作原理和制作工艺的不同,FLASH可以分为以下几种

- NOR技术

- DINOR技术

- AND技术

- NAND技术

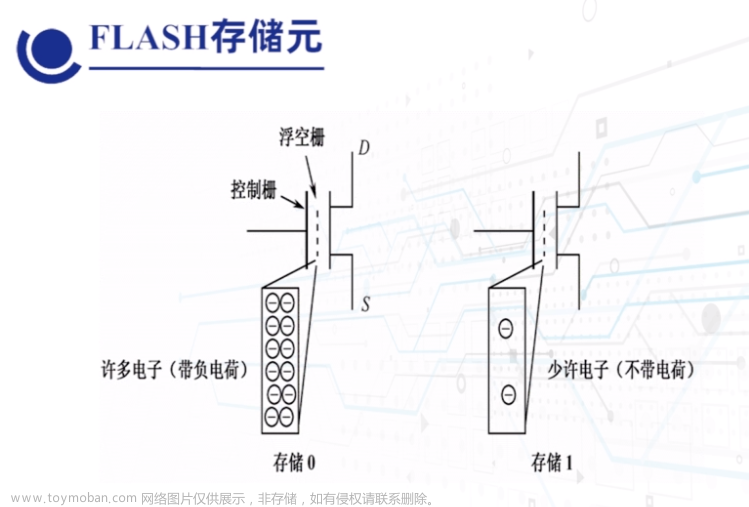

上面是flash的存储元,他是在EPROM的基础上改进而来的,当浮空栅带有许多电子(负电荷)时表示存储0,当带有少量电子可认为不带电荷时表示存储1

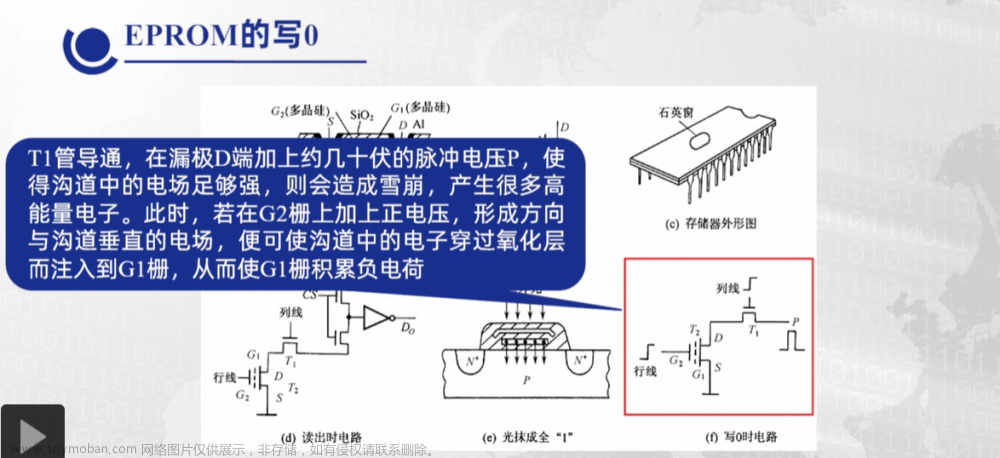

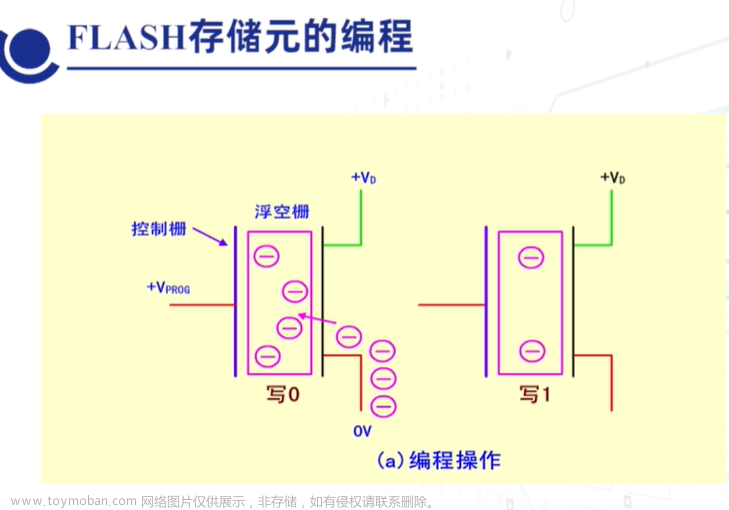

FLASH的编程操作

当向存储元写0时,在控制栅添加正电压,这样浮空栅就会产生大量的负电荷,从而使存储元存储0

不加正电压就会保持1的状态

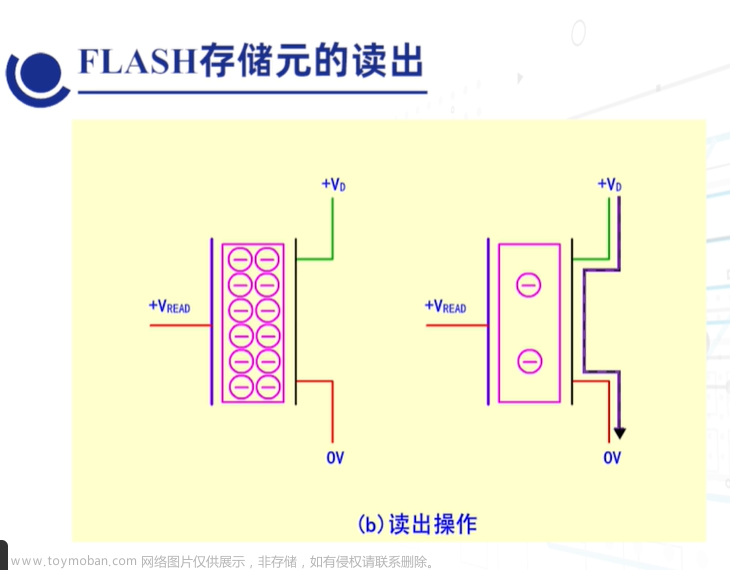

FLASH存储元读出操作

读出操作时,控制栅加上正电压,浮空栅中的电荷量决定是否可以导通MOS晶体管,如果浮空栅带有少许或不带负电荷,MOS管导通,电源 V D V_D VD提供从漏极D到源极S的电流,读出电路检测到有电流就表示读出了1,如果浮空栅带有很多负电荷,控制端的正电压不足以克服负电荷导通MOS管,那么源极和漏极就不会产生电流,表示读出了0

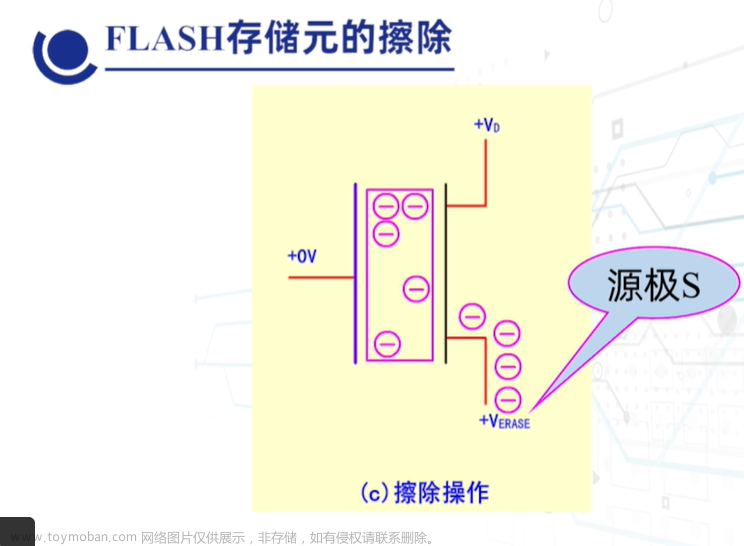

FLASH的擦除操作

擦除操作令所有存储元都置为1,即要把浮空栅的负电荷都释放出去,在源极S加上正电压,会吸收浮空栅中的负电荷,从而令存储元置1

NOR闪存

通常称为线性闪存

- 可以随机读出任意地址的内容,读出速度高

- 存储在其中的指令可以直接执行

- 可以对单字节或单字进行编程

- 以区块或者芯片为单位执行擦除

- 有独立的地址线和数据线,接口与SRAM相似,信息存储的可靠性高

NOR闪存的擦除和编程速度较慢,且区块尺寸较大,因此NOR闪存更适合于擦除和编程操作较少,而直接执行指令代码的场合

- 适合存储监控程序、引导加载程序、系统配置等

NAND闪存

-

通常称为非线性闪存

-

以页为单位读出,非随机访问

-

存储在其中的指令不能够直接执行

-

以页为单位进行编程

-

以数十页组成的块为单位进行擦除操作

能够快速编程和快速擦除

-

数据线、地址线和控制线复用在同一组总线信号上接口方式与传统ROM不同

NAND非随机存储,不能够直接存储在线运行的代码,但是其存储密度高、造价低,通常容量较大,适用于大容量存储设备

无机械运动、可靠性高、存储速度快、体积小巧,因而已部分取代磁介质存储,比如固态硬盘、存储卡、U盘等

对比

存储容量的扩展

CPU经由地址总线将地址传送到主存,CPU通过控制总线将读写操作指令传送到主存,通过数据总线与主存进行数据交互

单片存储芯片的容量是有限的,因此要多个存储器芯片组成足够容量的存储器

存储器容量的控制方法有:位扩展、字扩展、字位同时扩展。

所需芯片数可以由下面的公式计算出:

d

=

设计要求的存储器总容量

选定芯片存储器的容量

d=\frac{设计要求的存储器总容量}{选定芯片存储器的容量}

d=选定芯片存储器的容量设计要求的存储器总容量

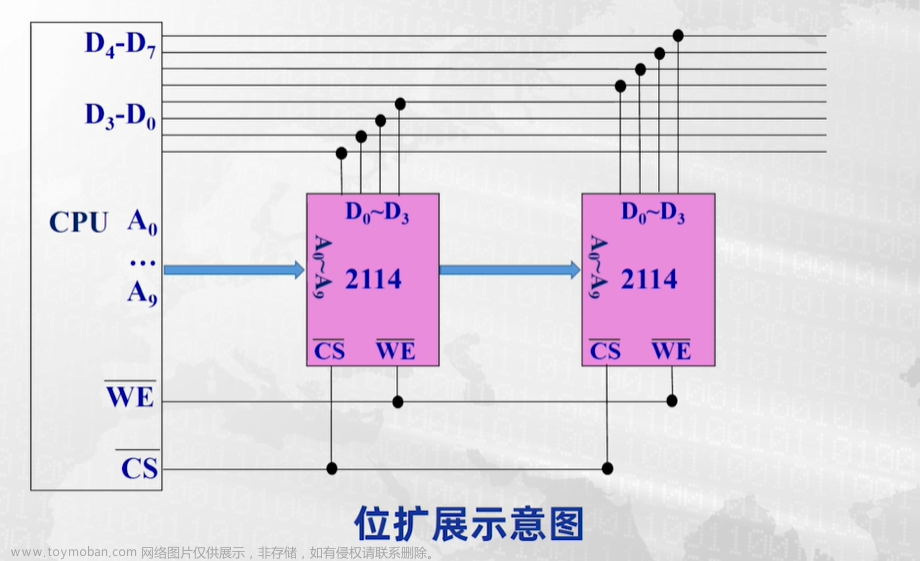

位扩展

只增加每个存储单元的字长而不增加存储单元的数量

接线方式:选定芯片的地址、片选、读写/控制信号线公用,数据线单独分开连接

上图是位扩展示意图

实际上就是原来的片选和读写控制信号还有地址选择信号,现在同时控制多个选定芯片存储器,但是对于数据线,分别输出,也就是实现了数据位的扩展

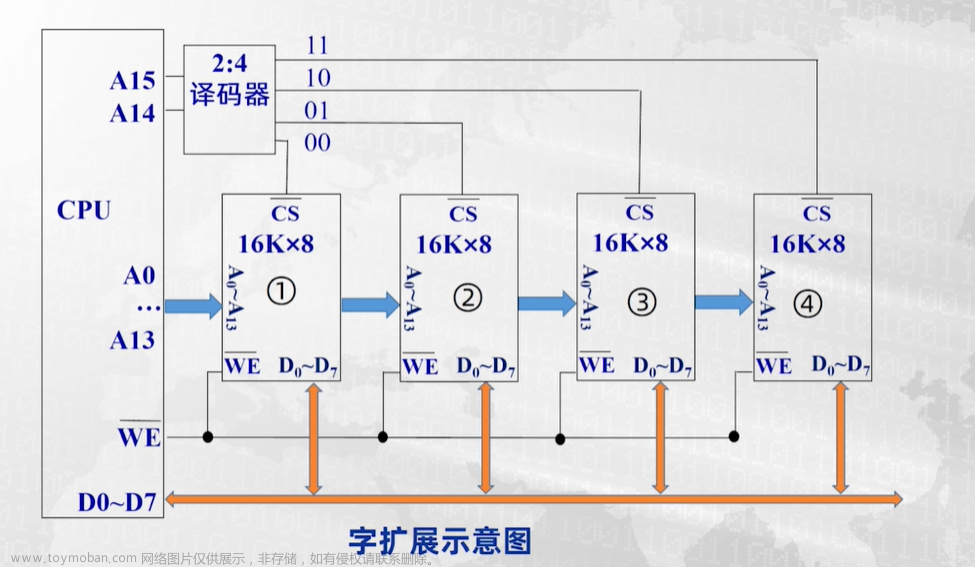

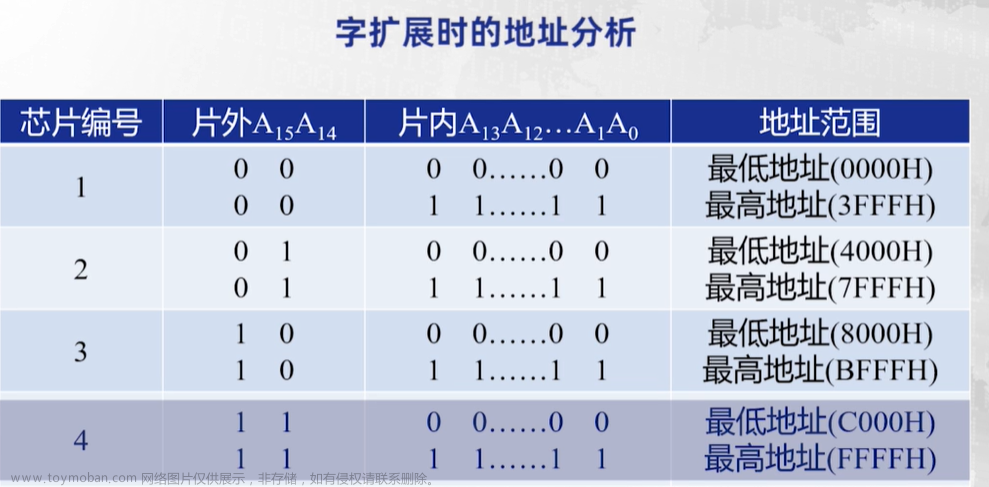

字扩展

给定的芯片存储容量较小,不满足设计要求的总存储容量,此时需要进行字扩展

连接方式:选定芯片的地址、数据、读/写控制信号线公用,由地址总线的高位译码产生片选信号让各个芯片分时工作

由图可以看出,每个芯片的处理都一样,但是使用译码器控制各个芯片分时工作,CPU中的地址线需要分出来两个用作译码来选择对应芯片

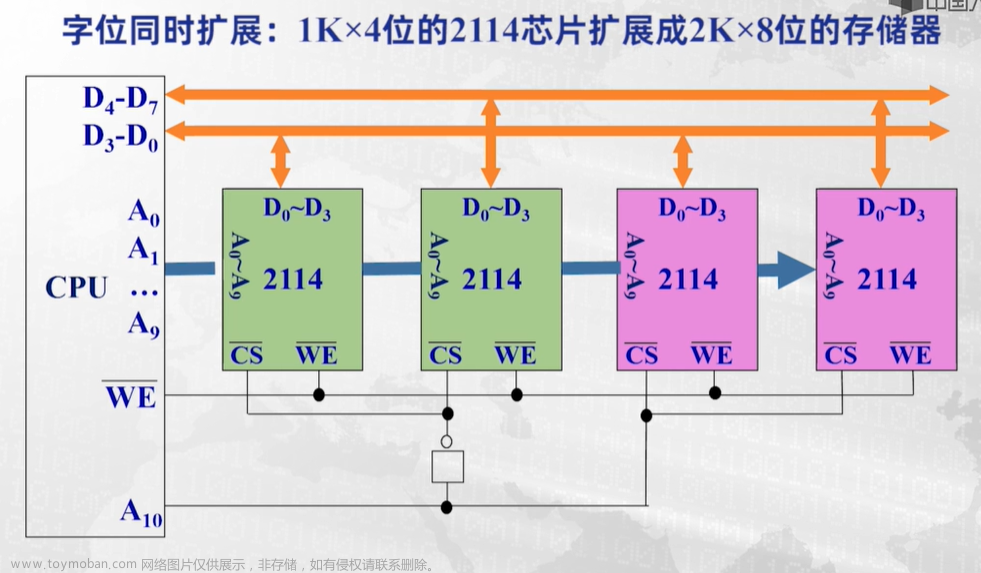

字位同时扩展

即增加存储字的容量又增加存储字长

扩展方式:先进行位扩展再进行字扩展

先把芯片分组,然后进行字扩展,把地址线与每组对应位置相连,最后连接读写控制信号、地址线,然后使用译码器或简单逻辑电路控制每组芯片分时工作。

注意

不同的扩展方法可以得到不同容量的存储器,要注意合理选择芯片文章来源:https://www.toymoban.com/news/detail-402738.html

- 通常选用ROM芯片存放系统程序,标准子程序和各类常数等

- RAM芯片则是为用户编程提供空间

- 在扩展时应该尽可能的选用集成度高的芯片,可减少成本,减轻系统负载

- 在实际的应用扩展中,还需要考虑CPU与存储芯片的时序配合,速度匹配等问题

内存条

文章来源地址https://www.toymoban.com/news/detail-402738.html

文章来源地址https://www.toymoban.com/news/detail-402738.html

到了这里,关于存储系统及主存储器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!