PHY芯片IP101GR

1. 预备知识

接上文

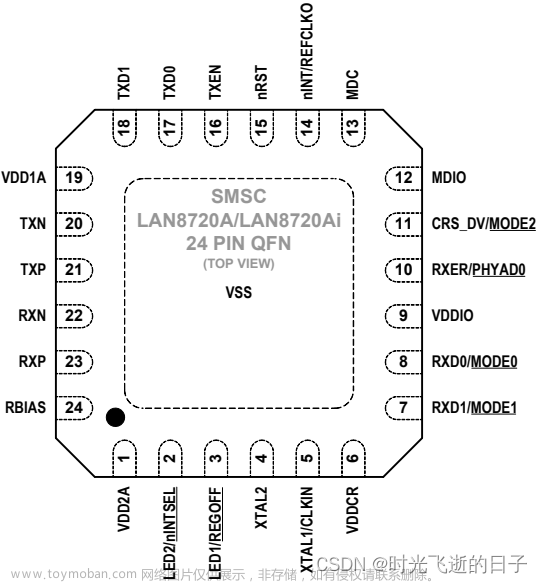

《GD32F450以太网(1):ETH 外设接口简介》介绍了嵌入式以太网接口。

《GD32F450以太网(2-1):PHY芯片LAN8720A介绍》介绍了LAN8720A

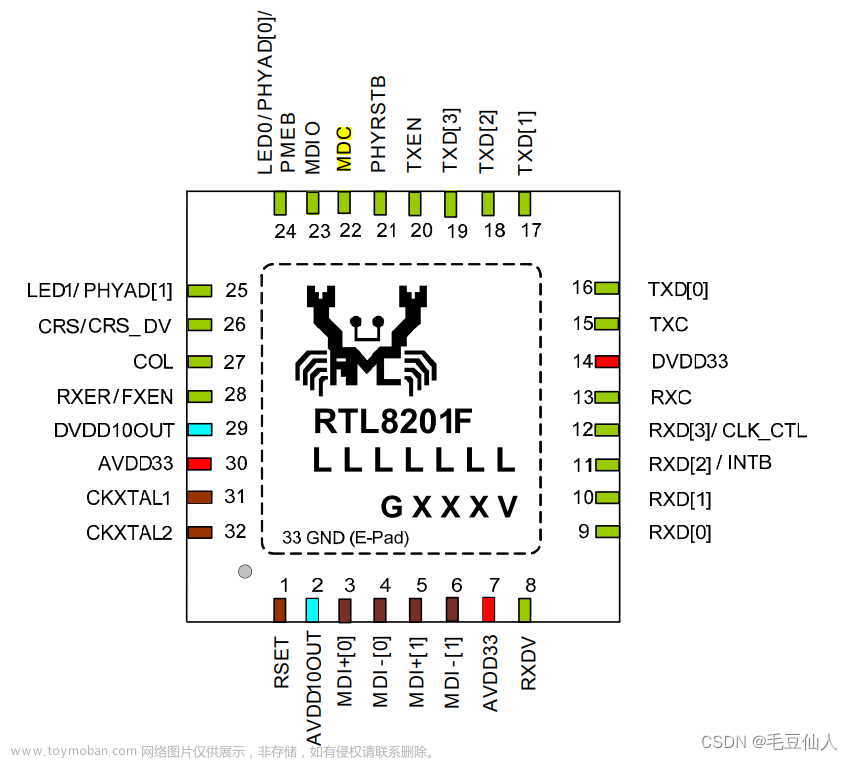

本文介绍另外一款PHY芯片IP101GR,支持MII接口或RMII接口,可代替市场上LAN8710A/LAN8720A/KSZ8041等芯片。

2. IP101GR简介

IP101是台湾省九阳电子公司生产制造的,符合IEEE 802.3/802.3u标准单端口快速以太网收发器100Mbps和10Mbps操作,它支持自动MDI/MDIX功能,简化网络安装和减少系统维护成本。提高系统性能,部分功能介绍如下:

- 支持Auto MDI/MDIX

- 已内置4个49.9欧的精密电阻

- 支持中断功能

- 支持 MII/RMII 接口

- 超低功耗,全负荷运转(100 Mbps_FDX)时,只需低于0.15 w。

- Rx to Tx 回环

- 有一个PECL接口可支持连接额外的100Base-FX光纤收发器。

IP101有一系列具体的型号,IP101GR只是其中的一种,具体可以在立创下载数据手册来了解,我也上传了数据手册,下面简单介绍一下主要区别:

| 型号 | 引脚数 | 工作温度范围 |

|---|---|---|

| IP101GA | 48LQFP | 0-70度 |

| IP101GR | 32QFN | 0-70度 |

| IP101GRI | 32QFN | -40-85度 |

| IP101AH | 48LQFP | 0-70度 |

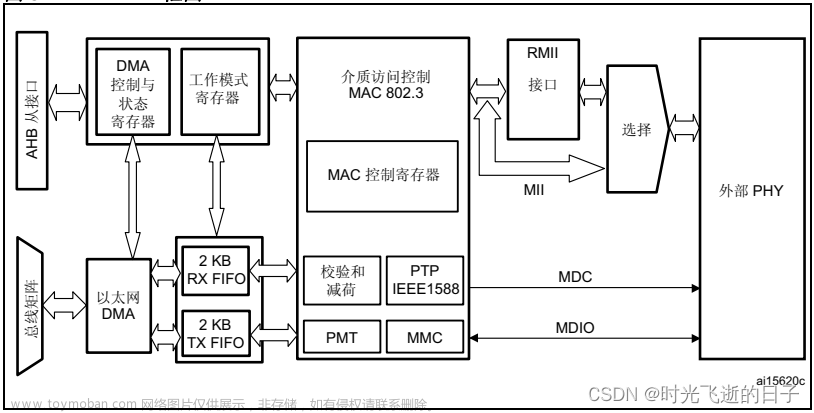

3. IP101GR基于RMII接口的PCB设计重点解析

说明:因为本文使用的目的主要是替换LAN8720,因此我只介绍RMII接口的设计和使用,对于MII接口的pcb设计,请参考数据手册自行完成。

PHY芯片的原理图有几部分非常重要,包括时钟选择,led灯设计,PHY芯片地址设定,下面我们依次介绍这几部分。

3.1 时钟设置

时钟的设计要完成两件事:

第一:PHY芯片工作是需要时钟的,因此PHY芯片需要时钟,一般都是25M或50M。

第二:RMII通信,需要时钟的,必须是50M。因此设计的时候必须为这两部分提供时钟。

回顾以前发的文章,我们知道对于LAN8710有两种方法解决:

-

一种是由外部提供50M的时钟(可以是有源晶振,也可以是MCU引脚输出),同时接入PHY芯片XTALI引脚和REF_CLK引脚,这样就可以也同时为PHY芯片和RMII通信提供时钟。

-

另一种是将PHY芯片接入25M晶振,在由PHY芯片内部PLL倍频到50M输出到REF_CLK引脚,从而实现为PHY芯片和RMII通信提供时钟。

对于IP101GR通过设置COL引脚为1,来选择IP101GR工作在RMII接口模式,在RMII接口模式,官方文档提供了两种方法来设置时钟:

-

提供一个25MHz无源晶振到引脚X1和X2或提供一个25MHz的有源时钟到X1引脚,RXCLK/50M_CLKO引脚将会输出50M时钟,接到 TXCLK/50M_CLKI,将会为RMII通信提供50M时钟,如下:

-

X1接地,外部提供一个50M时钟(可以由mcu产生,也可以外接有源晶振)接到TXCLK/50M_CLKI引脚,此时PHY芯片和RMII通信都可以获得50M时钟,如下:

注意:对于时钟的两个作用:PHY芯片工作是需要时钟的,能接25M或50M,RMII通信,需要时钟的,必须是50M,因此才有上面的接法。总结IP101的时钟的3种设计,如下:

其中,GD32F4的PA1引脚是REF_CLK引脚,这个对于不同芯片引脚也应该是不同的。

3.2. led灯设计

IP101G提供2种LED工作模式:

模式1(默认):

| LED | 功能 |

|---|---|

| LED0 | 链路状态:Active表示链路已经建立 |

| LED1 | 双工操作:Active表示全双工 |

| LED2 | 10BT/ACT: Active表示10Mbps连接已经建立, |

| LED3 | 100BT/ACT: Active表示100Mbps连接已经建立,当有数据收发的时候会发生闪烁 |

模式2:

| LED | 功能 |

|---|---|

| LED0 | 链路状态:Active表示链路已经建立,当有数据收发的时候会发生闪烁 |

| LED1 | Duplex/COL: Active表示全双工,当发生冲突事件时闪烁。 |

| LED2 | 10BT/ACT: Active表示10Mbps连接已经建立 |

| LED3 | 100BT/ACT: Active表示100Mbps连接已经建立 |

对于led模式,一般我们都采用默认,若更改模式需要设置IP101GR的第20引脚脚,因此本文就不讨论设置led模式了,直接采用默认。

当led闪烁的时候,闪烁速度说明:On 26ms -> Off 78ms -> On 26ms -> Off 78ms …

对于IP101GR,只有LED0和LED3两个led灯,这两个led灯一般我们直接与网口上面灯相连,由于led和PHY芯片地址设置引脚是复用的,因此在PHY芯片地址设置部分说明引脚连线方式。

3.3. PHY芯片地址设置

每一个PHY芯片都有自己的地址,因此对于PHY模块来说,是可以同时连接好几个来实现多网口的。IP101的配置地址引脚和led的引脚是复用的。因此对于IP101GR只有两条地址配置引脚PHY_AD0和PHY_AD3, PHY芯片在上电的时候,引脚会配置成输入,此时引脚处于PHY_AD0和PHY_AD3状态,当 PHY芯片读完引脚的电平后,就会把引脚配置成输出,此时引脚处于LED0和LED3状态。

对于32 pin的ip101芯片来讲,由于只有地址LED0和LED3,没有LED1和LED2,引脚关系如下:

| led3/PHY_AD3 | led0/PHY_AD0 | PHY芯片地址 |

|---|---|---|

| 0 | 0 | 5’d0 |

| X | 1 | 5’d1 |

| 1 | 0 | 5’d2~5’d31 |

X表示不关心,当led3=1;led0=0的时候地址2到31都能得到响应,对于48pin引脚芯片,地址定义请自行查看手册。

书册中也准备好了PHY_ADx的画法,当想要高电平,则按左边的设计,需要低电平的按右边图设计,如下:

4. pcb设计

下面是采用PHY外接50M晶振来实现clk_50M的方案原理图设计:

引脚4的COL接电阻上拉来先择使用RMII方式通信,当19引脚RXDV上拉是配置为光纤模式,这里使用普通网卡因此我添加了一颗下拉电阻。当X1、X2引脚接25M晶振,50M时钟将从14引脚输出,为了输出到RMII时钟上,因此要将10引脚和14引脚连在一起,并且在连接到mcu的rmii_clk引脚上面。若使用外部提供50M时钟方案,那么就需要将X1引脚接地,此时需要外部提供50M时钟同时接到10引脚和mcu的rmii_clk引脚上面。

由于31引脚AVDD33是一个模拟电源输入,因此需要为它的电源进行一次滤波,来保证稳定,如下:

网口设计,采用一个集成变压器的网口,如下:

注意:对于设计过其它网口的人来讲,一般需要在线路进入变压器前串联精度较高的49.9欧电阻,但是IP101自带了这个这个部分,因此不需要我们在管。

上面的图中在连接网口灯的时候,可实现PHY芯片的地址配置,当R18、R24连接,R23、R25不焊接的时候,配置地址为1,当R23、R25连接,R18、R24不焊接的时候,配置地址为0。

对外接口设计,就是将RMII引脚和复位引脚、错误指示引脚引出来,MCU可以不全部连接,如下:

最后设计3D图:

对于使用外部提供50M的时钟方案也很好实现,只需要更改一下时钟线的连接。

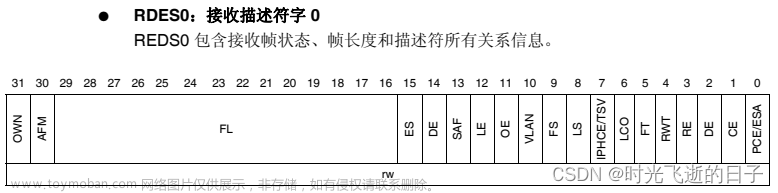

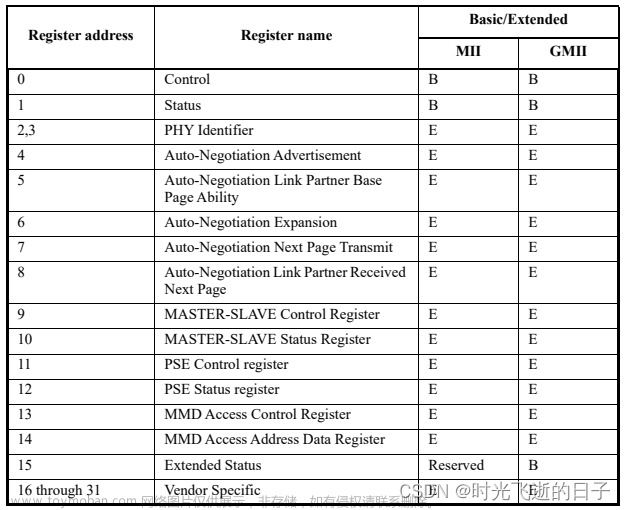

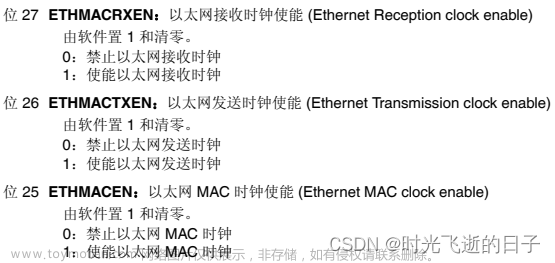

5. 寄存器描述

PHY是由IEEE802.3定义的,一般通过SMI对PHY进行管理和控制,也就是读写PHY芯片的内部寄存器。PHY寄存器的地址空间为5位,可以定义031共32个寄存器,其中IEEE802.3定义了015这16个寄存器的功能,PHY芯片厂商不可任意修改,剩下的16~31寄存器由芯片制造商自己定义,用于实现一些自己独有的功能。但是随着PHY芯片功能的增加,很多PHY芯片都采用分页技术来扩展地址空间,定义更多的寄存器,IP101G就采用分页技术来扩展了地址。我有另外的一篇文章,介绍了分页技术的原理和访问方式,在这里我就不多讲了。

使用过LAN8720A的都知道,LAN8720A重点关注三个寄存器,BCR寄存器、BSR寄存器、PHY特殊功能寄存器,由于BCR寄存器和BSR寄存器是在前16个寄存器中,PHY芯片厂商不可任意修改,因此不管使用那家的PHY芯片,BCR寄存器和BSR寄存器的相关配置都可以拿来直接用,下面我列出IP101g最重要的4个寄存器,如下:

| Page | Register | Description | Default | Note |

|---|---|---|---|---|

| X | 20 | 页面控制寄存器 | 0x0010 | 页配置寄存器 |

| – | 0 | 控制寄存器 | 0x3100 | BCR寄存器 |

| – | 1 | 状态寄存器 | 0x7849 | BSR寄存器 |

| 16 | 30 | PHY MDI/MDIX控制和特定状态寄存器 | 0x0000 | PHY特殊功能寄存器 |

注:X表示不关心

关于BCR寄存器和BSR寄存器这两个地址的内容,请参考我的另一篇文章《GD32F450以太网(2-1):PHY芯片LAN8720A介绍》,下面我们重点介绍IP101对应的那个PHY特殊功能寄存器的使用方法。

首先这个PHY芯片采用了分页技术来扩展地址空间,这个特殊寄存器位于第16页的reg30。我有一篇文章介绍了分页技术来扩展地址空间内存的访问方式,文章链接。

特殊功能寄存器各位含义如下:

我们知道用来寻找页的页配置寄存器的地址是reg20,感到庆幸的是这个寄存器的默认值是0x0010,也就是16,正好在特殊寄存器所在的页,因此我们可以不必设置页就可以访问特殊寄存器,因此就当一个地址为reg30的普通寄存器就可以了。

我们在已经完成LAN8720A驱动的程序上直接修改(这种程序几乎对任何MCU都有现成的移植程序),其实IP101GR和LAN8720是差不多的,只是PHY特殊功能寄存器有区别,因此对于已经实现LAN8720驱动的程序,只需要稍微改一下寄存器就可以直接驱动IP101GR。通过修改程序来适配IP101GR,最后的程序配置如下:

- BCR寄存器、BSR寄存器不需要修改。

- 特殊寄存器修改如下:

#define PHY_SR 30U /*!< tranceiver status register */

#define PHY_SPEED_STATUS ((uint16_t)0x0001) /*!< configured information of speed: 10Mbit/s */

#define PHY_DUPLEX_STATUS ((uint16_t)0x0004) /*!< configured information of duplex: full-duplex */

其它的不用修改。

6. 附加:IP101GR和GD32F450引脚连接情况

因为我是用的是GD32F450来驱动IP101GR,因此顺道将我的连线图贴出来。文章来源:https://www.toymoban.com/news/detail-403082.html

IP101GR支持MII和RMII两种方式驱动,当我们采用RMII方式,下面是mcu和PHY引脚连接:文章来源地址https://www.toymoban.com/news/detail-403082.html

| 功能 | IP101GR对应引脚编号 | mcu对应引脚 | 描述 |

|---|---|---|---|

| 50M_CLKI | 10 | PA1 | 50M时钟线,无论采用那种时钟方式,这两个引脚必须相连 |

| 50M_CLKO | 14 | 当PHY芯片挂载25M时钟,此引脚为50M时钟输出和50M_CLKI相连。 当X1接地,则采用外部提供50M时钟,此引脚不需要引出。 |

|

| 50M_CLK | PA8 | GD32F4的PA8引脚可以配置输出50M时钟,当X1接地,采用外部提供50M时钟方式,可以让这个引脚和50M_CLKI和PA1相连,为PHY芯片和RMII提供时钟。 | |

| MDIO | 23 | PA2 | |

| CRS_DV | 19 | PA7 | |

| TXEN | 5 | PB11 | |

| TXD0 | 9 | PB12 | |

| TXD1 | 8 | PB13 | |

| MDC | 22 | PC1 | |

| RXD0 | 18 | PC4 | |

| RXD1 | 17 | PC5 | |

| RST | 32 | 拉高使能IP101GR芯片 |

到了这里,关于GD32F450以太网(2-2): PHY芯片IP101GR介绍的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!