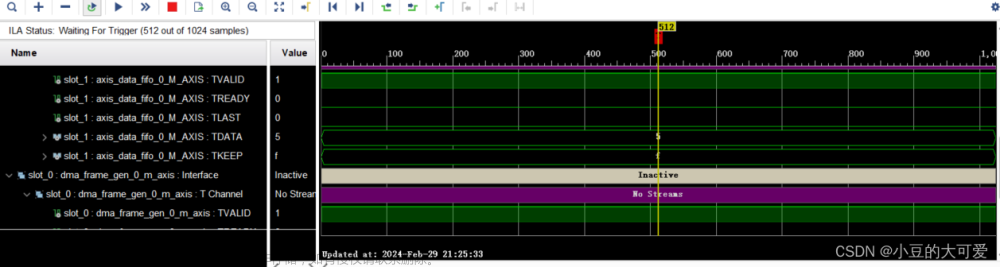

AXI-DMA:实现数据从PS内存到PL的高速传输。

Zynq芯片有4个高速接口 HP 口,接口时序是 AXI 时序,需要通过AXI 的时序把数据写入到 HP 口,HP 口实际是跟 ARM 的 DDR3 的控制器互联的,这样的话,就能把 FPGA 这一侧的数据写入到 ARM 的内存里面去,这个过程叫做 DMA。

DMA介绍:

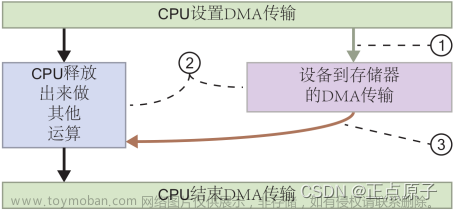

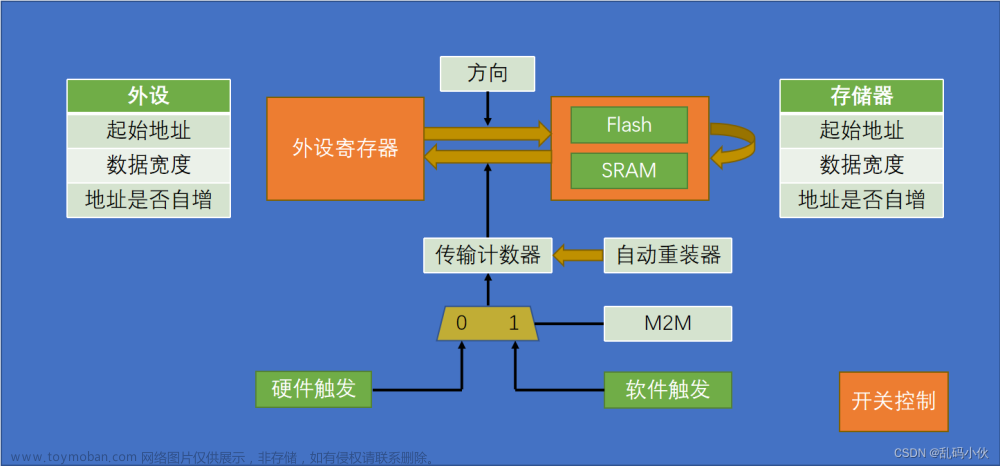

DMA直接存储器访问,无需CPU介入,提高数据的访问速率。因为CPU一个总线周期最多对总线进行一次读写操作,对于CPU处理器,如果要把内存中A地址的数据搬移到B地址,需要先将A地址的数据取出并放入寄存器,再从寄存器取出数据放入B地址,需要花费两个总线周期。而DMA可直接进行A地址到B地址的数据搬移。DMA在进行数据的传输期间,CPU被挂起,会失去对系统总线的控制,会影响CPU对中断请求的及时响应与处理。因此,DMA一般应用于速度要求高,数据传输量偏大的系统中。

DMAC为DMA控制器,DMAC取代CPU,控制DMA传输。

DMAC功能:

1. DMA请求,DMAC响应;

2. DMAC向CPU发起总线请求,CPU响应该信号;

3. DMAC接管对总线的控制权,进行DMA操作;

4. DMA传输结束,发出结束信号,释放总线,CPU恢复对总线的控制权;

AXI介绍:

AXI协议是基于burst的传输,burst突发不能超过4KB,不然就会访问到其他外设,会出现一个外设响应,而另一个外设并无响应,就会导致此笔burst交易无法完成。AXI协议定义了5个独立的传输通道:写地址、写数据、写响应、读地址、读数据;并且每个通道都有自己的握手协议。

信道间握手关系:

INFORMATION为要传递的数据,数据的提供方会输出 VALID 信号,数据的接收方要提供 READY 信号,当 VALID 与 READY 信号共同有效的时候,也即会采集到 information,也即只有在 T3的时候才会采集到。也就是 VALID 与 READY 握手的一个机制,一旦VALID 信号拉高,必须等待READY 有效之后才能拉低。若 READY 还未拉高,VALID 就拉低,这样就违背协议了。

Master设备和Slave设备通过interconnect组成的系统如下图,AXI总线作为其中的interface,实现数据通信。

为防止死锁,在读写传输事务上,AXI信号遵循了一定的依赖关系;

1. VALID不能依赖READY;

2. AXI接口可以等待检测到VALID才断言对应的READY,也可以检测到VALID之前就断言READY;

AXI写时序依赖关系:

AXI读时序依赖关系:

双箭头表示:前后有依赖关系,前面发生了,后面才会发生。

AXI outstanding:因为AXI数据传输是基于握手传输,即上一次传输完才进行下一次传输,读操作:读地址命令 -> 等待读数据返回 以此循环;写操作:写地址命令 -> 写数据 -> 等待写响应返回 以此循环;这期间可能会产生气泡。而outstanding模式,读操作:可以连续发N个读地址命令,这期间如果读数据没有返回,则等待;如果有数据返回,返回几个数据,就可以接着发几个地址;写操作:可以连续发N组写地址命令,这期间如果没有写响应返回,则等待,如果有写响应返回,返回几个,就可以接着发几组写地址命令。

AXI总线是基于握手协议进行传输,需要同时等到主机的VALID和从机的READY信号有效才能进行传输,并且地址和数据的传输是分离的;而outstanding就是发出去的地址数据,未处理的地址可以先存放在AXI综合性的缓存里,等待以此传输事物完成后,无需再握手,即可立即进行下一次的传输,所以outstanding本质上是为了实现数据的流水线传输。

对AXI而言,因为读写分离,所以outstanding分为读outstanding和写outstanding。

AXI的写响应信号是一个Burst传输完成之后返回一个写响应信号,并非每次握手传输完成之后返回,并且在数据传输完成之后,读写双方都会有LAST信号产生,用以标识最后一笔数据传输完成。

AXI突发写时序:

AXI突发读时序:

文章来源:https://www.toymoban.com/news/detail-403163.html

文章来源:https://www.toymoban.com/news/detail-403163.html

文章来源地址https://www.toymoban.com/news/detail-403163.html

到了这里,关于AXI-DMA的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!