前言

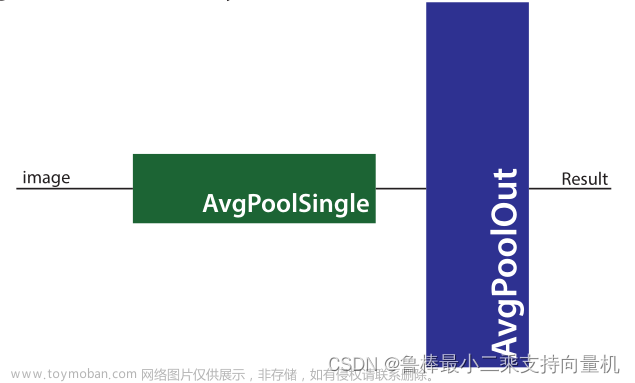

在编写基于verilog的的卷积神经网络实现时,需要定义一个滑窗,并与对应位置的图像像素值相乘再相加,实现单点的卷积运算,具体的操作如图1所示。 文章来源:https://www.toymoban.com/news/detail-403446.html

文章来源:https://www.toymoban.com/news/detail-403446.html

正文分析

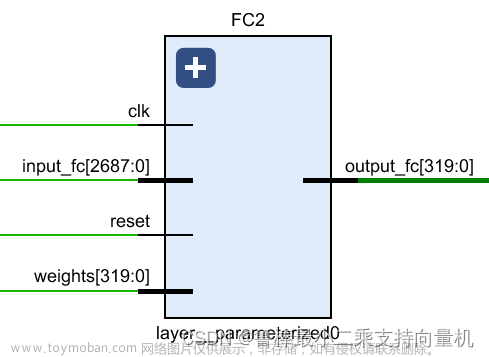

我们采用FPGA的RAM的进行图片(假设图片为5×5,滤波器的大小为3×3)数据缓存,由于图像的数据是按行展开串行送入,但是在进行卷积计算时,我们至少需要同时有3行的数据参与运算,所以需要定义数组为3的window_in和window_out用于RAM中图片缓存的输入与输出。文章来源地址https://www.toymoban.com/news/detail-403446.html

wire [7:0] window_in[0:3-到了这里,关于基于verilog的CNN搭建缓存图片数据浅析的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!