实验使用 Verilog HDL 实现了单周期 54 条 MIPS 指令的 CPU 的设计、前仿真、后仿真和下板调试运行。CPU 可实现 54 条 MIPS 指令。(详细论述所设计作品的功能)

二、总体设计

1 作品功能设计及原理说明

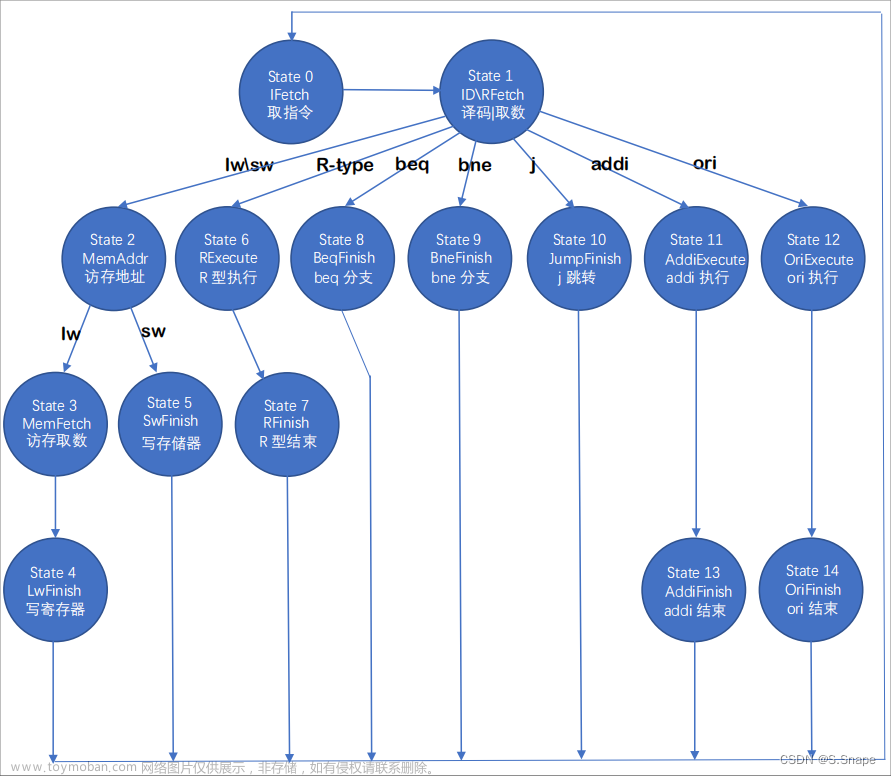

(作品总体设计说明,重点写清每条指令数据通路设计和控制器设计)

(一)总体设计说明

设计流程:先画出各指令的数据通路,再将所有指令的数据通路合成一个总数据通路,设计控制信号并列控制信号表,最后编写各模块并测试。

(二)数据通路设计

A)各指令数据通路

1)ADD

**指令功能:**rd←rs+rt,将通用寄存器中的 32 位数据 rs 与 rt 相加产生一个 32 位数据存入目标寄存器 rd。文章来源:https://www.toymoban.com/news/detail-403799.html

指令格式:ADD rd, rs, rt文章来源地址https://www.toymoban.com/news/detail-403799.html

到了这里,关于使用 Verilog HDL 实现了单周期 54 条 MIPS 指令的 CPU 的设计、前仿真、后仿真和下板调试运行 附完整代码的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!