set_max_delay:最大延迟约束

set_min_delay:最小延迟约束

约束原语:

set_max_delay [-datapath_only] [-from <node_list>] [-to <node_list>] [-through <node_list>]

set_min_delay [-from <node_list>] [-to <node_list>] [-through <node_list>]

一般在约束异步信号时可以使用。针对跨时钟域的异步信号,常使用set_false_path或者set_clock_groups,但是这两种约束会导致跨时钟域的信号完全没有受到约束。而使用set_max_delay约束可以保证两个异步时钟域的路径延时收到约束。

在设计时我们不会主动去添加,因为在设计之前,我们一般不会知道具体哪条路径为异步信号之间的时序路径,并且对于异步信号之间的路径,我们一般不关心其时序要求,通常是设为伪路径处理,如果我们确实要对某条异步信号之间的时序路径提出时序要求时,我们才设定它的最大最小延时,因此进行set_max_delay、set_min_delay时,我们一般是对整个工程进行综合实现了,根据时序报告和我们的要求,再对相应的路径添加set_max_delay、set_min_delay。

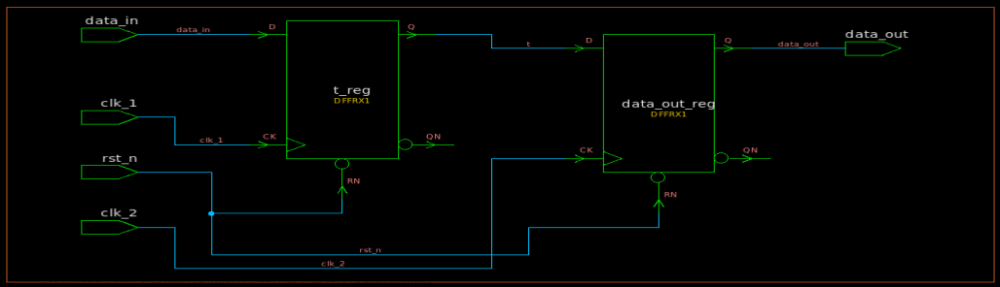

set_max_delay与set_min_delay这两种约束,一般用于特定的异步路径上,并且这种异步路径又不能不分析,比如异步FIFO的读写地址传递,虽然是格雷码,但也只能保证在一个源时钟周期内只有一条线发送翻转,如果不对源时钟到目的时钟路径进行max_delay的约束,那么很有可能地址从源时钟传递到目的时钟时,其传播路径延时会超过两个源时钟周期,特别是源时钟周期很小的情况下。

又比如说,同一时钟内,当某条路径总是不能满足(即周期跑不过),可以先用set_max_delay将这条关键路径约束起来(它的优先级比周期约束高),这样vivado会优先将这条路径布了,然后再去布其他路径,加大了布线成功的概率:

一般应用场景有两个:

输入管脚的信号经过组合逻辑后直接输出到管脚设置

异步电路之间的最大最小延迟设置文章来源:https://www.toymoban.com/news/detail-404978.html

本文为学习记录文档,内容大多为网上资料,如有侵权,请联系作者删除。文章来源地址https://www.toymoban.com/news/detail-404978.html

到了这里,关于时序约束——set_max_delay和set_min_delay用法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!