RC正弦波振荡器

采用LC器件作为振荡电路的反馈网络可以达到很高的输出频率,器件比较容易实现小体积。但是要求振荡器输出几十或者几百Hz信号时,LC器件的取值会很大,很难实现实用的产品,此时采用RC选频网络就会有很大的优势。

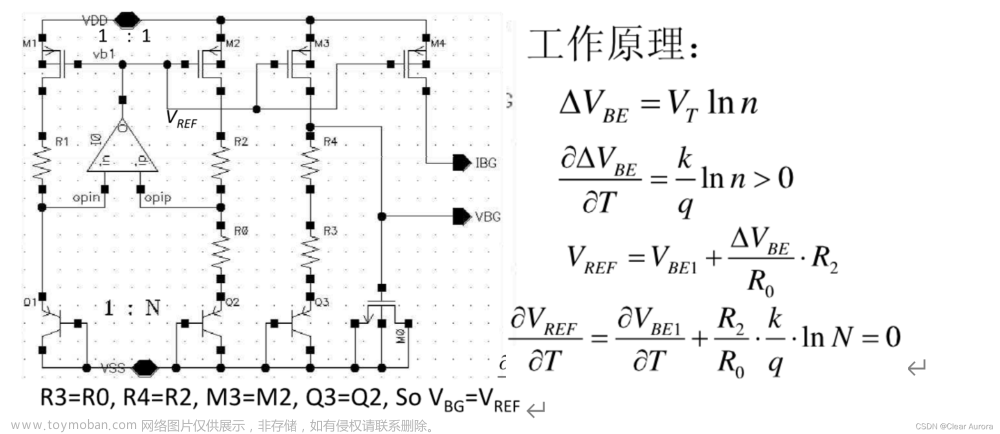

RC、LC反馈振荡器的最大区别是振幅的稳定机理,LC振荡器利用器件的非线性稳幅,但RC振荡器不允许有源器件进入非线性区,若器件进入非线性区后RC负反馈的效果就会减小,电路振荡不稳,输出波形会严重失真。因此,实际应用中RC反馈振荡器常采用可变增益或限幅电路进行稳幅。如下图所示,列出常用RC反馈网络的幅频特性:

RC网络特性示意图

由上图可见,RC网络可以有效控制交流信号的相移,将之应用到振荡回路中的反馈网络,可以使环路满足振荡所需的相应条件而实现振荡,实际电路中应用最广泛的就是文氏电桥振荡器,是利用RC串并联实现的振荡电路,如下图所示:

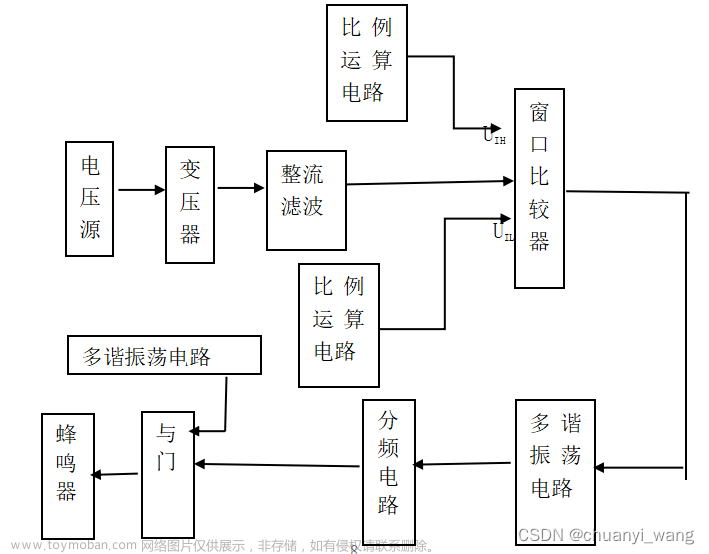

文氏电桥振荡器的基本电路组态

如上图所示,该组态是由运算放大器以及正负两个反馈网络构成。R1、C1、R2、C2组成RC选频网络作为振荡器的正反馈网络,使得电路获得相位条件。RF1、RF2组成负反馈回路使电路满足一定的幅度条件,正负反馈网络构成了一个电桥。

文氏电桥振荡器

文氏电桥振荡器的原理,说白了就是正反馈网络R1、R2、C1、C2是带通网络,增益和信号频率相关,负反馈网络RF1、RF2是全通网络,增益为常数。正反馈具有带通特性,若将参数计算成使得正反馈网络在幅频峰值点的幅度大于负反馈网络,那么电路就会形成振荡,如下图所示:

正负反馈网络关系示意图

为方便计算,通常取R1=R2、C1=C2,ω0=1/RC,那么正反馈网络传递函数:

当ω=ω0时,B+达到最大值1/3,电路的反馈系数为:

因振荡器的幅度条件是AB≥1,那么要求:

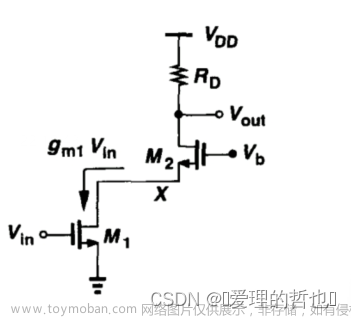

因运算放大器的开环放大倍数A是一个很大的数值,很难通过精确计算或手动调节来满足上述反馈条件,但在负反馈回路上通过添加非线性器件控制其输出幅度更容易实现,使得正负反馈几乎相等,振荡器会输出失真系数很小的正弦波。对于振荡频率很低的电路,要求负反馈网络的时间常数远大于信号周期,这样振荡波形就不会影响负反馈网络的非线性器件。实际应用原理图如下图所示:

实际应用原理图

图中常采用一个P沟道JFET替代电桥中的RF1,使JFET的漏源电阻受控于振荡器的输出幅度就可以实现输出的良好振荡,图中D1用作输出信号的峰值检波,稳压管D2决定了振荡器的输出幅度。为使输出波形良好,要求负反馈网络的时间常数远远大于振荡周期。

另外,整理了一些电子工程类的资料,分享给大家,目前有模拟电路、单片机、C语言、PCB设计、电源相关、FPGA、EMC、物联网、Linux相关学习资料,还有针对大学生的资料包,后续还会有更多资料分享给大家,助力大家学习,成就梦想~文章来源:https://www.toymoban.com/news/detail-405365.html

博主福利:免费分享电子工程类学习资料~https://mp.weixin.qq.com/mp/appmsgalbum?__biz=MzkzOTM5NTE0OQ==&action=getalbum&album_id=2532293941282209792#wechat_redirect文章来源地址https://www.toymoban.com/news/detail-405365.html

到了这里,关于模拟电路设计(17)---典型RC正弦波振荡器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!