一、PLL原理

锁相环,即是一种实现将输入的频率fin放大成所需要的频率fout的结构,例如我们IC中的晶振只能达到100M,但是工作的clock需要500M,这个时候就可以利用PLL实现频率的增大(倍频)。是IC中很重要的一个部分。PLL可用于Reduce EMI。

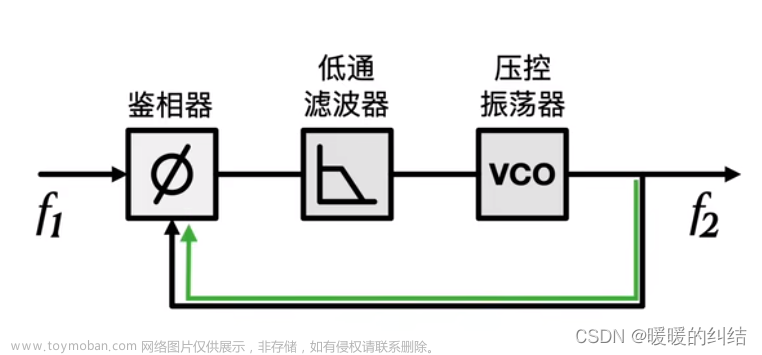

锁相环的结构如图所示,主要由3个部分组成:

1、 PFD:由D触发器和and门组成,对比Fre和Fout的相位和频率,产生up和down信号。

2、 CP和LPF:本质上是两个MOS开关,利用UP和Down信号去对电容充电或者放电,以达到Vc电压的增大与减小。

3、 VCO,产生方波的源头。N个反相器组成,利用延时产生信号。Vc越大,反应时间越快,频率越大。

最终实现了Fin/N=Fout/M

二、PLL的频宽

增益:

一般通稱之 PLL 頻寬即為上图所計算之公式 w-3dB 且正比於 ICPRKVCO

頻寬之物理意義即為 PLL 追輸入的能力及行為 。當頻寬越大即代表追的能力越強且輸出越容易變化,反之亦然。若 PLL 輸出的頻率可以被越快的調整,等效於越容易追輸入的訊號,而 VCO 的輸出頻率便由 ICPRKVCO 來控制, ICP 跟 R 越大,便代表輸入 VCO 的控制電壓 VC 的變化可以越大,對應 VCO 輸出的頻率範圍也因此變大,同理 KVCO 也有同樣的效果

而對應用上來說,不同的應用便需有不同的最佳頻寬設定,舉幾個例來說:

對Tx應用來說,其頻率要越穩越好,PLL的頻寬便希望小一些

對Rx來說追的能力要強,頻寬便要設大一些,才能保證其接受能力。

有些應用需要在限定時間內要追到,頻寬也要設足夠大,才會追的快

三、M.NPLL和N.FPLL

IC上常用的PLL架构有两种:M.NPLL、N.FPLL

3.1M.NPLL

M.NPLL是在原有的PLL架构上增加了phase swallow的部分,其中,

Phase shifter:产生8组不同相位的方波,排列组合形成7/8或者9/8的Fout,在1/8之间跳动。SDM是对其做微调,12个bit。例如,Offset=2e11,代表在两个cycle做一个phase swallow down,内部的一些处理可以让它实现比1/8更小的调整。

3.2N.FPLL

N.FPLL就是将phase swallow 换成phase interpolator,它是先将Fout分频后再进行处理,因为在更低的频率做处理的话,功耗更低,精度更准。PI其实就是对fout做一个phase delay,SDM的输入是clock,PI,N,然后经过数字模块处理后又输出给PI和N。待会会专门有个地方讲SDM的作用以及它的调整是怎么实现的。

PI是电流驱动的,PI的电流与VCO频率范围有关,正比。

文章来源:https://www.toymoban.com/news/detail-405499.html

文章来源:https://www.toymoban.com/news/detail-405499.html

3.2.2 SDM

文章来源地址https://www.toymoban.com/news/detail-405499.html

文章来源地址https://www.toymoban.com/news/detail-405499.html

到了这里,关于PLL锁相环知识的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!