一、安装INCISIVE

想进行AMS仿真首先需要安装INCISIVE(网上很多人管这个叫安装IUS,我也不知大它俩什么关系,hhh)。INCISIVE不是cadence virtuoso自带的,需要额外安装,我安装时候参考的这篇安装教程:https://blog.csdn.net/YYP_8020/article/details/107252366

我已经安装的virtuoso是IC617和MMSIM151,因此我就选择了上面这篇安装教程安装INCISIVE151。我当时在找安装教程时,网上说INCISIVE版本相对于已安装的virtuoso太老是不行的。

在安完INCISIVE151后,还要在InstallScape上用Configure功能再重新设置IC,实现连接IC和INCISIVE,具体方法我参考的是https://www.jianshu.com/p/c49b798f1baf和

https://bbs.eetop.cn/thread-479940-1-1.html

二、报错ERROR (SFE-23): “analog/input.scs” 13: The instance M0' is referencing an undefined model or subcircuit,nch3’. Either include the file containing the definition of nch3', or definench3’ before running the simulation.

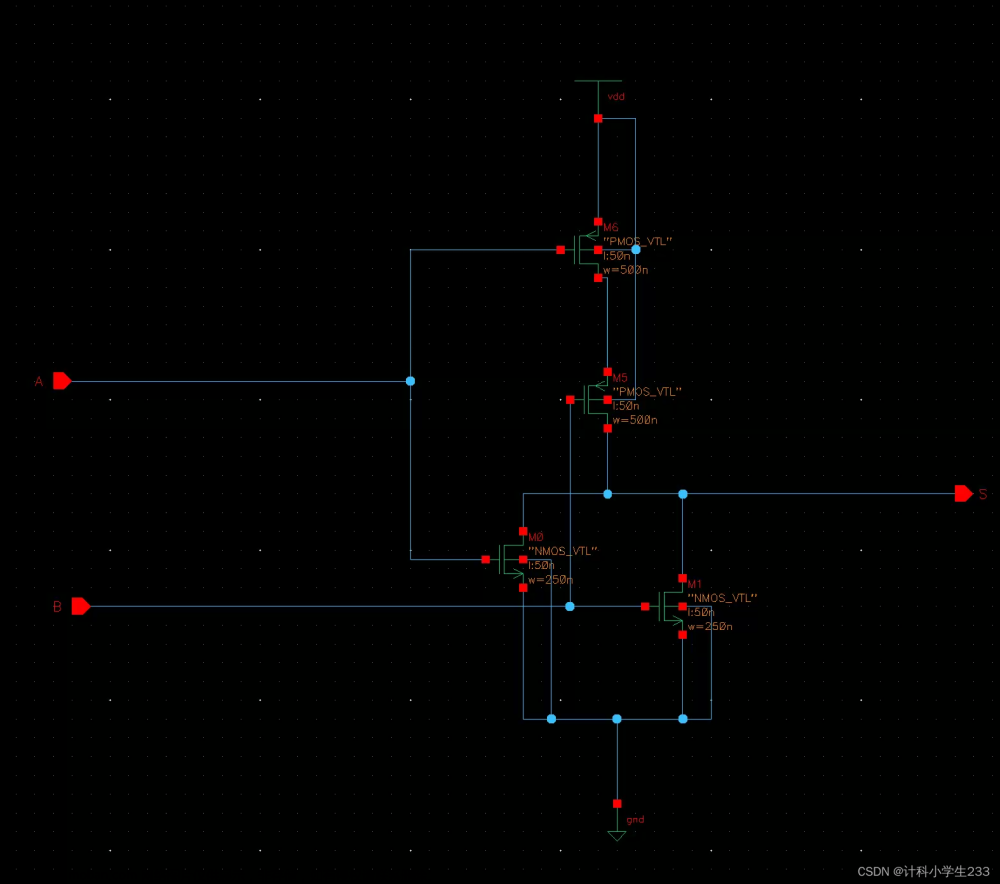

安装完INCISIVE并配置好IC之后就可以仿真了。具体步骤我参考的是https://blog.csdn.net/mymatin1004/article/details/98804521。我按这个教程走遇到了几个报错,把这几个报错都解决了就仿真通过了。我当时搭建的电路如下:

gen是我按那个教程编写的数字模块,M0则是我从网上下载安装的tsmc18rf库里的nmos。

我点击仿真运行图标后,遇到的第一个报错是:

ERROR (SFE-23): “analog/input.scs” 13: The instance ‘M0’ is referencing an undefined model or subcircuit, ‘nch3’. Either include the file containing the definition of ‘nch3’, or define ‘nch3’ before running the simulation.

大概就是说没有认出来M0这个nmos是什么。

解决方法是:

点击Setup->Model Libraries

出现如下界面

点击click here to add model file,添加tsmc18rf的.scs文件

我的tsmc18rf库的.scs文件叫rf018.scs,在/tsmc18rf_1P6M/models/spectre文件夹下,/tsmc18rf_1P6M是我的工艺库文件夹。

然后点击选择section

我这里使用的M0是属于nch3,在tt_3v、ff_3v、fs_3v、sf_3v、ss_3v中有,具体可以查看rf018.scs的内容,里面应该会写哪些器件在哪些section中

tt、ff、fs、sf、ss代表的是工艺角,我这里就选择标准工艺角tt_3v。之后点击ok。再仿真,就不报这个错了。

实际上,我在普通仿真的时候,.scs都自动添加进来了,不知道为什么AMS仿真就要自己手动添加。(因此如果找不到.scs文件,可以看一下普通仿真时Setup->Model Libraries里面添加的.scs路径是什么,把相同的.scs手动添加到AMS仿真的Setup->Model Libraries里并选好section即可)

三、报错ncelab: *E,CUVNCM (./netlist.vams,26|17): No connection module found:Need an input port of discrete discipline logic, and an output port of continuous discipline electrical, at instance test_gen.I0.

这个报错网上说是缺少connectlib库,好像就是负责数字电路部分和模拟电路部分连接。解决方法是找到安装的INCISIVE路径,如图

在这个文件夹下找到/INCISIVE151/tools/affirma_ams/etc/connectLib,这个就是需要的链接库

接着就在virtuoso操作界面新建这个库就行,名字起connectLib,路径就是connectLib文件夹的路径,technology file我选的“Do not need process information”。点击ok。

添加connectLib库也可以直接手动在工程目录下的cds.lib添加一句DEFINE connectLib XXXXX (XXXXX为connectLib所在目录)

之后就可以再library manager中看到connectLib被添加进来了,里面有好多cell

接着回到仿真界面,点击setup->connect rules/ie setup

在这里选择需要的connect rules,

具体选择哪个connect rules可以查看/INCISIVE151/tools/affirma_ams/etc/connectLib下的readme文件,里面有各个connect rules的解释,我用的是3v电源电压,因此选了Connectrules_3V_full_fast

选好之后,点击add再点ok就好了。

再运行AMS仿真就不报错了。

四、报错信息如下

ld: BFD (GNU Binutils) 2.20 internal error, aborting at …/…/binutils-2.20/bfd/reloc.c line 446 in bfd_get_reloc_size

ld: Please report this bug.

collect2: ld returned 1 exit status

gnumake: *** [obj/optimize/5.0/libahdlcmi_connectLib__L2E_2__module__0x10000001_behavioral.so] Error 1

网上说这个是gcc版本问题(毕竟virtuoso是原本在centos、redhet上运行,放到Ubuntu上真的让它好不适应,hhh)

解决方法:

找到INCISIVE安装目录下的INCISIVE151/tools.lnx86/cdsgcc/gcc文件夹,里面有4.1和4.4两个文件夹

两个里面都有bin/gcc文件,把这两个gcc文件改个名备份,分别在终端执行sudo ln -s /usr/bin/gcc ./gcc,重新建立名为gcc的软连接,我也不知道仿真时用的是4.1还是4.4里面的bin/gcc,就两个都改了。

完成之后,再运行AMS仿真就不报错了。文章来源:https://www.toymoban.com/news/detail-406390.html

五、总结

这些就是我在cadence virtuoso进行AMS仿真时踩的坑,本人比较小白,真的是花了好长时间才跑通AMS仿真,肯请大家斧正。文章来源地址https://www.toymoban.com/news/detail-406390.html

到了这里,关于cadence virtuoso进行AMS仿真踩坑记录和解决方法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!