日常·唠嗑

同上一篇文章术语:Xilinx及Altera FPGA 配置名词区分,本篇文章也是短文,简述Altera FPGA芯片的管脚,供FPGA同行快速查阅信息。如果需要细入研究,可以网上检索看看,文章很多,写的也很详细。也可以参考官方配置文档(其实网上很多文章都是翻译官方文档,要想深入研究建议多看官方文档)

1、配置管脚

| Pin | 简述 |

|---|---|

| MSEL[2:0] | 用于选择配置模式,比如AS、PS等 |

| DATA0 | FPGA串行数据输入,连接到配置器件的串行数据输出管脚 |

| DCLK | FPGA串行时钟输出,为配置器件提供串行时钟 |

| nCSO | (I/O)FPGA片选信号输出,连接到配置器件的nCS管脚 |

| ASDO | (I/O)FPGA串行数据输出,连接到配置器件的ASDI管脚 |

| nCEO | 下载链期间始能输出。在一条下载链中,当第一个器件配置完成后,此信号将始能下一个器件开始进行配置。下载链上最后一个器件的nCEO悬空 |

| nCE | 下载链器件始能输入,连接到上一个器件的nCEO,下载链的最后一个器件nCE接地 |

| nCNFIG | 用户模式配置起始信号 |

| nSTATUS | 配置状态信号 |

| CONF_DONE | 配置结束信号 |

| Pin | 简述 |

|---|---|

| INIT_DONE | 该引脚使能后,从低到高的跳跃表示FPGA已进入用户模式。如果该引脚使能,则配置完成后不能作为I/O使用 |

| CLKUSR | 当(CLKUSR)选项打开时,该引脚只能用作用户提供的初始化时钟输入引脚 |

| CRC_ERROR | 当选择错误CRC电路时,此引脚用作CRC_ERROR引脚,如果不使用,则默认为 I/O |

| DEV_CLRn | 如果选择了(DEV_CLRn)函数,该引脚被设置为低电平以清除所有寄存器。也可用作 I/O |

| DEV_OE | 可以用作I/o全局使能引脚,如果这个引脚低,所有I/ OS进入三种状态,也可以用作 I/O |

2、电源管脚

| Pin | 简述 |

|---|---|

| VCCINT | 内核电压。130nm为1.5V,90nm为1.2V |

| VCCIO | 端口电压。一般为3.3V,还可以支持多种电压,5V、1.8V、1.5V |

| VREF | 参考电压 |

| GND | 信号地 |

这里做个简单描述

FPGA通常需要两个电压才能运行:一个是“核心电压”,另一个是“IO电压”。每个电压通过独立的电源引脚来提供。

内核电压(这里简称VCCINT)是用来给FPGA内部的逻辑门和触发器上的电压。该电压随着FPGA的发展从5v、3.3v、2.5v、1.8v、1.5v变的越来越低。核心电压是固定的。(根据所用FPGA的模式来确定)。IO电压(简称VCCIO)是用于FPGA的IO模块(同IO引脚)上的电压。该电压应该与其它连接到FPGA上的器件的电压匹配。

实际上,FPGA器件本身是允许VCCINT和VCCIO相同的(比如VCCINT和VCCIO两种引脚可以被连接在一起)。但是FPGA设计是面向低电压内核和高电压IO的,所以两种电压一般是不相同的。

命名

内部电压Xilinx简称VCC,Altera简称VCCINT;IO电压Xilinx简称VCCO,而Altera简称VCCIO。

3、时钟管脚

| Pin | 简述 |

|---|---|

| VCC_PLL | PLL管脚电压,直接连VCCIO |

| VCCA_PLL | PLL模拟电压,截止通过滤波器接到VCCINT上 |

| GNDA_PLL | PLL模拟地 |

| GNDD_PLL | PLL数字地 |

| CLK[n] | PLL时钟输入 |

| PLL[n]_OUT | PLL时钟输出 |

4、特殊管脚

| Pin | 简述 |

|---|---|

| VCCPD | 用于寻则驱动 |

| VCCSEL | 用于控制配置管脚和PLL相关的输入缓冲电压 |

| PROSEL | 上电复位选项 |

| NIOPULLUP | 用于控制配置时所使用的用户I/O的内部上拉电阻是否工作 |

| TEMPDIODEN | 用于关联温度敏感二极管 |

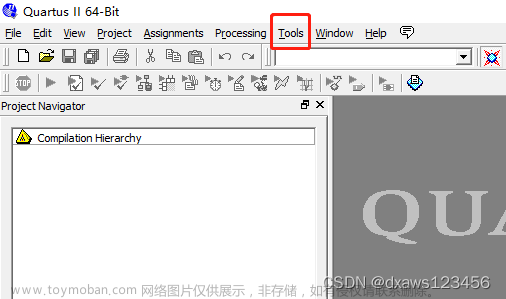

5、Altera 芯片管脚

给两个图,供读者参考。

文章来源:https://www.toymoban.com/news/detail-407184.html

文章来源:https://www.toymoban.com/news/detail-407184.html

参考文献:

geekite:FPGA芯片管脚解释

cl1217982730:FPGA的引脚VCCINT 、VCCIO VCCA文章来源地址https://www.toymoban.com/news/detail-407184.html

到了这里,关于零基础学FPGA(七):Altera FPGA管脚简述的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!