一、实验目的:

按照规则字写存储器,编写实验程序,将N个数写入SRAM的某段空间中,查看该存储空间,检测写入是否正确。

二、实验内容与要求:

按照规则字写存储器,编写实验程序,将0000H~000FH 共16个数写入SRAM的从0000H起始的一段空间中,然后通过系统命令查看该存储空间,检测写入数据是否正确。

三、实验步骤:

1.连接线路。

2.编写实验程序,经编译、链接无误后装入系统。

3.先运行程序,待程序运行停止。

4.通过D命令查看写入存储器中的数据,输入D8000: 0000并回车。

这里可以修改一下程序,将其改成其他的值,在memory中的Address输入查看数据。

5.改变实验程序,按非规则字写存储器。给SI寄存器赋奇地址数,MOV SI,0001H即为非规则字写存储器。

6.改变实验程序,按字节方式写存储器。

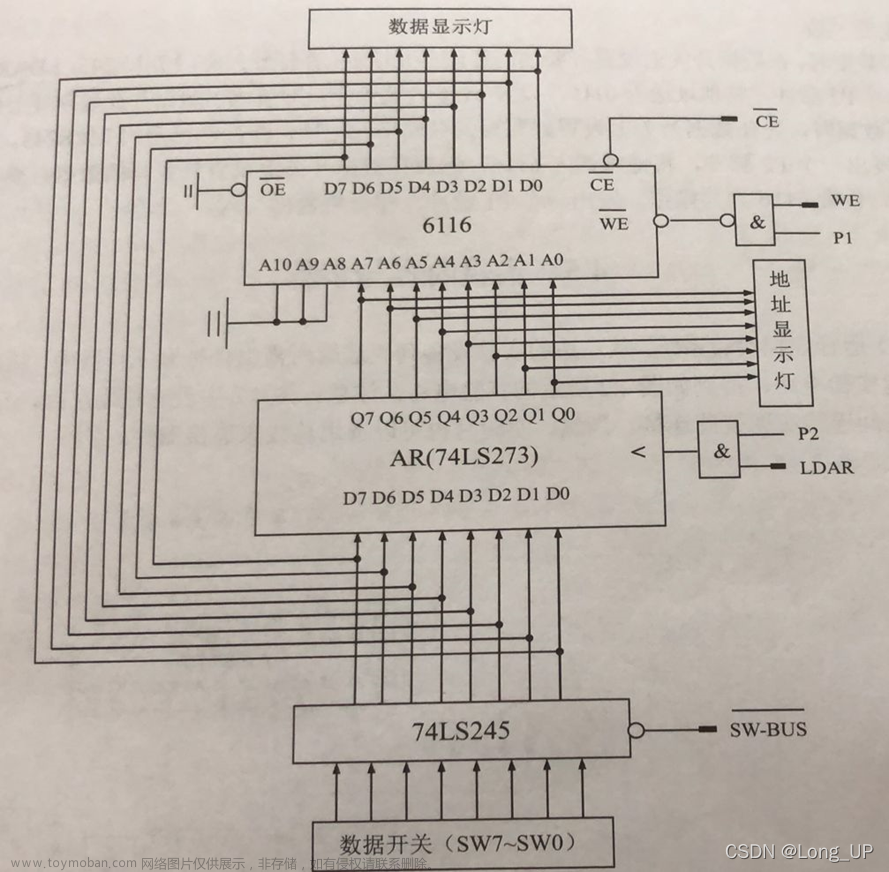

四、电路连接

五、代码设计与分析

这里只挑重要的代码进行分析。完整代码见后。

1.按非规则字写存储器

规则字是低位地址为奇数,否者是非规则字,非规则字读取需要两个周期,而规则字只需要一个周期。一个字在存储器中按字节存储,若低地址为偶数,高地址为奇数,则为规则字。相反,若低地址为奇数,高地址为偶数,则为非规则字。

AA0: MOV SI,0001H;数据首地址8000:0001 si是偏移地址,01是非规则字

MOV CX, 0010H;CX是计数存储器10H=16D

MOV AX,0000H;AX从0开始2.按字节写存储器

字节(Byte)是计算机信息技术用于计量存储容量和传输容量的一种计量单位,一个字节等于8位二进制数,在UTF-8编码中,一个英文字符等于一个字节。

AA1:MOV [SI], AX

INC AX;

INC SI;SI只加一个字节

LOOP AA1;CX不等于0需要循环六、实验现象

(1)查看写入存储器中的数据,可以看到存储器中的数据,为0000、0001、0002、.、000E共16个字,结果如下:

图4 按规则字写存储器

可见各个数被存放在偶地址单元中。

(2)按非规则字写存储器,结果如下:

图5 按非规则字写存储器

可见各个数被存放在奇地址单元中。

(3)按字节方式写存储器,结果如下:

图6 按字节方式写存储器

可见00、01…0F已紧凑地放到了每个存储单元。

七、源代码

1)扩展存储器实验,访问16位存储器,将16个数写入

SSTACK SEGMENT STACK

DW 32 DUP(?)

SSTACK ENDS

CODE SEGMENT

START PROC FAR

ASSUME CS:CODE

MOV AX, 9000H ; 存储器扩展空间段地址

MOV DS, AX

AA0: MOV SI, 0000H ; 数据首地址

MOV CX, 0010H

MOV AX, 0000H

AA1: MOV [SI], AX

INC AX

INC SI

INC SI

LOOP AA1

MOV AX,4C00H

INT 21H ;程序终止

START ENDP

CODE ENDS

END START

2.改变实验程序,按非规则字写存储器文章来源:https://www.toymoban.com/news/detail-407712.html

SSTACK SEGMENT STACK

DW 32 DUP(?)

SSTACK ENDS

CODE SEGMENT

START PROC FAR

ASSUME CS:CODE

MOV AX, 9000H ; 存储器扩展空间段地址

MOV DS, AX

AA0: MOV SI, 0001H ; 数据首地址

MOV CX, 0010H

MOV AX, 0000H

AA1: MOV [SI], AX

INC AX

INC SI

INC SI

LOOP AA1

MOV AX,4C00H

INT 21H ;程序终止

START ENDP

CODE ENDS

END START

3.改变实验程序,按字节方式写存储器文章来源地址https://www.toymoban.com/news/detail-407712.html

SSTACK SEGMENT STACK

DW 32 DUP(?)

SSTACK ENDS

CODE SEGMENT

START PROC FAR

ASSUME CS:CODE

MOV AX, 8000H ; 存储器扩展空间段地址

MOV DS, AX

AA0: MOV SI, 0000H ; 数据首地址

MOV CX, 0010H

MOV AX, 0000H

AA1: MOV [SI], AX

INC AX

INC SI

LOOP AA1

MOV AX,4C00H

INT 21H ;程序终止

START ENDP

CODE ENDS

END START到了这里,关于静态存储器扩展实验的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!