前言

在初学数字电路时,经常在正负逻辑、高低电平有效的符号的理解和使用上产生混乱,本文将从逻辑代数和码制的原理出发进行解释。

—>直接看结论跳转至总结部分。

一、码制的理解

所谓码制,通俗的理解就是将一些事件进行编码,也就是命名。在数字电路中,有两个重要的量——高电平和低电平,可以用逻辑代数中0/1编码。有以下码制:

- 正逻辑:高电平为1;低电平为0

- 负逻辑:高电平为0;低电平为1

二、码制与逻辑代数与数字电路

对这些关系的理解是充分了解数电的基础,需要明确如下几点:

- 在数字电路中,逻辑代数变量只可以取0/1两个值,0和1表示两个对立的事件,并没有对应的解释。逻辑代数的运算是独立的,与0/1赋予的意义没有任何关系。

- 逻辑代数基本运算有“与或非”三种,对应数字电路中用三种符号表示:

与门

与门 或门

或门 非门

非门 - 其中每一种“门”对应了一种逻辑代数的基本运算,即一幅真值表。

总结:一种逻辑运算(=真值表)=对实际电路在一种码制下的描述

举例解释,如果一种实际电路所实现的功能为:

在正逻辑和负逻辑的码制下分别为:

而由第3点知,与门对应着与运算,它的真值表如下:

救命…与门真值表Y列错了

所以在正逻辑码制下,与门(即与运算)可以描述功能如上表的实际电路;而在负逻辑码制下,或门(即或运算)可以描述如上表的实际电路。

得出:与门=与运算(=与运算真值表)=正逻辑下对一种功能的实际电路的描述。

总结:逻辑电路图即在规定的一种码制之下,运用逻辑代数运算得到最终的编码,再将编码对应到L/H电平的一种描述方式,相当于逻辑函数的直观形式,是一系列的运算。

可知,同一个功能的电路,在两种码制(正负逻辑)下,所对应的逻辑运算是不同的;同一个逻辑运算,在两种码制(正负逻辑)下,所对应的实际电路功能是不同的。

所以在关于逻辑电路图的使用时,避免带入H/L电平进行推演,而应该只带入变量值0/1。

三、正负逻辑转换与高低电平有效

一、二部分介绍了逻辑电路图的本质和误区。有了这些铺垫,现在来到第三板块,高低电平有效和正负逻辑转换。

- 高电平有效在实际电路中的意义是:不加高电平为低电平,加上高电平为高电平。在电路中传递的是高电平信号。

- 低电平有效在实际电路中的意义是:不加低电平为高电平,加上低电平为低电平。在电路中传递的是低电平信号。

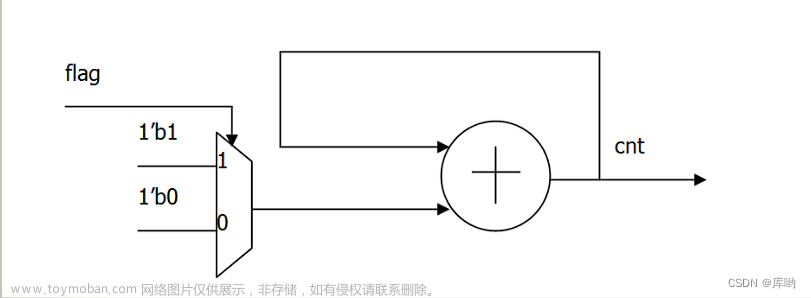

想要在电路中实现与运算的功能,首先需要对与运算进行编码,由此就有正逻辑和负逻辑两种码制,实际电路所需要满足的功能分别如下图所示(注明:输入采用正负逻辑,输出采用正逻辑):

再利用高低电平有效的观念,对两种实际电路产生改进如下图所示(括号内为所加的电压):

由横向和纵向对应观察可知,在AB端做相同动作时(即在相同端加相应的有效电压),高电平有效对应着输入正逻辑,低电平有效对应着输入负逻辑。

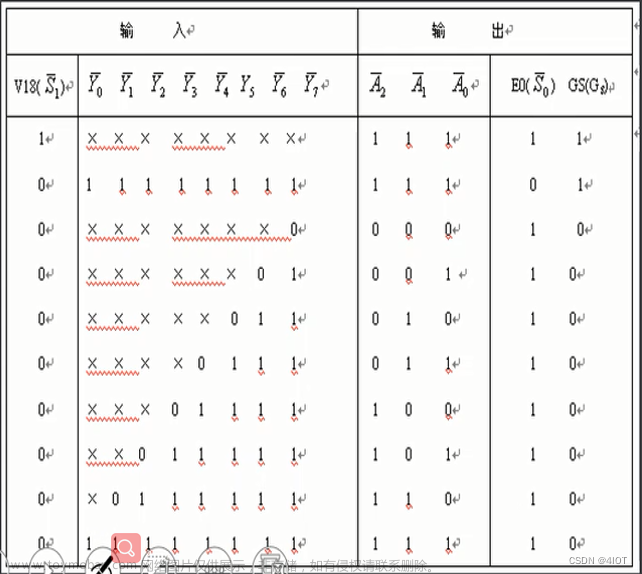

然而在设计实际电路时,为了避免逻辑混乱,通常采用一套码制,即整个都用正逻辑或整个都用负逻辑。但是有的已经设计完成的实际电路模块是已经采用了低电平有效输入的,即满足的是负逻辑输入,比如高电有效与门和低电平有效与门的区分(它们的功能都是与运算,但是是在不同的码值制之下)。在逻辑代数中的与运算,在数字电路的实现中有一般与门(高电平有效与门与之码制相同)和低电平有效与门两种,用两种符号进行表示。

由于我们一般在逻辑电路图中对此有以下的处理方式:

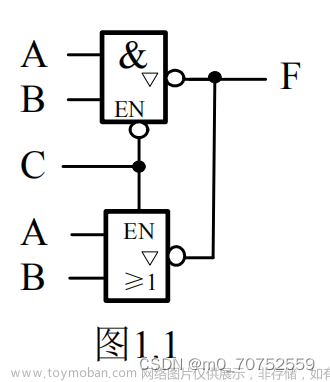

- 低电平有效的与门在逻辑电路图的表示中,会在与门符号前加上两个圈。这两个小圈,表示这是一个低电平有效的与门,即一个输入是负逻辑的与门。如下图:

PS:至于为什么用A’和B’下面一张图里有说明 - 在一幅逻辑电路图中,需要明确使用正负逻辑的哪一种,如果混用且不加以转换,就会导致错误。在板块二我们得出结论:

逻辑电路图是一系列的运算。在关于逻辑电路图的使用时,避免带入H/L电平进行推演,而应该只带入变量值0/1文章来源:https://www.toymoban.com/news/detail-407831.html

如果都用正逻辑时,对于高电平有效与门输入00得到0结果为低电平,对低电平有效与门输入00得到1结果为高电平,导致错误。而列出负逻辑器件的真值表很麻烦,所以在混用时我们需要转换逻辑。

我们如何进行逻辑转换呢?一般我们习惯将负逻辑转换为正逻辑。由第1点我们提到,在输入负逻辑运算(低电平有效)前会加上小圈注明,这个小圈起到标志作用。而将这个小圈改写为非门时,就可以全部用正逻辑进行运算。理解起来很容易,负逻辑用1表示L,0表示H,取反(单纯对变量取反,不是对高低电平取反)就是0表示L,1表示H,正好符合正逻辑的输入,而输入本身就是正逻辑,所以就可以解决逻辑混乱的问题了。

举个小例子(THU教材): 文章来源地址https://www.toymoban.com/news/detail-407831.html

文章来源地址https://www.toymoban.com/news/detail-407831.html

总结

- 数字电路是用实际电路描述逻辑代数的运算。

- 同一种逻辑运算在不同的码制(正负逻辑)之下有不同的数字电路实现,其中高电平有效对应正逻辑,低电平有效对应负逻辑(PS:不过要看清是输入还是输出端)。简单点讲,实现的还是那个逻辑运算,但是实现过程H/L不同,对应的数字电路符号也不一样。

- 逻辑电路图其实就是用数字电路特有的符号描述实际电路的功能,进而反映对应的一系列逻辑运算。一幅逻辑电路图要明确用的是哪一种逻辑,一般采用正逻辑。

- 正逻辑下的逻辑电路遇到低电平有效的元件,要使用电平转换。将低电平有效元件的小圈改成非门即可。

到了这里,关于数字电路低电平有效逻辑和符号的理解的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!