1、锁相环:

锁相环是对接收到的信号进行处理,并从其中提取某个时钟的相位信息。锁相环由鉴相器、环路滤波器和压控振荡器组成。

锁相环原理图

锁相环原理图

鉴相器:

用来鉴别输入信号输入信号Ui与输出信号输出信号Uo之间的相位差相位差,并输出误差电压Ud。Ud 中的噪声噪声和干扰成分被低通性质的环路滤波器滤除,形成压控振荡器的控制电压Uc。Uc作用于压控振荡器的结果是把它的输出振荡频率fo拉向环路输入信号频率fi ,当二者相等时,环路被锁定,称为入锁。维持锁定的直流控制电压由鉴相器提供,因此鉴相器的两个输入信号间留有一定的相位差。

2、使用Quartus II 自带的IP核

第一步:新建一个工程,点击tools,再点击MegaWizard Plug-In Manager;

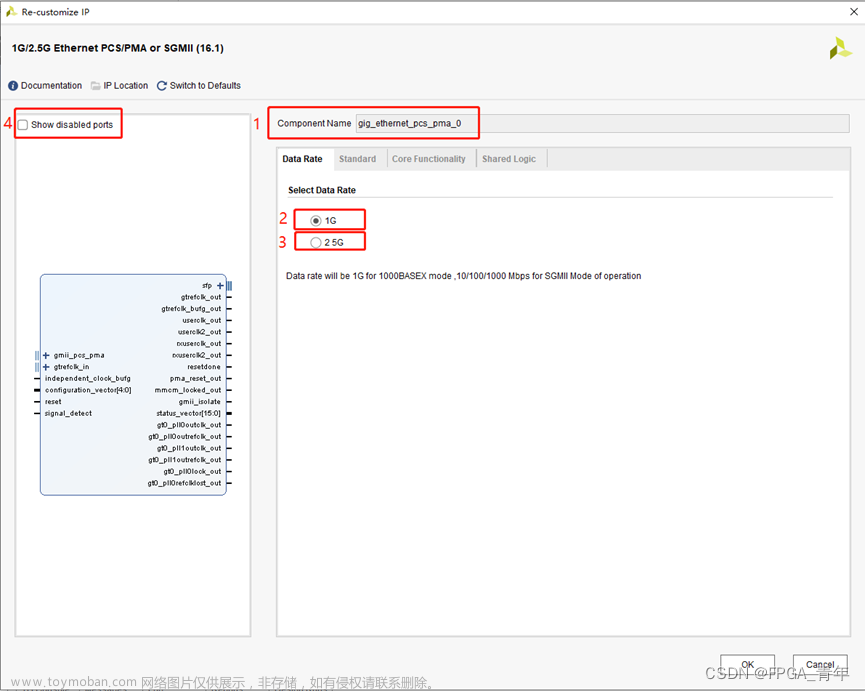

第二步:在弹出的对话框点击next,即:创建一个新的IP核,再到弹出的搜索框搜索altpll并选择第一个,并在右侧选择存储文件夹并命名,选择好后,点击next,如下:

第三步:继续点击next,直到出现如下页面,并设置参数如下:(根据自己实验所需依次设置参数),设置好参数,点击next,直到总结页面,点击finish;

生成的IP核文件如下:

文章来源:https://www.toymoban.com/news/detail-407938.html

文章来源:https://www.toymoban.com/news/detail-407938.html

然后新文件,编写顶层文件。文章来源地址https://www.toymoban.com/news/detail-407938.html

到了这里,关于FPGA之Quartus II 自带的IP核的使用(IP核仅自己学习,未完成)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!