本实验将实现音频模块和FPGA之间的数据通信,通过音频模块把麦克风输入的语音数据存储到SDRAM存储器里,再把音频数据发送给音频模块,从耳机接口进行语音的播放,从而实现录音和播放的功能。

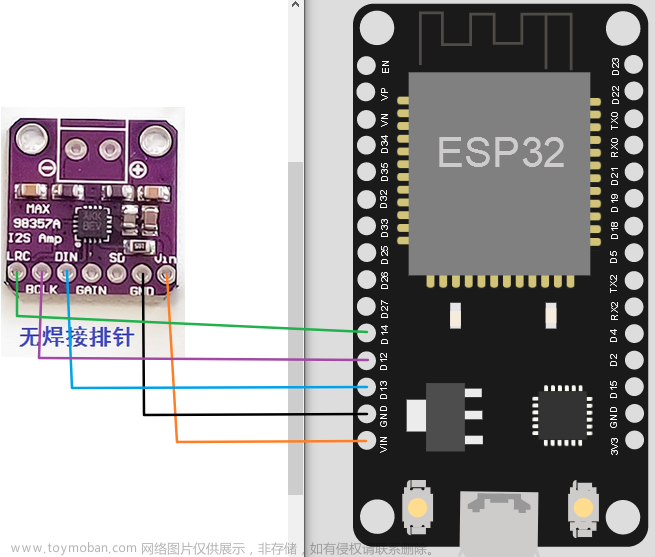

这里简单介绍一下音频模块AN831用到的音频编/解码芯片WM8731。该芯片在本设计中主要完成声音信号在采集和回放过程中的A/D和D/A转换功能。该芯片的ADC和DAC的采样频率为8KHZ到96KHZ可调,可转换的数据长度为16-32位可调。WM8731的内部有11个寄存器。该芯片的初始化以及工作时的工作状态和功能都是通过I2C总线方式对内部的这11个寄存器进行相应的配置来实现的。本设计中WM8731工作于主模式,采样频率设为48KHZ,转换的数据位长度为16位。WM8731的数字音频接口有5根引脚,分别为:BCLK(数字音频位时钟)、DACDAT(DAC数字音频数据输入)、DACLRC(DAC采样左/右声道信号)、ADCDAT(ADC数字音频信号输出)、ADCLRC(ADC采样左/右声道信号)。在本设计中FPGA为从设备,WM8731为主设备。ADCDAT、DACDAT、ADCLRC和DACLRC与位时钟BCLK同步,在每个BCLK的下降沿进行一次数据传输。在本系统中FPGA和WM8731的控制和数据通信将用到I2C和数据音频总线接口。FPGA通过I2C接口配置WM8731的寄存器,通过I2S总线接口来进行音频数据的通信。

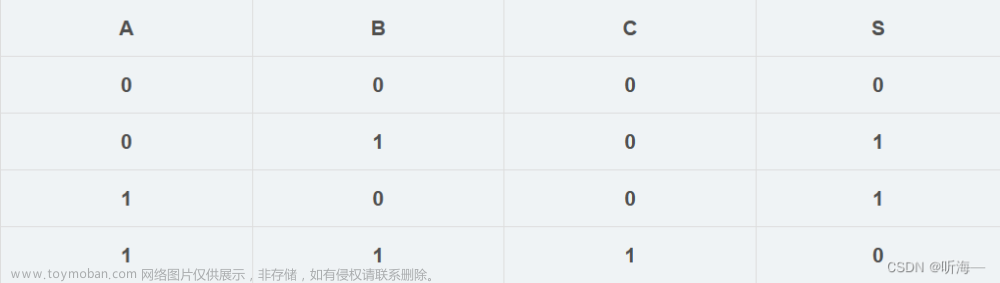

可以从时序图看出,数据被采样是在BCLK的上升沿(两个设备以某种通信协议通信,必须双方都遵从,如i2s,上升沿接受数据,下降沿发送数据,那么主从设备都是上升沿采样,下降沿发送),时序图中出现的1/fs为一个周期,完成了一次数据的收发(左右声道)。每一次收发数据的开始,从ADCLRC/DACLRC的上升沿开始,到下一个上升沿结束。

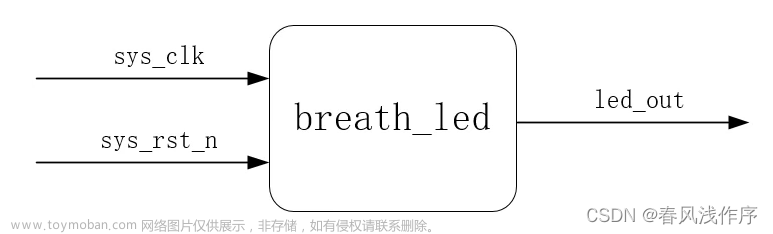

top

top

该模块主要用于通过I2S通信协议对WM8731音频芯片AD输出的数据进行采样(接收)以及将存储的数据发送给WM8731进行DA 。

由于SDRAM存储数据的mem_clk与FPGA内部的clk不同步,所以需要一个跨时域的数据交互,以便数据由CLK到MEM_CLK这个时域。

并输出给SDRAM控制器burst_data/burst_len/burst_addr。

Pll倍频输出的MEM_CLK走线

通过I2C配置WM8731

top.v

顶层设计可以由(Analysis&Synthesis中的Netlist Viewers RTL)即上面的顶层模块电路图看出具体设计。文章来源:https://www.toymoban.com/news/detail-409303.html

文章来源地址https://www.toymoban.com/news/detail-409303.html

到了这里,关于FPGA-音频模块开发(一)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!