写在前面

在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。

这是网站原文:http://asic-world.com/verilog/veritut.html

这是系列导航:Verilog教程系列文章导航

空白符(White Space)

空白符包括空格(blanks)、制表符(tabs)、换行符(newlines)和换页符(form feed)。这些字符在代码中一般被忽略(没有实际意义),除非它们用于分隔其他令牌。但是,空格和制表符在字符串中却很重要。

空白符可以是:

- 空格(Blank space)

- 制表符(Tab)

- 回车(Carriage return)

- 换行符(Newline)

- 换页符(Form-Feed)

来看一个空白符的例子。下面两段代码在功能上是一样的,但是一种是好的编码习惯,另一种是不好的编码习惯:

糟糕的代码:永远不要写这样的代码。这样的代码没有利用好空白符,代码的易读性很差。

module addbit(a,b,ci,sum,co);

input a,b,ci;output sum co;

wire a,b,ci,sum,co;endmodule良好的代码:这样的编码习惯很好。这样的代码非常好地利用了空白符,布局良好,看起来很舒服。

module addbit (

a,

b,

ci,

sum,

co);

input a;

input b;

input ci;

output sum;

output co;

wire a;

wire b;

wire ci;

wire sum;

wire co;

endmodule注释(Comment)

Verilog中的注释有两种方法:

- 单行注释以标记 // 开始并以回车结束;这种注释只能写在一行

- 多行注释以标记 /* 开始并以标记 */ 结束;这种注释可以跨行

来看一个例子:

/* 这是一个

多行注释

案例 */

module addbit (

a,

b,

ci,

sum,

co);

// 这是单行的注释: 输入端口

input a;

input b;

input ci;

// 这是单行的注释: 输出端口

output sum;

output co;

// 这是单行的注释: 数据类型

wire a;

wire b;

wire ci;

wire sum;

wire co;

endmodule大小写规则

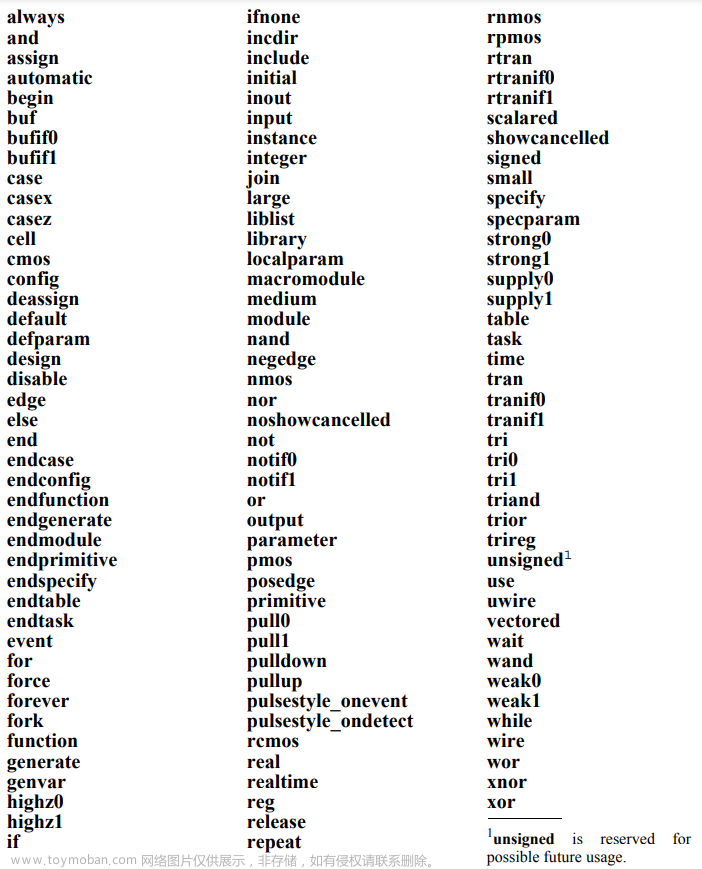

Verilog的大小写规则是这样的:

- 区分大小写

- 所有的关键字都是小写的

这是一个关于大小写的命名示例:

input // 这是关键字

wire // 这是关键字

WIRE // 这是一个自定义名称(这不是关键字)

Wire // 这是一个自定义名称(这不是关键字) 提示:永远都不要将 Verilog 的关键字用作自定义名称,即使大小写不同也不要用(尽管这是合法的,但容易出错)。

标识符

标识符用于为对象(例如寄存器、函数或模块等)提供名称,以便可以从代码中的其他位置引用它。

- 标识符必须以字母或下划线 ( az AZ _ )开头

- 标识符可以包含字母、数字、下划线和美元符号 ( az AZ 0-9 _ $ )

- 标识符最长可达 1024 个字符。

这些是合法的标识符:

- data_input mu

- clk_input my$clk

- i386 A

转义字符(Escaped Identifiers)

Verilog 语言允许通过转义字符在标识符中使用任何字符。转义字符提供了一种在标识符中包含任何可打印 ASCII 字符的方法(十进制值 33 到 126,或十六进制的 21 到 7E)。

- 转义标识符以反斜杠 (back slash,\) 开头

- 转义标识符以空白符终止(逗号、括号和分号等字符成为转义标识符的一部分,除非前面有空格)

- 要用空白符终止转义字符,否则标识符后面的字符将被视为其中的一部分

Verilog 不允许标识符以数字开头。所以如果您真的想使用以数字开头的标识符,请使用转义字符,如下所示。

//使用转义字符的字符串后必须有空格

module \1dff (

q, // Q output

\q~ , // Q_out output,注意空格

d, // D input

cl$k, // CLOCK input

\reset* // Reset input,注意空格

);

input d, cl$k, \reset* ;

output q, \q~ ;

endmodule Verilog 中的数字

您可以使用十进制、十六进制、八进制或二进制格式的常数。负数将以 2 的补码形式表示。问号 (?) 在数字中使用时与 z 的作用是等效的。

下划线 ( _ ) 在数字中的任何位置都是合法的(但作为第一个字符时会被忽略),其仅用来分隔数字以提高可阅读性。

整数(Integer )

Verilog 的整数规则是:

- 有符号整数(Sized )或无符号(unsized )整数 (无符号整数位宽为32)

- 二进制、八进制、十进制或十六进制

- 十六进制数字(a、b、c、d、e、f)不区分大小写

- 大小、进制和数值之间允许有空格

一般语法:<size>'<radix><value>;

下表是一些整数的表示示例:

| 整数 |

存储方式 |

备注 |

| 1 |

00000000000000000000000000000001 |

默认32位 |

| 8'hAA |

10101010 |

指定8位 |

| 6'b10_0011 |

100011 |

指定6位 |

| 'hF |

00000000000000000000000000001111 |

默认32位 |

Verilog 通过从右到左的方式来扩展 <value> 以填充指定的 <size>。

- 当 <size> 小于 <value> 时,<value> 的最左边的位被截断

- 当<size>大于<value>时,则根据<value>中最左边位的值填充最左边的位:

- 最左边的'0'或'1'用'0'填充;

- 最左边的'Z'用'Z'填充;

- 最左边的'X'用'X'填充

注: X代表未知,Z代表高阻抗,1代表逻辑高或1,0代表逻辑低或0。

了解了这些规则后,再来看一些关于整数的示例:

| 整数 |

存储方式 |

备注 |

| 6'hCA |

001010 |

CA原为1100_1010,但指定位宽为6,所以高两位被截断 |

| 6'hA |

001010 |

A原为1010,但指定位宽为6,所以高两位填充00 |

| 16'bZ |

ZZZZZZZZZZZZZZZZ |

全部用Z填充 |

| 8'bx |

xxxxxxxx |

全部用x填充 |

实数(Real)

关于实数的一些规则是:

- Verilog通过四舍五入将实数转换为整数

- 实数不能包含“Z”和“X”

- 实数可以用十进制或科学记数法来表示

- < value >.< value > (十进制)

- < mantissa >E< exponent > (科学技术法)

- 当用实数给整数赋值时,实数会四舍五入到最接近的整数

这是一些实数表示的例子:

| 实数 |

十进制表示 |

| 1.2 |

1.2 |

| 0.6 |

0.6 |

| 3.5E6 |

3500000.0 |

有符号数和无符号数(Signed and Unsigned Numbers)

Verilog 支持这两种类型的数字,但有一定的限制。不同于C语言,verilog没有用来表示一个数字是有符号整数还是无符号整数的 int 和 unint 数据类型。

任何没有负号( - )前缀的数都是正数。负数可以通过在常数前加减号(即负号 -)来指定,因此来成为有符号数。Verilog 在内部以 2 的补码格式表示负数。

这是一个数值描述的例子:

| 数字 |

描述 |

| 32'hDEAD_BEEF |

Unsigned or signed positive number |

| -14'h1234 |

Signed negative number |

下面的代码展示了Verilog是如何处理有符号和无符号数的:

module signed_number;

reg [31:0] a;

initial begin

a = 14'h1234;

$display ("Current Value of a = %h", a);

a = -14'h1234;

$display ("Current Value of a = %h", a);

a = 32'hDEAD_BEEF;

$display ("Current Value of a = %h", a);

a = -32'hDEAD_BEEF;

$display ("Current Value of a = %h", a);

#10 $finish;

end

endmodule

这是仿真的结果(负数展示的是2进制补码):

Current Value of a = 00001234

Current Value of a = ffffedcc

Current Value of a = deadbeef

Current Value of a = 21524111

数据类型

Verilog的数据类型有很多,一般可以分为两个主要的大类:

- 线网(Nets )----描述两个组件之间的连接

- 寄存器(Registers )---- 存储数据的变量

每个信号都有对应的数据类型:

- 显示声明(Explicitly declared):这就是在代码中的普通声明

- 隐式声明(Implicitly declared):没有直接在代码中的声明,默认是1位宽的wire类型

net类型下还有很多的子类型,如wire、tri、wand等,但是使用的最多的是wire类型,其他的类型一般很少使用,不多介绍。wire类型可以通俗地理解为一根电线,它被用来连接电路中的两个组件,主要起连接作用。

reg类型可以用来存储数据,在下一条赋值语句到来之前,其存储的值不会改变。同样的,reg是使用得最多的寄存器类型,其余的寄存器类型还有integer、time和real等。

字符串

字符串是用双引号括起来的字符序列,所有的字符都包含在一行中。在表达式和赋值中用作操作数的字符串被视为一系列8位 ASCII 值,每一个8位 ASCII 值代表一个字符。

要声明一个变量来存储字符串,请声明一个足够大的寄存器以容纳该变量。当变量大于保存赋值所需的值时,Verilog 会在赋值后用零填充左侧的内容。当变量小于保存赋值所需的值时,Verilog 会截断最高位的内容。

某些字符只有在前面加一个转义字符的时才能在字符串中使用。下表在右列中列出了这些字符,并在左列中列出了代表该字符的转义字符。

| 字符串 |

描述 |

| \n |

换行符 |

| \t |

制表符 |

| \\ |

反斜杠 |

| \" |

双引号 |

下面是一个打印字符串的例子:

module str();

// 声明一个可以容纳21个字符的便令

reg [8*21:0] str ;

initial begin

string = "This is sample string";

$display ("%s \n", str);

end

endmodule

这是打印的结果:文章来源:https://www.toymoban.com/news/detail-409352.html

This is sample string文章来源地址https://www.toymoban.com/news/detail-409352.html

- 📣您有任何问题,都可以在评论区和我交流📃!

- 📣本文由 孤独的单刀 原创,首发于CSDN平台🐵,博客主页:wuzhikai.blog.csdn.net

- 📣您的支持是我持续创作的最大动力!如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!

到了这里,关于ASIC-WORLD Verilog(4)基础语法上篇的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!