0. 前言

首先,先声明一下,我写这篇博客的时候我就是一个纯小白,实不相瞒,刚刚学了一天,哈哈哈,没错,你没看错,就是一天!!!主要是因为前天因为刷题和找工作的需要,需要熟悉VCS和Verdi的联合仿真(据说是很好用,随大流呗!!!),所以才会有接下来的一些相关博客,我准备把它搞成一个专栏,以便于后边有朋友需要,做个参考,话不多说,直接开干。

1. 概述

相信大家多多少少接触过一款或者多款EDA的相关软件吧,你比如Vivado,Quartus,它们都已经包含了RTL,编译,仿真,综合,看波形,烧板子等功能。那为什么不用这个呢?难道是公司有问题???哈哈,你想多了,公司可比我们学校学的东西超前十年到二十年不止吧,所以说,多向公司学学没毛病的。反观VCS和Verdi就很专一了,VCS专注于编译及仿真,Verdi专注于看波形。再就是VCS编译仿真速度极快,效率极高,为大家节约时间,Verdi看波形也十分方便debug,它支持信号追溯,无缝增加信号波形等功能。

2. 从“0”开始学习

环境: CentOS7

代码编写: Vim

编译仿真: VCS

波形查看: Verdi

关于虚拟机的安装请移步我的另一篇博客,传送门

关于VCS和Verdi相关EDA工具的安装可以评论区或者私聊我都可以获取的。

=============================================================================================

好了我们接着往下看===>

这里默认VCS和Verdi环境都已配好,配置环境参考我的博客,.bashrc文件的配置

2.1 进入虚拟机,选择“”打开终端

2.2 创建相关文件

2.2.1 通过linux命令创建相应的文件,这里我以计数器为例,需要创建Counter文件夹,

(注意的是,Linux传送门在这里,点击传送门)

$cd _Project/ # cd 文件夹名称

#下边的是我文件夹_Project里边的文件

# Counter

2.2.2 在Counter文件夹中创建3个文件夹

mkdir module tb verification # 创建3个文件,名字为module、tb、 verification

# 下边是结果

drwxrwxr-x. 2 ICer ICer 23 6月 29 17:43 module

drwxrwxr-x. 2 ICer ICer 27 6月 29 17:55 tb

drwxrwxr-x. 2 ICer ICer 39 6月 29 21:03 verification

2.2.3 在module中创建rtl代码

vim counter.v # 通过vim编辑器创建counter.v文件

# 对于相应的写代码过程可以参考vim的使用看看,等我有时间也写一篇关于vim使用的文章,根据大家的需要来吧,如果有需要评论区告诉我!!!

写完之后的代码:

1 module counter(

2 input clk,

3 input rst,

4 output reg [5:0] count

5 );

6

7 always @ (posedge clk or negedge rst) begin

8 if(!rst) begin

9 count <= 0;

10 end

11 else begin

12 count <= count + 1;

13 end

14 end

15 endmodule

2.2.4 在tb中创建测试代码

vim tb.sv # 通过vim创建tb.sv文件

写完之后的代码:

1 module tb_counter();

2

3 reg clk,rst;

4 wire [5:0] counter;

5

6 counter u1(clk,rst,counter);

7

8 always #(5) clk = ~clk;

9

10 initial begin

11 clk <= 0;

12 rst <= 0;

13 #20;

14 rst <= 1;

15 #50;

16 if(counter != 5)

17 $display("Failure 1: the counter should be 5 but it is %d",counter);

18 else

19 $display("You gotta the right result!");

20 $finish;

21 end

22

23 //.v file

24 //`ifdef FSDB

25 //initial begin

26 // $fsdbDumpfile("tb_counter.fsdb");

27 // $fsdbDumpvars;

28 //end

29 //`endif

30

31 //.sv file

32 initial begin

33 $fsdbDumpfile("tb.fsdb");

34 $fsdbDumpvars;

35 end

36 endmodule

2.2.5 在verification中file_list和脚本文件

# 这个文件可以不加后缀,主要作用就是组织一下前边的rtl代码和测试文件的路径,便于脚本文件调用

vim file_list

# 这个文件是个脚本文件,通过make指令调用(具体可以看看Makefile的使用,我这里有个文档资料,需要同样是私信或评论区留言即可)

#它的作用是统筹调度一切文件的运行顺序,是个老大哥

vim Makefile

写完之后的代码:

all: \

3 vcs \

4 verdi

5

6 #-------------------------------------------------------------------------------------------------------

7 # VCS

8 vcs :

9 vcs \

10 -f file_list \

11 -timescale=1ns/1ns \

12 -full64 -R +vc +v2k -sverilog -debug_access+all \

13 |tee vcs.log

14 #-------------------------------------------------------------------------------------------------------

# verdi

34

35 verdi :

36 verdi -sv -f file_list -ssf tb.fsdb &

37

38 #-------------------------------------------------------------------------------------------------------

39 clean :

40 rm -rf *~ core csrc simv* vc_hdrs.h ucli.key urg* *.log novas.* *.fsdb* verdiLog 64* DVEfiles *.vpd

41 rm -rf INCA_libs irun*

42 rm -rf modelsim.ini transcript work

2.3 万事俱备,只欠运行

2.3.1 运行vcs

$make vcs # 通过make指令调用Makefile运行vcs

运行结果:

图中标出来的是原有的,剩下的都是仿真生成的,恐怖不???哈哈哈,习惯就好了

2.3.2 运行verdi

make verdi # 通过make指令调用Makefile运行verdi

运行结果:

没有波形???

这里还需要一步,就是添加你想要观察的信号,看下图即可。

这不就完事了吗?怎么样,你学废了吗?

把学废了打在评论区!!!

2.4 事后的好习惯

看完波形之后,不是之前产生了很多文件啥的吗?你不得收拾收拾啊!吃完饭得收拾收拾,咋办?

别忘了Makefile中最后不是有个clean指令吗?干就完了!!!

make clean # 清理产生的文件

结果:

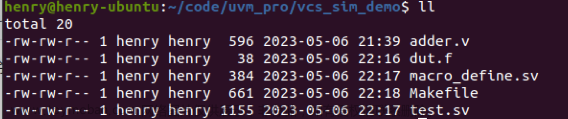

就剩下我们仿真之前的文件喽!!!

3. 总结

通过这一天的学习,你还真别说,vcs和verdi联合仿真还是真的好用啊,到这里,我学的远远不够,只是掌握了一点点小小的皮毛,还得不断地学习,参考他人的优点,希望大家共同学习,共同进步,如有错误,欢迎大家批评指正!!!

好了,完结撒花,多多三连,持续更新。文章来源:https://www.toymoban.com/news/detail-411213.html

=========================================================================

未完待续…文章来源地址https://www.toymoban.com/news/detail-411213.html

到了这里,关于【VCS+Verdi联合仿真】~ 以计数器为例的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!