前言

2023.4.11 继续学习STA,前面听的感觉好迷糊,先接着看,到时候回头再看一遍理解

2023.4.12 打卡

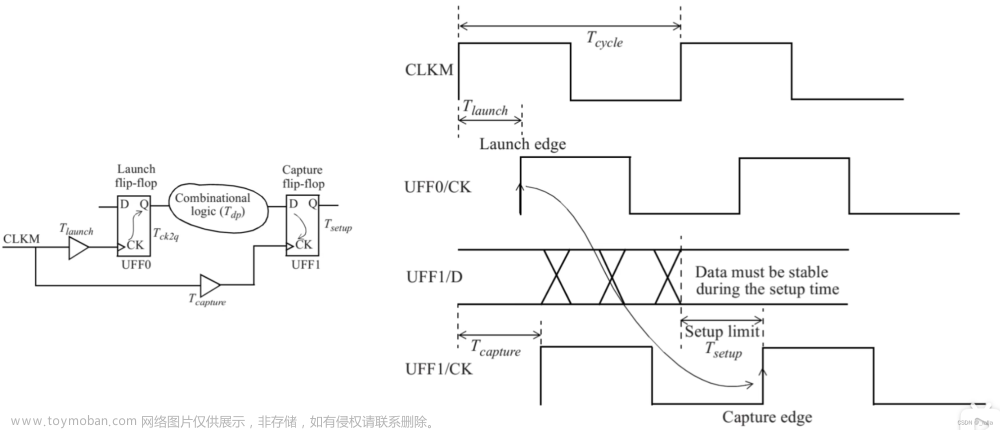

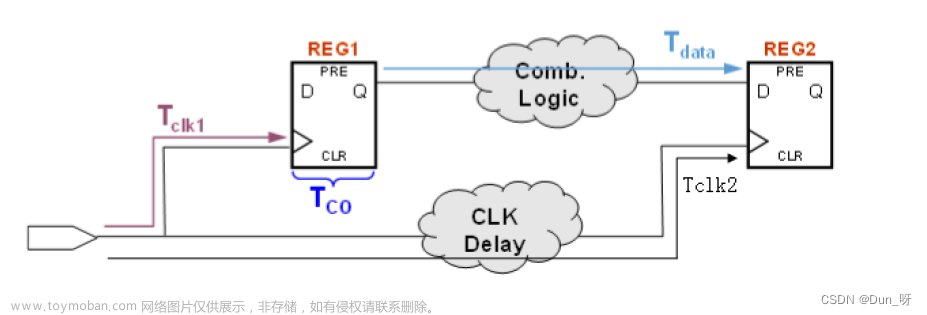

一、建立时间检查

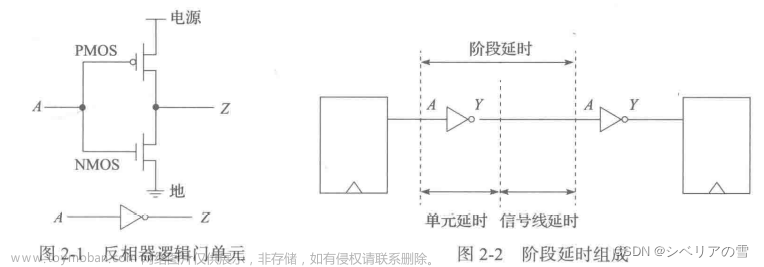

Tlaunch + Tcq + Tdp <= Tclk + Tcapture - Tsetup

- 时钟的发射和捕获延迟时间是很小的,Tcq和Tsu是工艺库决定的,是固定值。要想等式成立,要取左边的最大值来进行判断

建立时间违例的解决方法:

- 降低时钟频率,增加时钟周期(增加Tclk)

- 在launch cell路径增加缓冲器,让时钟晚点到来(增加clk skew)

- 组合逻辑优化或插入流水线,缩短关键路径(减小Tcomb)

- 选择器件延迟更小的触发器(减小Tcq和Tsu)

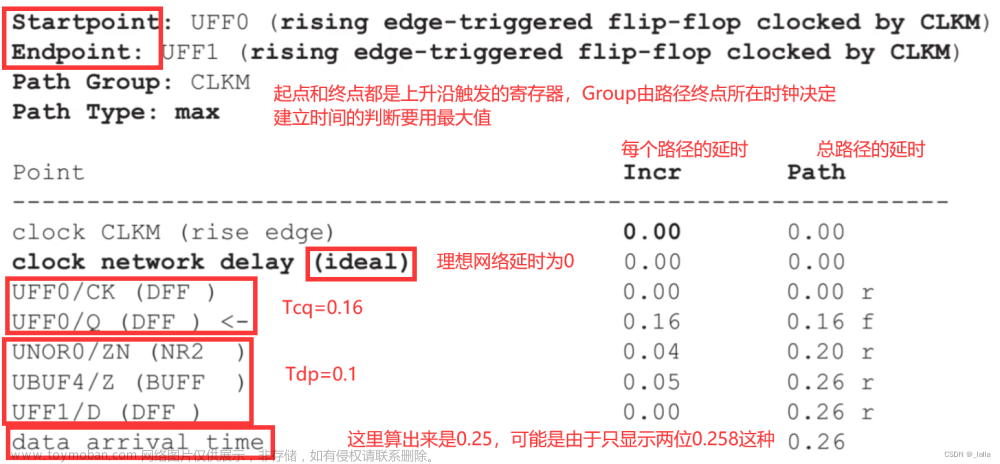

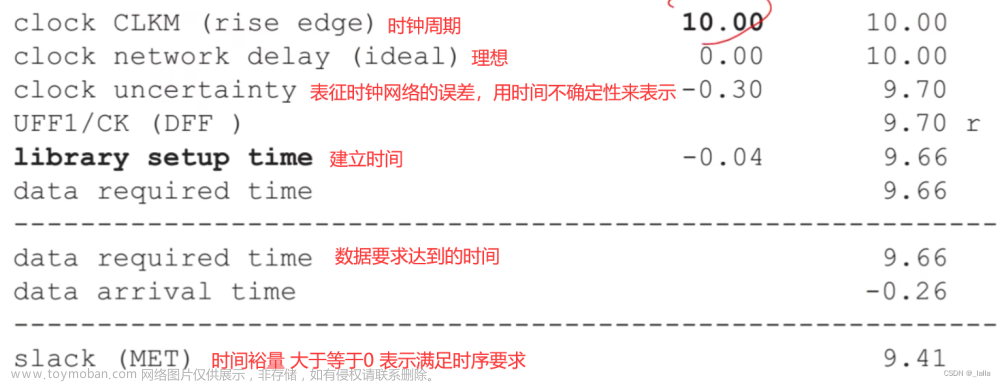

1、寄存器到寄存器

另外一个路径的时间计算如下,要减去clock uncertainty,使得时序约束更加严格

时钟不确定性,通常来说芯片在制造过程中存在很多的随机的偏差,如果我们此时在建立时间之前再将数据需要稳定的时间提前一些,以此来模拟芯片实际生成中的偏差。如果clock uncertainty 大于零,就会导致一个比较严谨的建立时间时序约束。如果在uncertainty 大于零的情况下,数据依然能够稳定到达,那也就是说这个设计比较安全。

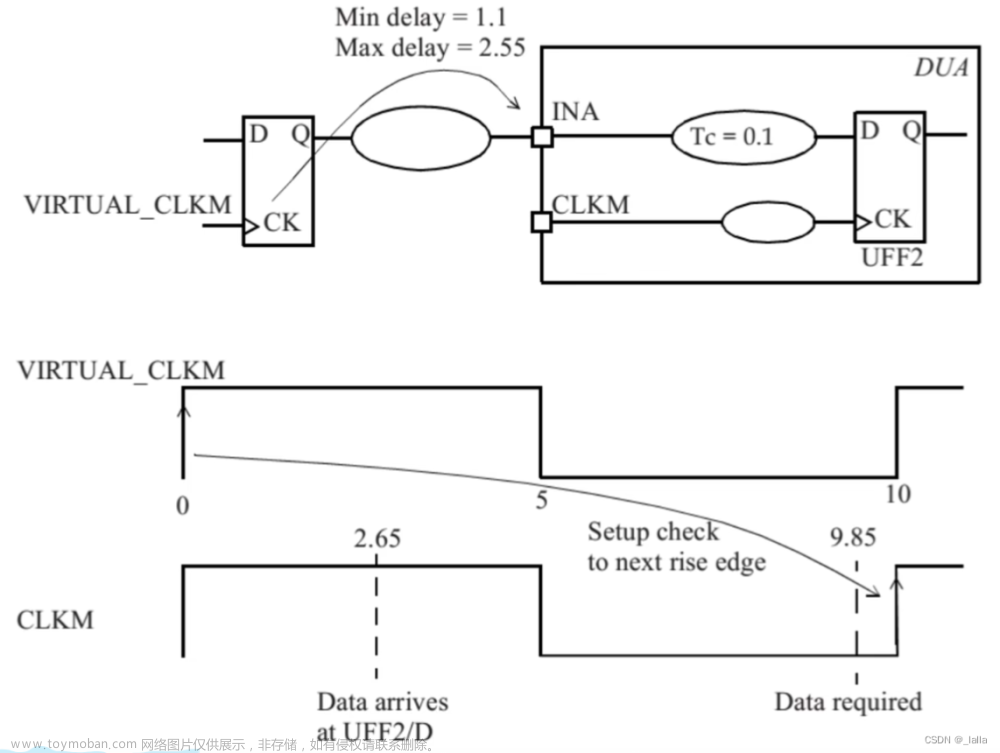

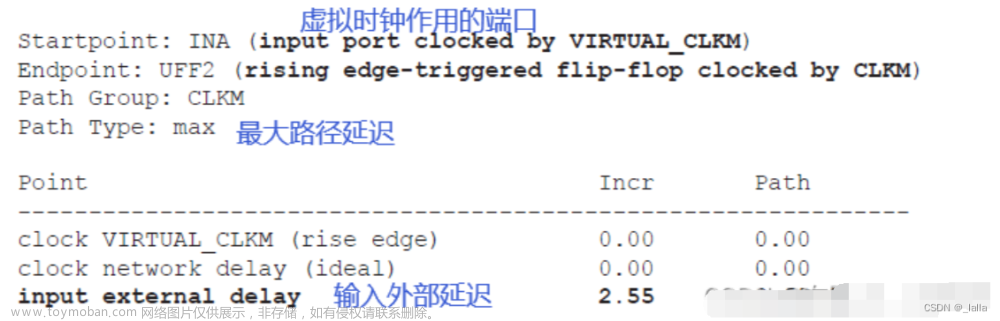

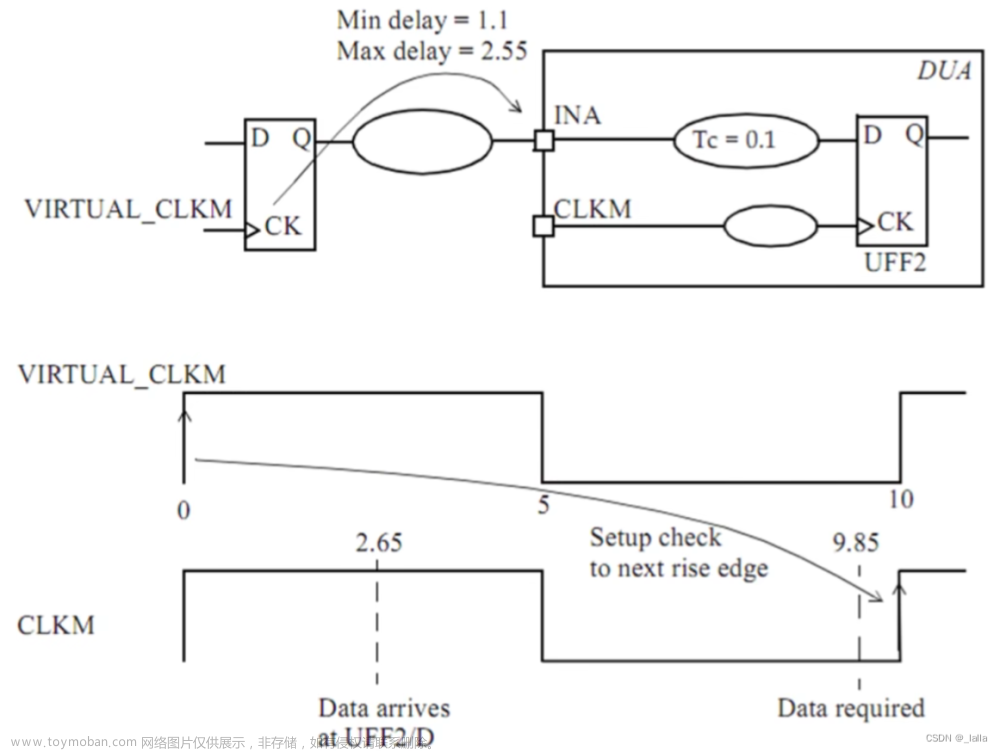

2、输入端口到寄存器

这种情况一般定义一个虚拟时钟,再来进行分析

其实是对方框内的芯片进行STA

create_clock -name VIRTUAL_CLKM -period 10 -waveform{0 5}

set_input_delay -clock VIRTUAL_CLKM -max 2.55 [get_ports INVA]

第二条路径减去clock uncertainty,再减去建立时间,使得约束严格

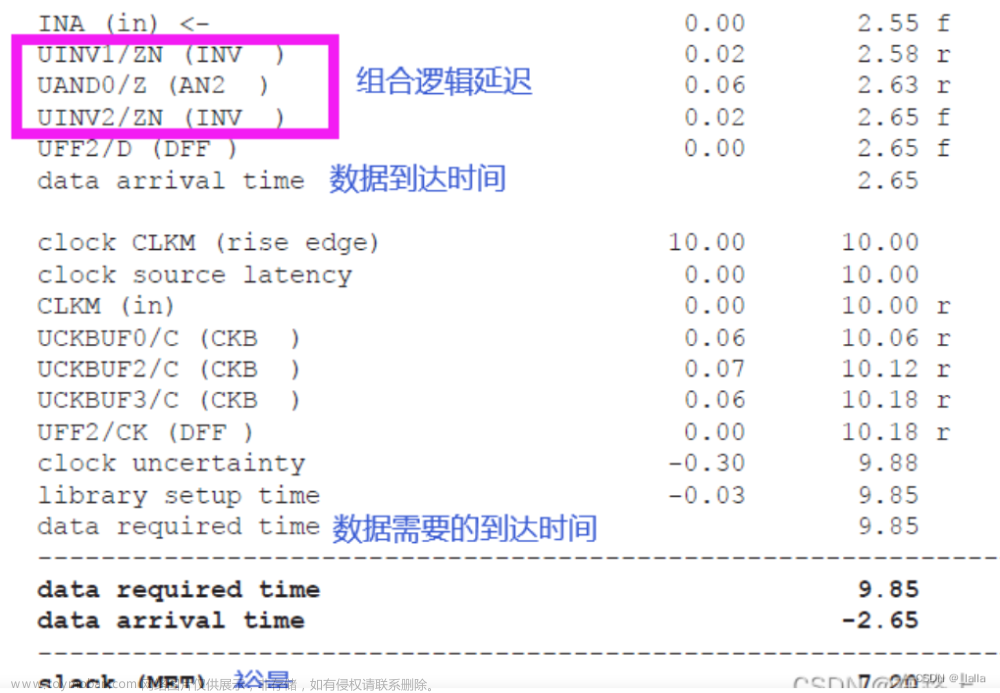

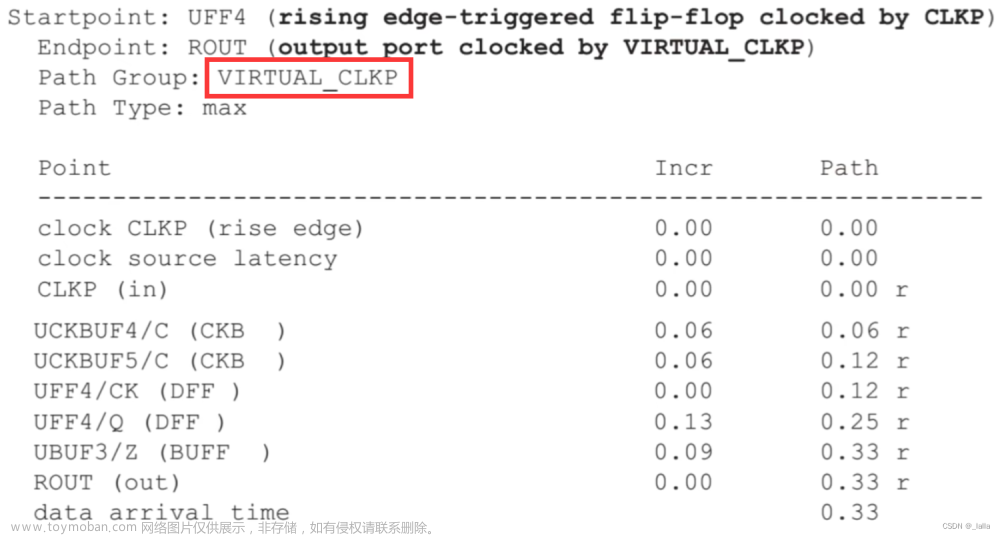

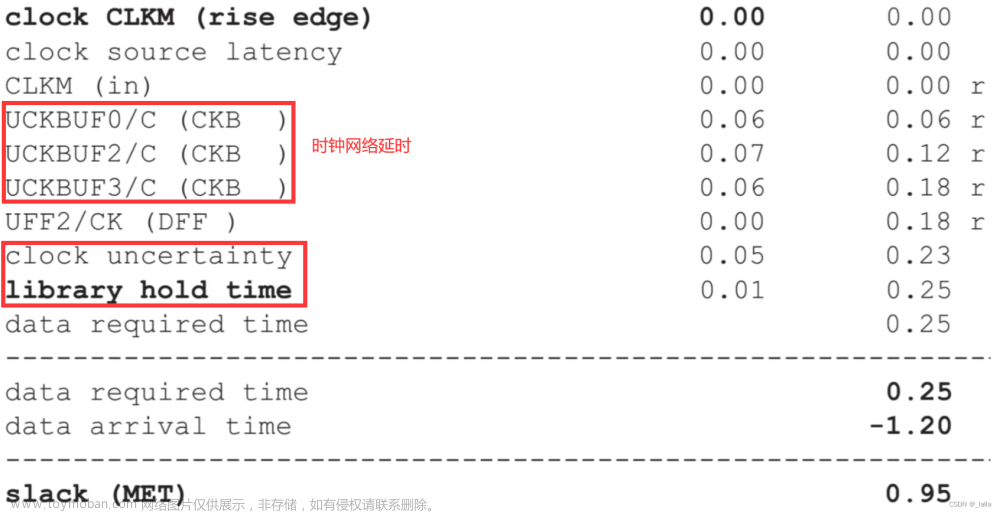

3、寄存器到输出端口

set_output_delay -clock VIRTUAL_CLKP -max 5.1 [get_ports ROUT]

set_load 0.02 [get_ports ROUT] //除了对输出延时进行约束外,还要对输出负载约束

注意这里是T减去输出延时

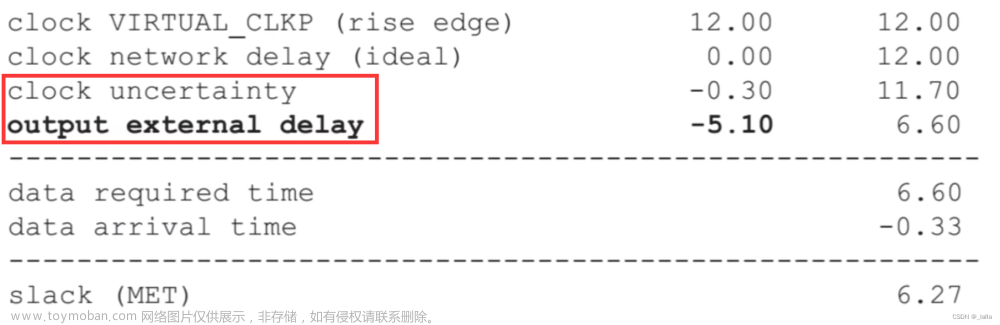

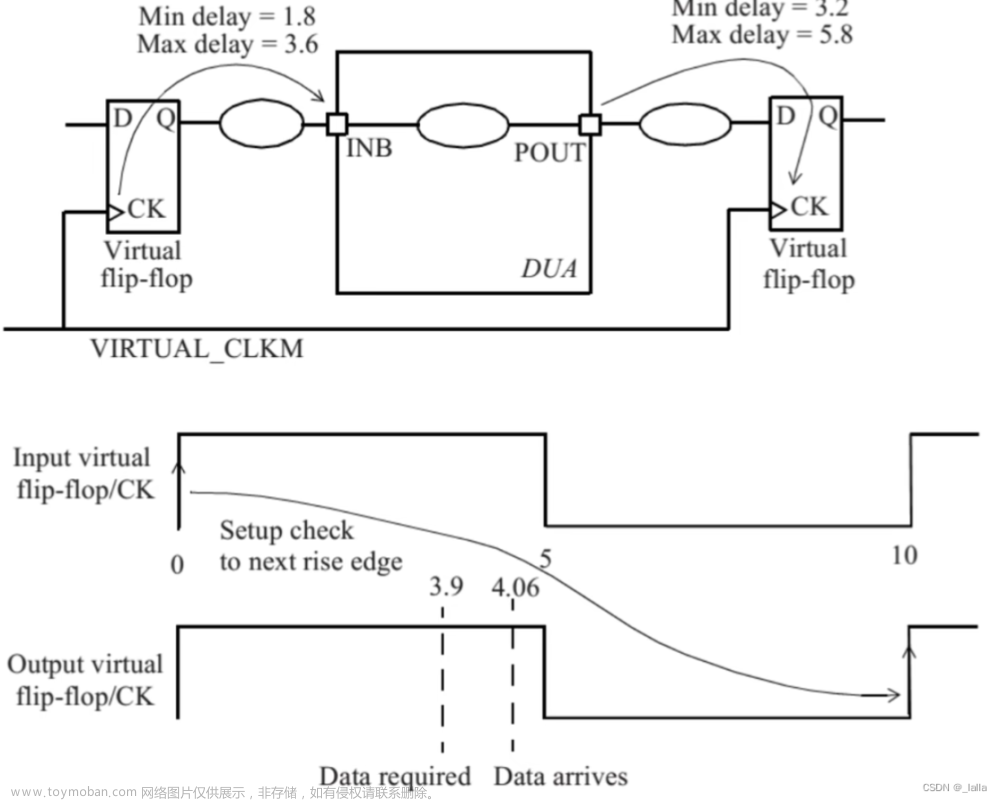

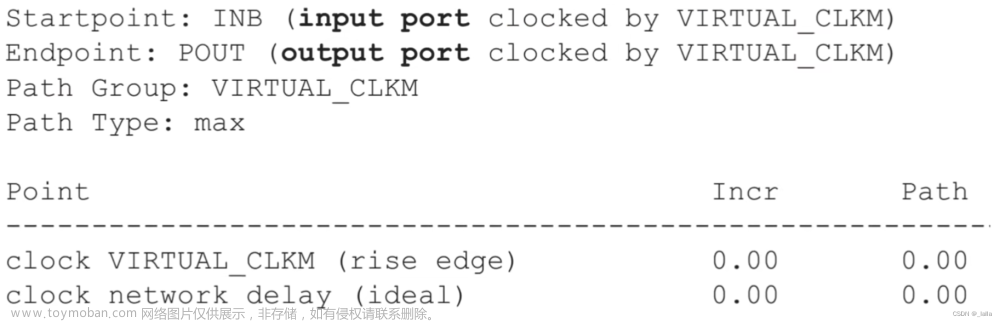

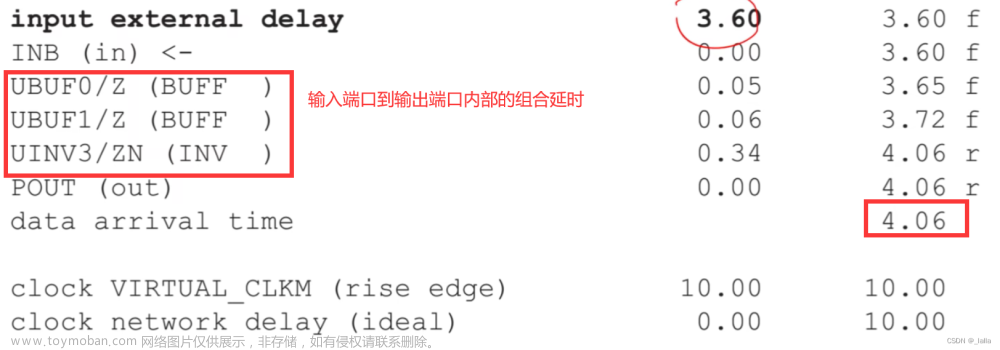

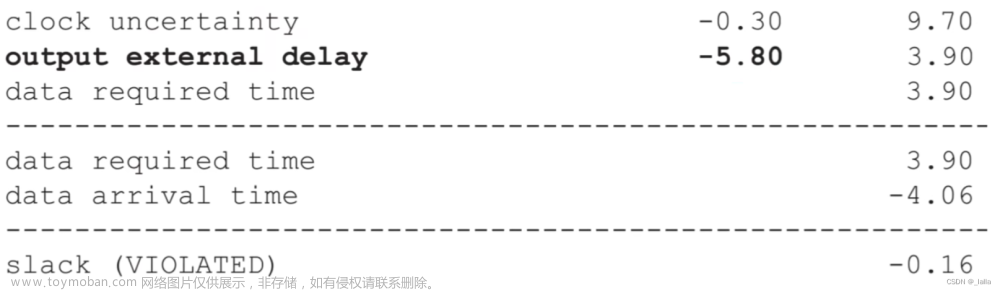

4、输入端口到输出端口

set_input_delay -clock VIRTUAL_CLKM -max 3.6 [get_ports INB]

set_output_delay -clock VIRTUAL_CLKM -max 5.8 [get_ports POUT]

该路径时序报告最后结果为负值,说明不满足要求。

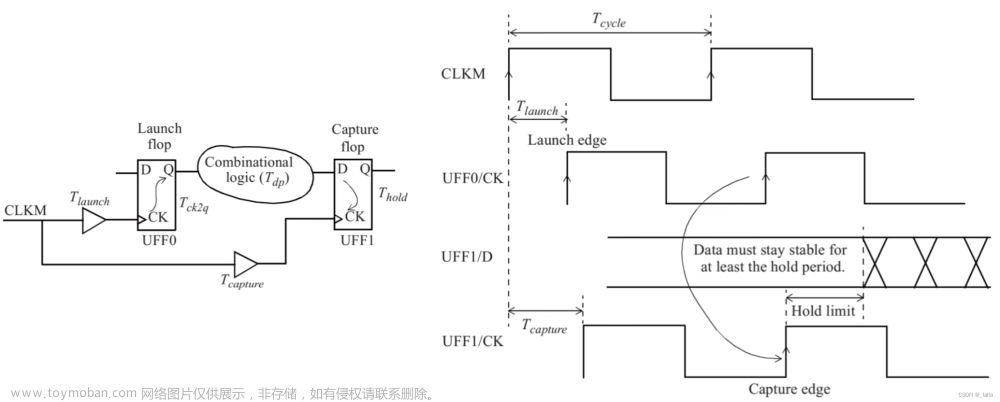

二、保持时间检查

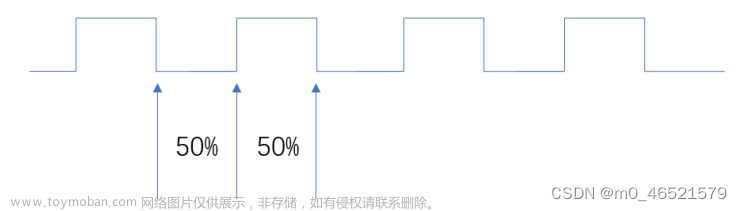

clock uncertainty:对于建立时间来说,这个值是负数;对于保持时间,这个值是正数。(引入这个参数的目的是为了使得时序更加严格,根据实际来判断正负)

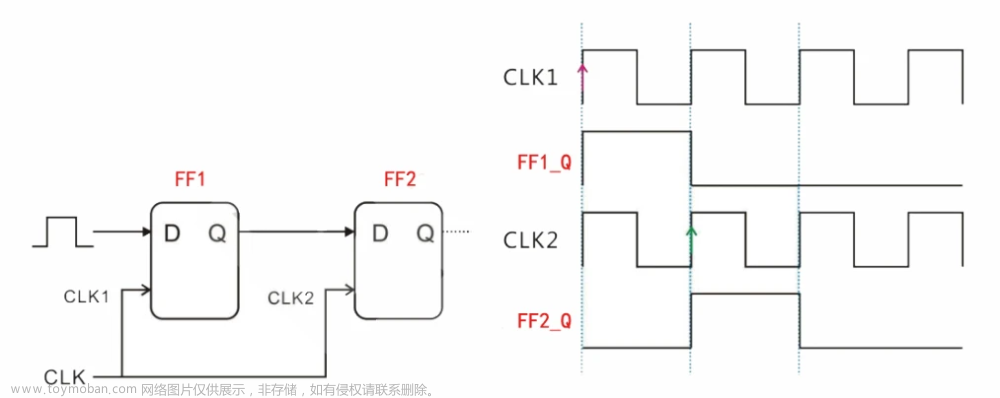

保持时间和建立时间检查的区别:

- 保持时间是在同一时钟边沿进行检查,数据的发射路径和接收路径是同一时钟边沿。建立时间数据捕获路径要比发射路径晚一个时钟周期,不在同一时钟沿检查。

- 保持时间检查与时钟周期无关。如果要计算一个电路的时钟周期,只能从建立时间去计算。

- 一般先检查保持时间,建立时间违例修复的方法有很多,而修复保持时间的方法很少。

- 对于保持时间,上面的数据发射路径的时间要大于下面的捕获时间,数据要维持到捕获之后;而对于建立时间,则是上面发射路径时间要小于捕获路径时间,要求捕获之前数据已经达到了。

- 当前时钟沿捕获的是上一个时钟沿发射的数据,与此同时,这个时钟沿会发射新的数据,为了不影响捕获上个时钟沿的数据,需要有

保持时间检查。在当前时钟沿同时完成捕获数据和发射数据的功能。 - 保持时间检查取

左边的最小值,如果左边的最小值都大于右边,说明时序肯定满足要求

Tlaunch + Tcq + Tdp >= Tcapture + Thold

保持时间违例的解决方法:

- 在数据路径上增加buffer(增大Tdp)

- 选择器件延迟更大的触发器(增加Tcq)

- 优化时钟路径,让时钟来得更早(相当于减小Tskew)

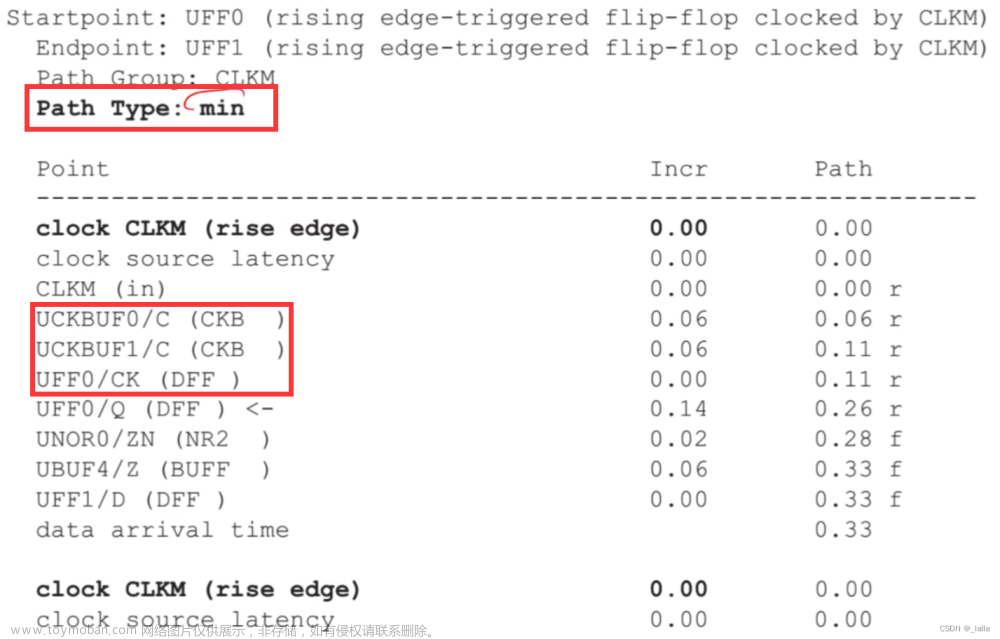

1、寄存器到寄存器

这里用的是arrival time - required time(前者数值大于后者),为了使得用户可以快速根据正负值来判断是否违例。不管是建立时间还是保持时间,都是小于0的时候就表示违例。

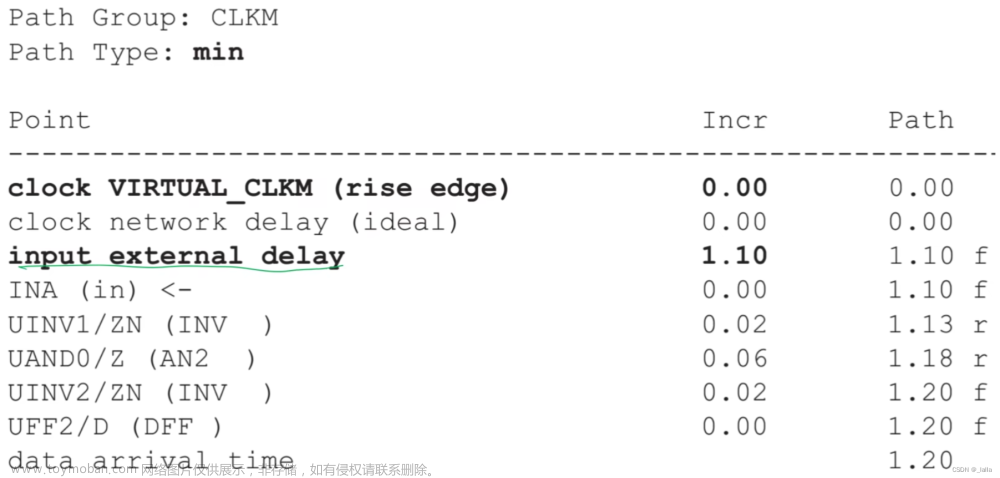

2、输入端口到寄存器

注意这里设置的输入延时的最小值

set_input_delay -clock VIRTUAL_CLKM -min 1.1 [get_ports INA]

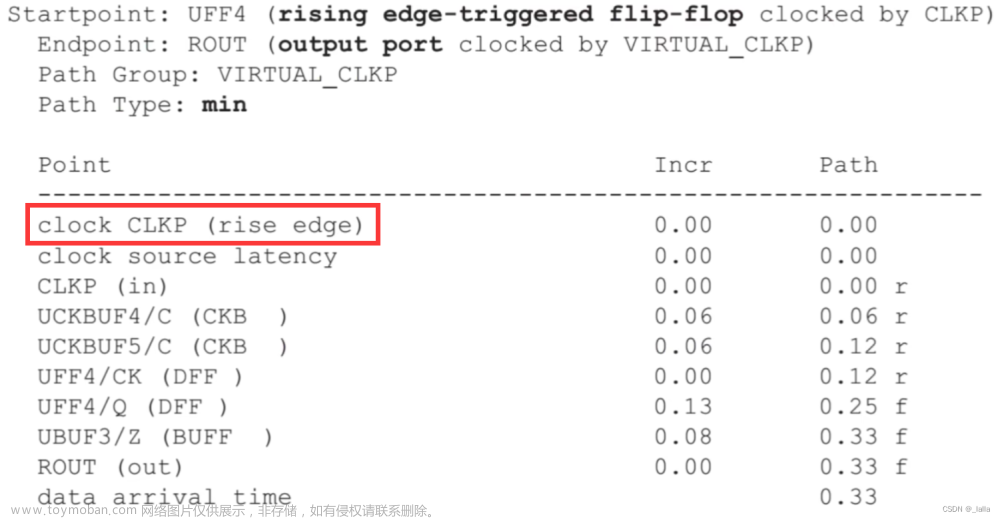

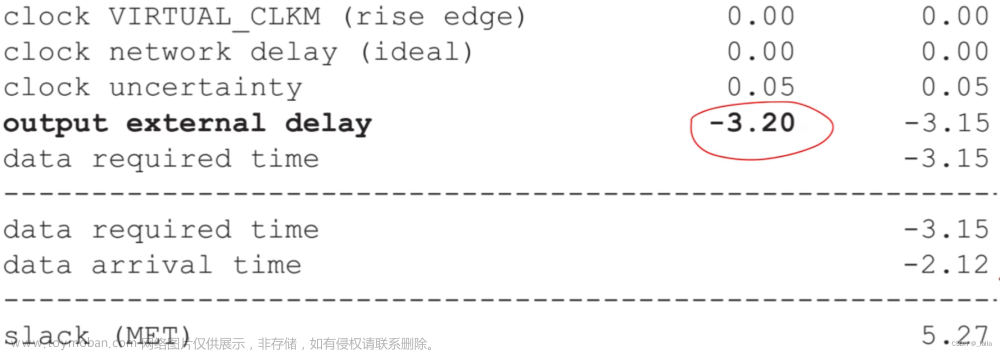

3、寄存器到输出端口

set_output_delay -clock VIRTUAL_CLKM -min 2.5 [get_ports ROUT]

文章来源:https://www.toymoban.com/news/detail-411322.html

文章来源:https://www.toymoban.com/news/detail-411322.html

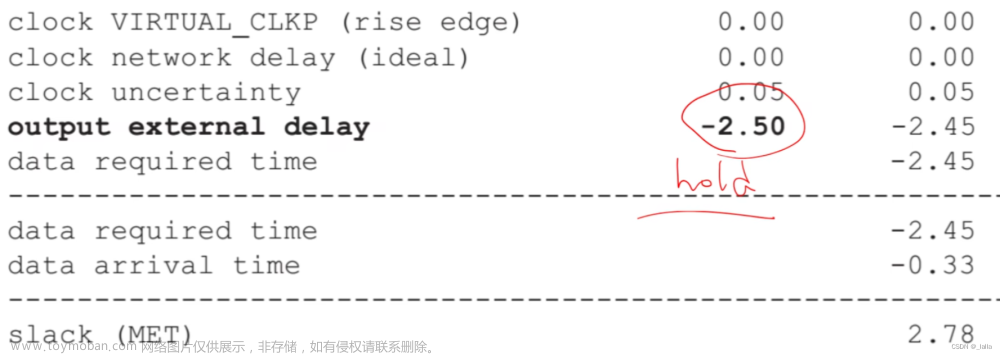

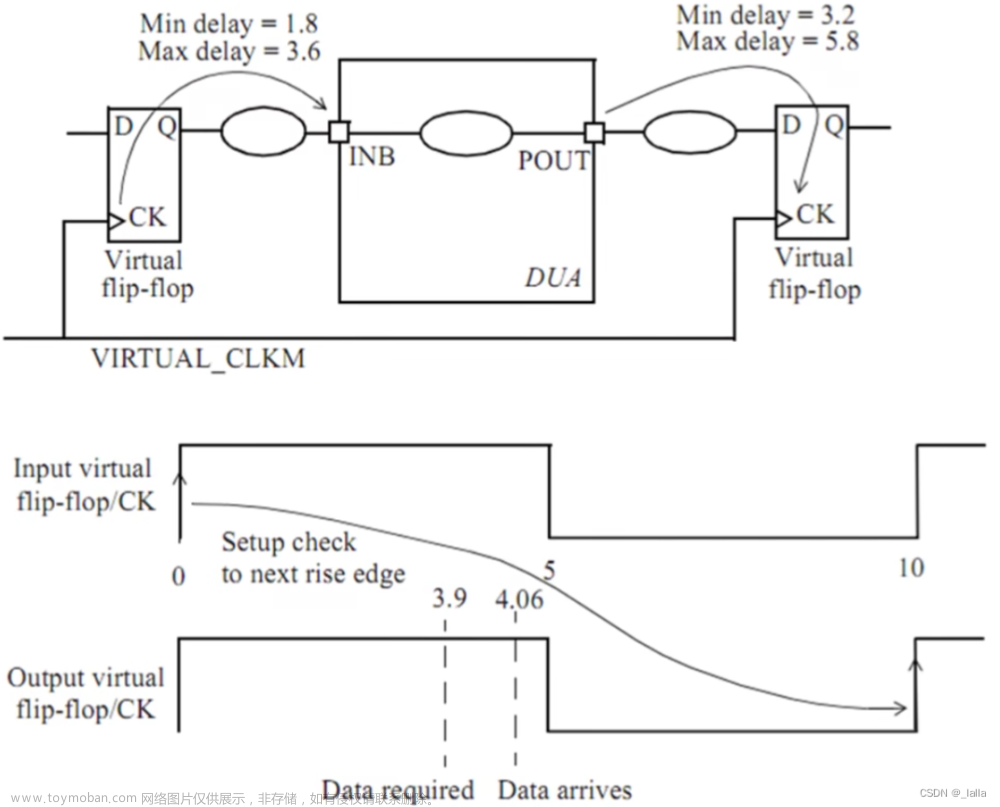

4、输入端口到输出端口

set_load -pin_load 0.15 [get_ports POUT]

set _output_delay -clock VIRTUAL_CLKM -min 3.2 [get_ports POUT]

set_input_delay -clock VIRTUAL_CZKM -min 1.8 [get_ports INB]

set_input transition 0.8 [get_ports INB]

文章来源地址https://www.toymoban.com/news/detail-411322.html

文章来源地址https://www.toymoban.com/news/detail-411322.html

到了这里,关于静态时序分析Static Timing Analysis2——建立时间和保持时间的时序检查的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[静态时序分析简明教程(八)]虚假路径](https://imgs.yssmx.com/Uploads/2024/02/434351-1.png)