目录

一、数码管静态显示

二、数码管动态显示

1、变量定义

2、定时(60us)

3、动态显示

代码

一、数码管静态显示

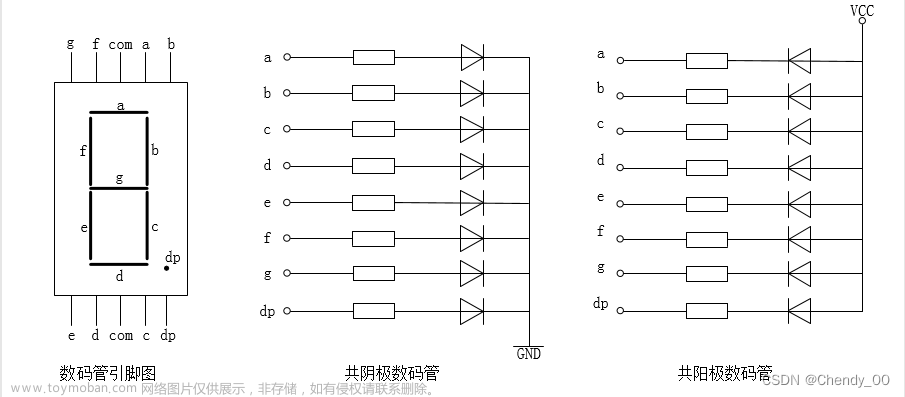

FPGA的数码管有4位,8段。(位和段都是共阳,即低电平有效)

位选的4位(二进制):分别为第1、2、3、4位数码管。

段选的8位(二进制):分别为第h、g、f、e、d、c、b、a段。

下面用4位(所有)数码管, 显示数字“1”:

//数码管(共阳:低电平有效)

//FPGA的数码管:段选和位选都共阳

module my_and(dig, seg);

output wire [3:0] dig; //位选(选定某一个数码管)

output wire [7:0] seg; //段选(选定一个数码管上的小段)

assign dig = 4'b0000; //位选(0000:4个零,共4个数码管,全选)

assign seg = 8'b1111_1001; //段选(第6、7段为0,显示的是“1”)

endmodule

二、数码管动态显示

由于要显示不同的数字,但是FPGA的数码管没办法单独操作,只能群操作。

所以只能给每个数码管不同的频率,然后依次显示。

注:这里频率要给适当:

频率过快:容易发生混叠;

频率过慢,变化慢,明显的流水式显示。

频率过慢(流水式变化):

频率过快(混叠):

正常频率:

1、变量定义

module my_and(dig, seg, clk, rst_n);

input clk, rst_n;

output reg [7:0] seg; //段选(选定一个数码管上的小段)

output reg [3:0] dig; //位选(选定某一个数码管)

reg [25:0] cnt;

reg [1:0] wei;2、定时(60us)

计时到60us,使得位变化一次。 文章来源:https://www.toymoban.com/news/detail-411791.html

//定时(60us变化位变化一次)

always@ (posedge clk, negedge rst_n)

begin

//按下复位键(清空)

if(!rst_n)

cnt <= 1'b0; //清空

else if(cnt != 12'd3000) //60us(3000*20ns=60us)

cnt <= cnt + 1'b1;//加1

else

begin

cnt <= 1'b0; //清空

wei <= wei + 1; //位+1

end

end3、动态显示

这里改变位(dig)和段(seg),段随位变。 文章来源地址https://www.toymoban.com/news/detail-411791.html

//动态显示

always@(*)

begin

case(wei)

//2

2'b00:

begin

dig <= 4'b0111;

seg <= 8'b1010_0100;

end

//5

2'b01:

begin

dig <= 4'b1011;

seg <= 8'b1001_0010;

end

//0

2'b10:

begin

dig <= 4'b1101;

seg <= 8'b1100_0000;

end

//8

2'b11:

begin

dig <= 4'b1110;

seg <= 8'b1000_0000;

end

endcase

end代码

//数码管动态显示(共阳:低电平有效)

//由于要显示不同的数字,但是FPGA的数码管没办法单独操作,只能群操作。

//所以只能给每个数码管不同的频率,然后依次显示

//注:这里频率要给适当,

//频率过快:容易发生混叠;

//频率过慢,变化慢,明显的流水式显示

/*对照表

4'h0 : seg = 8'hc0; //显示"0"

4'h1 : seg = 8'hf9; //显示"1"

4'h2 : seg = 8'ha4; //显示"2"

4'h3 : seg = 8'hb0; //显示"3"

4'h4 : seg = 8'h99; //显示"4"

4'h5 : seg = 8'h92; //显示"5"

4'h6 : seg = 8'h82; //显示"6"

4'h7 : seg = 8'hf8; //显示"7"

4'h8 : seg = 8'h80; //显示"8"

4'h9 : seg = 8'h90; //显示"9"

4'ha : seg = 8'h88; //显示"a"

4'hb : seg = 8'h83; //显示"b"

4'hc : seg = 8'hc6; //显示"c"

4'hd : seg = 8'ha1; //显示"d"

4'he : seg = 8'h86; //显示"e"

4'hf : seg = 8'h8e; //显示"f"

*/

module my_and(dig, seg, clk, rst_n);

input clk, rst_n;

output reg [7:0] seg; //段选(选定一个数码管上的小段)

output reg [3:0] dig; //位选(选定某一个数码管)

reg [25:0] cnt;

reg [1:0] wei;

//定时(60us变化位变化一次)

always@ (posedge clk, negedge rst_n)

begin

//按下复位键(清空)

if(!rst_n)

cnt <= 1'b0; //清空

else if(cnt != 12'd3000) //60us(3000*20ns=60us)

cnt <= cnt + 1'b1;//加1

else

begin

cnt <= 1'b0; //清空

wei <= wei + 1; //位+1

end

end

//动态显示

always@(*)

begin

case(wei)

//2

2'b00:

begin

dig <= 4'b0111;

seg <= 8'b1010_0100;

end

//5

2'b01:

begin

dig <= 4'b1011;

seg <= 8'b1001_0010;

end

//0

2'b10:

begin

dig <= 4'b1101;

seg <= 8'b1100_0000;

end

//8

2'b11:

begin

dig <= 4'b1110;

seg <= 8'b1000_0000;

end

endcase

end

endmodule

到了这里,关于FPGA(5)数码管静态显示与动态显示的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[FPGA 学习记录] 数码管动态显示](https://imgs.yssmx.com/Uploads/2024/02/766282-1.png)