一、目的:

1、掌握Cadence Virtuoso快捷键技巧,学会使用Cadence进行原理图设计、版图设计、原理图仿真。

2、实验使用AMI 0.6u C5N工艺,了解NCSU Cadence设计套件(NCSU_Analog_Parts库)的使用,学会使用自行设计的反相器设计环形振荡器。

3、实现CMOS 环形振荡器的设计与仿真。

二、设计分析:

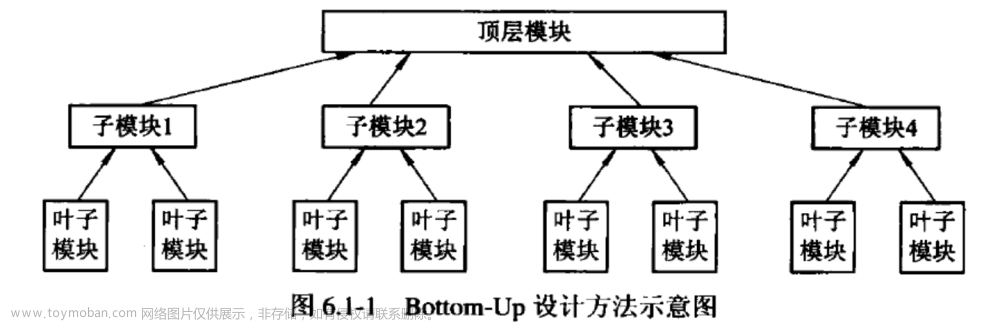

1、设计原理:环形振荡器的结构必须是一串奇数个串联连接的反相器(Invertor)构成一个闭环回路,最后一个输出恰好接上最初的输入。

例如:初始触发的时候给“1”,最后输出就是“0”,也就意味着第二个周期输入自然也就是“0”。在第二个周期里输出又变成“1”。如此,就实现了“0”和“1”的固定频率交替振荡输出。

2、频率计算:根据之前对反相器的设计,我们先根据实验指导书设计一个由31个串联连接的反相器构成的环形振荡器,通过总体设计后仿真结果得出,此环形振荡器输出振荡周期为5.0×10(-9)S,如图:

即可根据振荡器的周期公式T=2×N×tP (N是反相器的个数,tp是单个反向器的反应时间)推出:tP=0.08×10(-9)S=8×10(-11)S,同理可计算出当反相器个数为31时的环形振荡器振荡频率为2×108Hz。

3、自主设计:为了以后在芯片设计时,使芯片片内时钟便于分频和使用,我将设计一个振荡频率为1×108Hz,即100MHz的环形振荡器,此振荡器周期T=1×10(-8)S。又已知tP=0.08×10(-9)S=8×10(-11)S,T=2×N×tP ,则可计算出N=62.5。又因为环形振荡器串联连接的反相器必须是奇数,并且通过实际仿真考虑一定延时后,我最终选择了N=61来进行设计。

三、步骤:

首先验证所设计的单一反相器的反应时间。在库管理器中添加一个库,为方便今后辨认,我添加的库名为Aurora-5,如图:

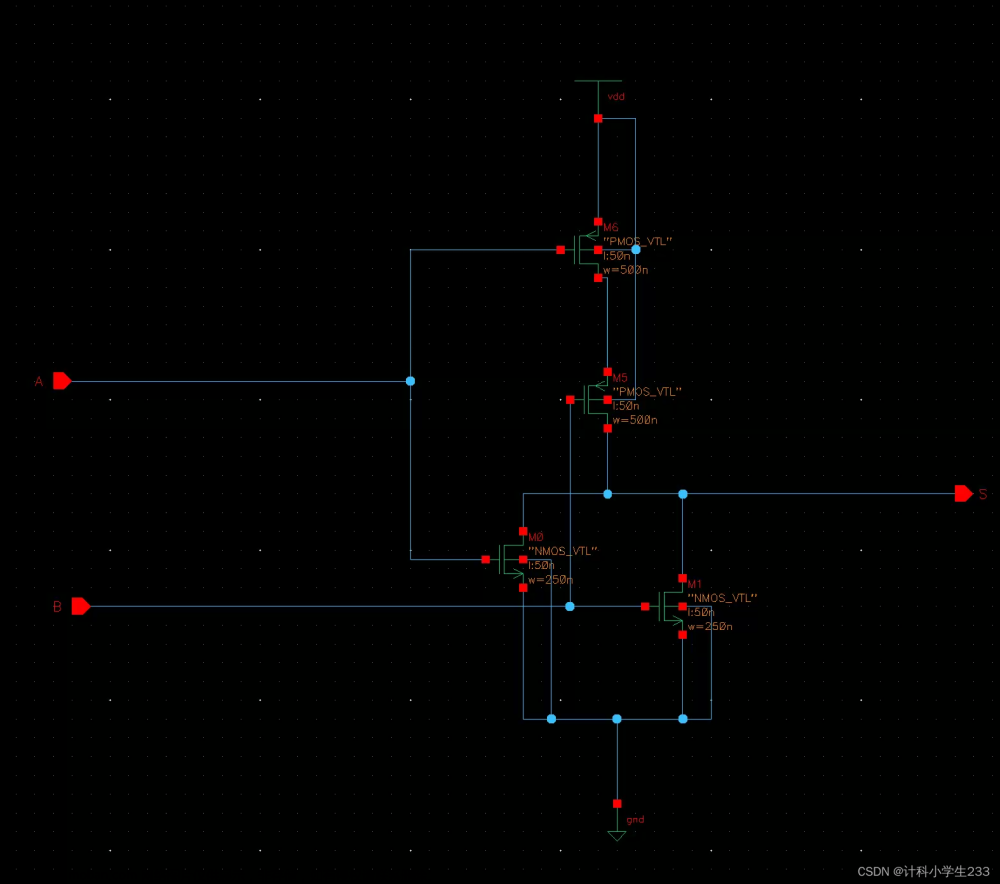

选择库管理器中的Aurora-5库,新建原理图,使用NCSU_Analog_Parts库中源网络和之前成功设计的反相器绘制如下CMOS 环形振荡器原理图如图,共31个反相器输入输出首尾相接组成:

检查并保存”以后,对原理图进行ADE仿真,启动ADE_L,转至选择菜单Setup - > Model Libraries,选择地址在/$ HOME=/home/cademce/ncsu-cdk-1.6.0.beta/models/Spectre /standlone的ami06N.m(NMOS模型文件)以及ami06P.m(PMOS模型文件),并且选择Setup—>Stimuli设置好Vdd!参数为DC 5V并且Enabled,之后Apply,之后再设置tran参数,所有参数设置完成后,仿真结果如下图:

仿真结果可见环形振荡器已经可以正常起振。为了使原理图美观,便于查看和修改N值,则将其改为如下图所示原理图:

改动完成再次仿真,参数设置及仿真模型选择等步骤同之前一致,选择右端导线作为输出信号后,仿真结果如图所示:

仿真结果与改动原理图之前一致,之后在原理图界面选择Create—Cellview—From Cellview建立CMOS 环形振荡器原理图的Symbol,绘制如下图:

“检查并保存”以后,重新建立一个原理图对Symbol进行ADE仿真。CMOS环形振荡器的Symbol仿真参数设置如下图:

选择需要输出仿真结果的导线,之后运行仿真,CMOS环形振荡器Symbol仿真结果如下图所示:

仿真结果符合预期,保存仿真文件于Cellview中便于下次调用无需重新设置参数,上述无问题后,进行版图绘制,在Aurora-5库中新建一个Layout版图文件,绘制CMOS 环形振荡器的版图,绘图布局时始终使用“drw”图层,绘制完成如下图所示:

输出端引脚绘制如下图所示:

DRC版图Layout后,导出CMOS 环形振荡器的抽取视图(Extracted),成功后如下图所示:

输出端局部视图如下图所示:

检查并使CMOS 环形振荡器版图的抽取视图(Extracted)与CMOS 环形振荡器的原理图相匹配,运行LVS,LVS完成后,结果如下:

CMOS 环形振荡器版图抽取视图LVS的Output显示“The net-lists match.”,Output结果如下图:

之后,对CMOS 环形振荡器进行后仿真:把CMOS 环形振荡器ADE_L设置环境Switch View List中仿真对象为“extracted schematic”,运行仿真,CMOS 环形振荡器仿真结果如下:

可见对“extracted schematic”的仿真结果中,由31个反相器构成的环形振荡器输出振荡周期为5.0×10(-9)S,如图:

根据振荡器的周期公式T=2×N×tP (N是反相器的个数,tp是单个反向器的反应时间)推出:tP=0.08×10(-9)S=8×10(-11)S,同理可计算出当反相器个数为31时的环形振荡器振荡频率为2×108Hz。

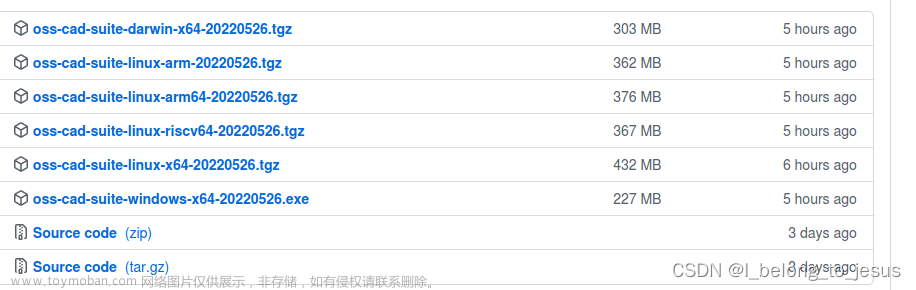

为了以后在芯片设计时,使芯片片内时钟便于分频和使用,我将设计一个振荡频率为1×108Hz,即100MHz的环形振荡器,此振荡器周期T=1×10(-8)S。又已知tP=0.08×10(-9)S=8×10(-11)S,T=2×N×tP ,则可计算出N=62.5。又因为环形振荡器串联连接的反相器必须是奇数,并且通过实际仿真考虑一定延时后,我最终选择了N=61来进行设计。在库管理器中复制粘贴一个库,为方便今后辨认,我添加的库名为Aurora-5-Freq,如图:

更改RING-OSC原理图使N=61,如下图所示:

改动完成再次仿真,参数设置及仿真模型选择等步骤同之前一致,选择相应导线作为输出信号后,仿真结果如图所示:

仿真结果符合预期,之后更新Symbol并绘制Layout,版图内共61个反相器首尾相连,绘制结果如下图所示:

输出端与首尾相连部分局部视图分别如下两图所示:

DRC版图Layout后,导出CMOS 环形振荡器的抽取视图(Extracted),成功后如下图所示:

检查并使CMOS 环形振荡器版图的抽取视图(Extracted)与CMOS 环形振荡器的原理图相匹配,运行LVS,LVS完成后,CMOS 环形振荡器版图抽取视图LVS的Output显示“The net-lists match.”,结果如下图:

之后,对N=61的CMOS 环形振荡器进行后仿真:把CMOS 环形振荡器ADE_L设置环境Switch View List中仿真对象为“extracted schematic”,运行仿真,CMOS 环形振荡器仿真结果如下:

可见仿真结果显示振荡周期T=1×10(-8)S,振荡频率为1×108Hz,此振荡器仿真结果符合预期。至此,后仿真结果与预想理论情况一致,版图设计无问题,原理图与版图及其抽取视图相匹配,振荡频率为100MHz的 CMOS 环形振荡器设计结束。

四、设计结果:

原理图(Schematic):

上图为100MHz CMOS 环形振荡器原理图。

上图为100MHz CMOS 环形振荡器的Symbol绘制结果。

原理图设计仿真(ADE_L):

上图为100MHz CMOS 环形振荡器 Symbol仿真用原理图。

上图为100MHz CMOS 环形振荡器 Symbol原理图仿真结果。

版图(Layout)设计:

上图为100MHz CMOS 环形振荡器版图绘制结果。

抽取视图(Extracted):

上图为100MHz CMOS 环形振荡器版图抽取视图结果。

LVS结果:

上图为100MHz CMOS 环形振荡器版图及原理图匹配成功后LVS的Output结果。(显示“The net-lists match.”)

后仿真结果(Sim-Extracted Schematic):

文章来源:https://www.toymoban.com/news/detail-412884.html

文章来源:https://www.toymoban.com/news/detail-412884.html

上图为实验最后设置100MHz CMOS 环形振荡器 Symbol原理图仿真环境Switch View List中仿真对象为“extracted schematic”后的仿真结果,显示振荡周期T=1×10(-8)S,振荡频率为1×108Hz,此环形振荡器仿真结果符合预期。文章来源地址https://www.toymoban.com/news/detail-412884.html

到了这里,关于集成电路CAD设计:CMOS 环形振荡器设计与仿真的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!