异步复位,同步释放是一种常见的设计思路,那么什么情况下,复位信号需要做“异步复位,同步释放”处理?

一般来说,同步系统,都使用异步复位。这是因为同步复位的电路实现,比异步复位的电路实现,要浪费更多电路资源。

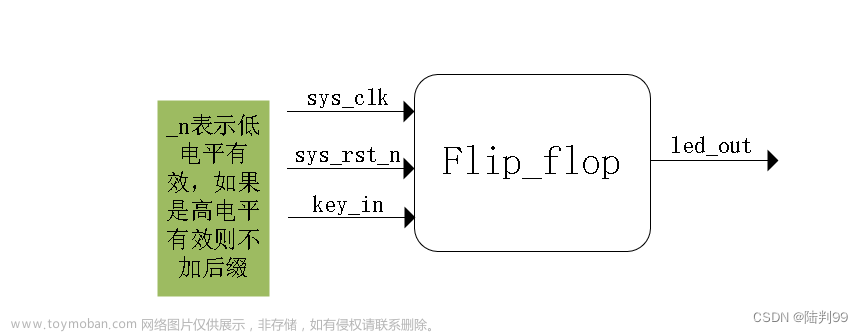

未在本模块时钟域做过“异步复位,同步释放”处理的复位信号,提供给本模块做异步复位使用时,都需要做“异步复位,同步释放”处理。

常见于系统内两部件不在同一时钟域的情况下。

假设rst_async_n撤除时发生在clk上升沿,如果不加此电路则可能发生亚稳态事件(有的时候会打三拍)。

但是加上此电路以后,假设第一级D触发器clk上升沿时rst_async_n正好撤除,则D触发器1可能输出高电平“1”,也可能输出亚稳态,也可能输出低电平。

但此时第二级触发器不会立刻更新输出,第二级触发器输出值为前一级触发器Q1的输出状态。显然Q1之前为低电平,故第二级触发器输出保持复位低电平。

直到下一个时钟有效沿到来之后,才随着变为高电平。即实现同步释放。

以下几个问题大家可以思考一下,我给出了参考答案:

问题1. 如果没有前面两级触发器的处理。异步信号直接驱动系统的触发器。会出现什么情况?

异步复位信号或者异步置位信号,存在建立保持时间的违反,从而时序冲突,引发输出亚稳态。

问题2. 复位信号存在亚稳态,有危险吗?

一个信号出现亚稳态,是在信号变化的时候,不能保证第一拍采样的值是固定的。可能是0,也可能是1,是一个不确定的X态。

而系统不希望这样的未知状态发生,系统希望知道在某一个时刻,后续逻辑需要的输入信号,是稳定值。

二级触发器同步后,第二级触发器的输出基本上是稳定值。后续逻辑根据稳定值,会有稳定的行为。

这就是追求的系统稳定性。最好是系统一起复位释放,但是时钟域不同,不可能保证系统一起复位释放。

一般来说,系统复位释放的顺序,是需要保证的。否则系统就是不安全的。

问题3. 如果只做一级触发器同步,如何?

不可以。

第一级触发器的输出,永远存在亚稳态的可能。亚稳态,导致系统不会复位初始化到已知状态。 当第一级触发器采样异步输入之后,允许输出出现的亚稳态可以长达一个周期,在这个周期内,亚稳态特性减弱。

在第二个时钟沿到来时,第二级同步器采样,之后才把该信号传递到内部逻辑中去。第二级输出是稳定且已被同步了的。

如果在第二级采样时保持时间不够,第一级的输出仍然处于很强的亚稳态,将会导致第二级同步器也进入亚稳态,但这种故障出现的概率比较小。

一般情况下,两级同步器总体的故障概率是一级同步器故障概率的平方。在大部分的同步化设计中,用两级同步器消除可能的亚稳态,有时候用三级。

问题4. 两级触发器同步,就能消除亚稳态吗?

不能。只是概率降低了。文章来源:https://www.toymoban.com/news/detail-413919.html

更多关于verilog的相关资料可以去IC修真院资料下载中心

以上就是给大家分享的“verilog|关于异步复位,同步释放的几个思考”!文章来源地址https://www.toymoban.com/news/detail-413919.html

到了这里,关于verilog|关于异步复位,同步释放的几个思考的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!