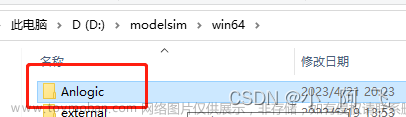

我的Modelsim-Altera是在安装Quartus13.0时下载的,里面会有选项,安装初学者版本就可以,在Quartus18.0里也可以使用。

一、设置Quartus和Modelsim的关联路径

这样就完成了关联设置,再次进行仿真就不会出现上篇文章出现的报错了。

sel为1的时候,out与a一致;sel为0的时候,out与b一致。

sel为1的时候,out与a一致;sel为0的时候,out与b一致。

这只是简单的波形仿真,下面来学习更加强大的Modelsim仿真。

二、用Verilog编写测试脚本testbench

1.File——New

2.保存在testbench文件夹,命名时在被测模块名后面加tb

3.编写代码

4.编译通过

三、调用testbench、RTL功能仿真

1.打开设置

2.设置仿真脚本

3.点击New,调用testbench文件

名称保持一致

4.开始仿真

RTL是理想化功能仿真(不考虑逻辑延迟),GateLevel是门级仿真,可以仿真布局布线和延迟

先进行RTL功能仿真

Modelsim窗口

Modelsim窗口

点击这里,使波形窗口独立出来,便于分析

想要放大或者缩小波形的话,点击这里

可见,s3=0时,Light1波形与s2一致; s3=1时,Light1波形与s1一致。

s1——a;s2——b;s3——sel;Light1——out。

这与本文第一章的波形仿真结果相同。实现了二选一多路选择器的功能。

四、Modelsim常用操作

1.添加模块内部信号

选择 Add Wave ,然后回到Modelsim

由于之前仿真时没有加载这部分波形,所以只能重新运行仿真

点击Restart——OK,再点击RUN-All

可以看到两组波形是完全相同的。

2.关闭路径

3.波形分组

Ctrl+鼠标左键 选中要分组的端口,右键,选择Group

文章来源:https://www.toymoban.com/news/detail-414299.html

文章来源:https://www.toymoban.com/news/detail-414299.html

结语

门级仿真部分在下一篇文章介绍,欢迎大家和我一起学习~文章来源地址https://www.toymoban.com/news/detail-414299.html

到了这里,关于FPGA学习笔记(二)——Modelsim仿真、testbench编写的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!