通过几个问题来记录CMOS反相器是什么,以及数字电路中为什么要使用CMOS反向器。

目录

问题

Q1:模拟电路和数字电路的区别?

Q2:为什么说相对模拟电路来说数字电路比较稳定?

Q3:数字电路中为什么要使用CMOS门电路?

Q4:CMOS的 输入噪声容限是什么?

Q5:CMOS结构中P管的宽长比W/L为什么比N管的大?

问题

Q1:模拟电路和数字电路的区别?

模拟电路:

在模拟电路中使用连续的电压,电流来表示信息。一条信号线理论上可以表示无穷多个信息。但是无法区分噪声和有效信息,不能避免噪声对电路的影响。

所以模拟电路通常用在系统前段,把外部的物理量通过传感器转换为电信号,希望尽快的就把信号传到数字电路中处理(通过ADC把模拟信号转换为数字信号)。

数字电路:

在数字系统中,传递的就是0,1,离散的电压序列。不是所有信息都是有效的。

在模拟电路中一根线可以表示无限多的信息量。但是在数学系统中,一根线只能传递0或1状态。

想要传递0.35这样的信息,需要多bit信号线才能表示出来。或者牺牲时间代价,通过一根线多次传输表示出0.35这个信息。

在数字系统中,时序和面积是需要衡量的两个重要性能。

Q2:为什么说相对模拟电路来说数字电路比较稳定?

1,因为数字电路中只进行0,1的计算,运算规则简单。

2,因为数字系统通常使用CMOS反相器作为最小设计单元。CMOS反相器对输入有一定的噪声容限,能够接受低质量的0,1输出高质量的0,1。

Q3:数字电路中为什么要使用CMOS门电路?

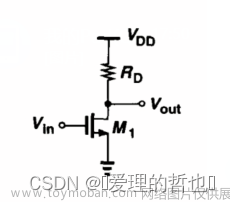

首先我们知道在数字电路中是通过电压来表示0,1两种信息。而理想的0就是地,1是电源。

按照这个思路,我们尝试用开关和电阻通过以下电路来获得0,1。

Vo = 1 ,通过Vi控制开关S断开,Vo通过R上拉到电源电压。

Vo = 0,通过Vi控制S闭合,通过开关把Vo拉到地Vss。这是我们希望R尽可能大,最好是断路。

这样确实可以让Vo输出0,1了,但是上述电路有个问题。

Vo=1时,我们希望限流电阻R尽可能小,减小分压和功耗,让Vo尽量等于Vcc。

V1=0时,我们有希望限流电阻尽可能大,最好时断路,让Vo尽量等于Vss。

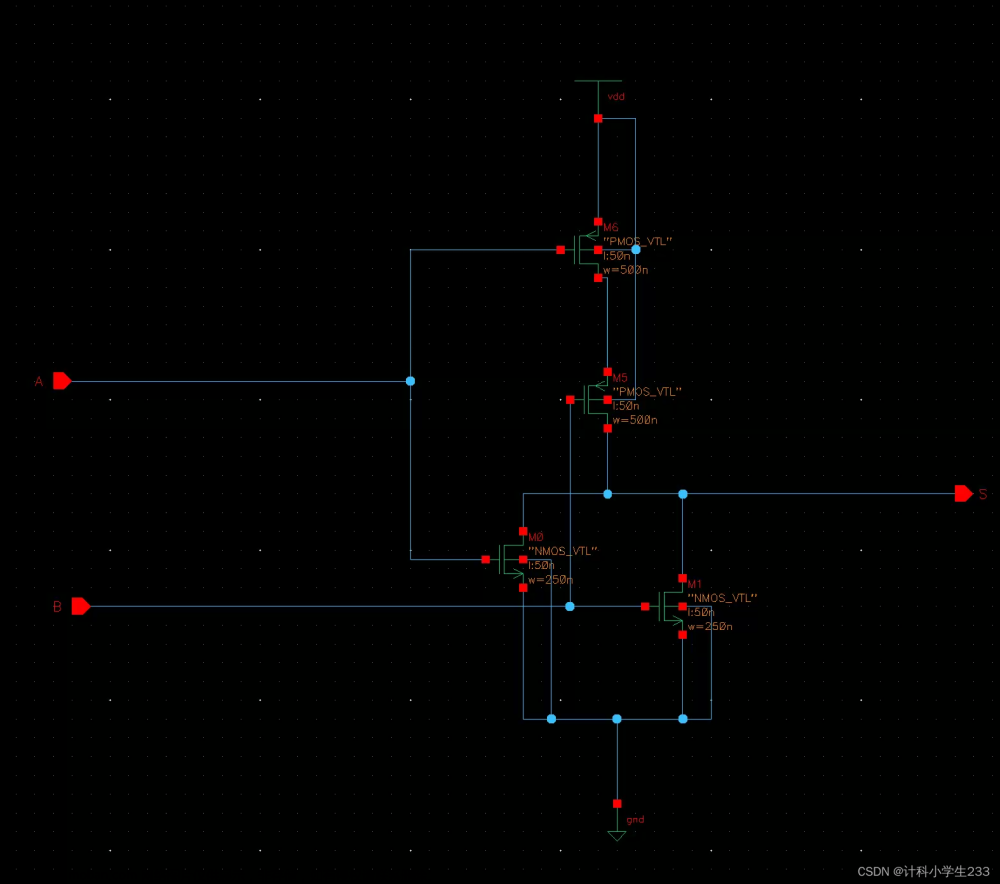

上述电路满足不了这个要求,那么我们想到MOS管也有开关特性,可以把开关S和电阻R换成两个MOS管。

当Vi < Vgs(th) ,NMOS截止,Vo ≈Vdd

当Vi > Vgs(th) ,NMOS导通,工作在可变电阻区,等效为一个小电阻Ron,Vo ≈0

所以MOS管的DS之间相当于一个受Vi控制的开关。

然后我们再把电阻R也换成一个Pmos。

当Vi = 1,NMOS导通,处于可变电阻区,而PMOS截止,处于截止区,流过PMOS的电流接近于0,基本没有功耗。

NMOS,PMOS两个管子这样Gate端共用一个输入,D端相连输出的结构就叫互补MOS结构,CMOS是Complementary Metal Oxide Semiconductor(互补金属氧化物半导体)的缩写。

两个管子的开启电压相同,Vgs(th)N = |Vgs(th)P|。标准的CMOS反相器中,P,N管的各项参数都相同。

基于MOS管的电压,电流传输特性,能够推出CMOS的电压,电流传输特性。

电压传输特性:输出电压Vo随输入电压Vi变化的关系曲线。

电流传输特性:输出漏极电流Id随输入电压Vi变化的关系曲线。

在AB段,Vi<Vtn,NMOS截止,处于截止区,PMOS导通,处于可变电阻区。

在CD段,Vi > VDD - |Vtp|,这是NMOS导通,处于可变电阻区,PMOS截止,处于截止区。

在BC段,从左到右,B~1/2Vdd阶段,NMOS处于饱和区(Vi大于Vtn,Vds由于PMOS的导通比较大,直接进入饱和区),PMOS处于可变电阻区(由于Vi变大,PMOS导通程度降低)

在BC段,从左到右,1/2Vdd阶段,由于Vi的逐渐增大,NMOS依然处于处于饱和区,PMOS也进入了饱和区。

在BC段,从左到右,1/2Vdd~C阶段,NMOS导通程度增大,处于可变电阻区,PMOS导通程度降低,Vds逐渐增大,进入饱和区。

在BC段,NMOS.PMOS同时导通,若N,P参数完全对称,那么Vi = 1/2Vdd 时,Vo = 1/2Vdd。

当Vtn<Vi < VDD -Vtp时,即图中的BC段,两个管子都处于饱和区,Id电流最大,会出现一个电流峰值,产生动态功耗。

Q4:CMOS的 输入噪声容限是什么?

在电压特性曲线中,在Vi从0上升到Vtn的过程中,输出Vo高电平维持一段时间没有变化。

在Vi从理想的高电平Vdd减小Vtp的期间,输出Vo低电平也维持一段时间没有变化。

因此,CMOS反相器对输入允许有一定的波动范围,在此范围内都能够输出有效的高,低电平。

而CMOS输出的时候,由于MOS管的导通电阻,输出高电平的时候,会产生分压,电位降低一点。输出低电平的时候,电位会被抬高一点。

所以输出高低电平有一定的误差,由于器件参数的分散性,相同条件下相同型号输出的低电平也略有区别,但是最大不会超过Vol(max)。输出高电平的最小值不会低于VoH(min)。

输出误差和输入波动范围就一起定义了CMOS的输入噪声容限。

例如,在74HC系列CMOD集成电路在5V工作电压时的参数。

输入高电平的噪声容限 VNH =VOH(min) -V IH(min) = 4.9V - 3.5V =1.4V

输入低电平的噪声容限 VNL =VIL(max) -V OL(maz) = 1.5V - 0.1V =1.4V

当P,NMOS的参数完全对称时,噪声容限也是相同的

当增大电源电压时,能够提高噪声容限,但是同时也增大了动态功耗。

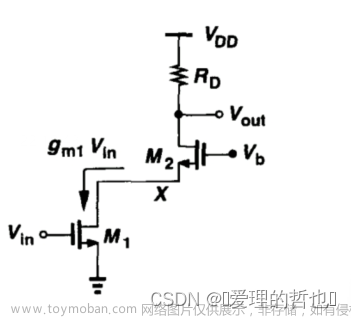

Q5:CMOS结构中P管的宽长比W/L为什么比N管的大?

首先L是指源漏之间的栅长尺寸,与之垂直的栅的尺寸叫做W。

un表示迁移率,Cox是单位面积栅氧化层电容。

由于NMOS管中多子是空穴,少子是电子,而PMOS的多子是电子,少子是空穴文章来源:https://www.toymoban.com/news/detail-415022.html

所以在Gate接入电压,Nmos中电子形成导电沟道,Pmos用空穴形成导电沟道,电子的迁移能力比空穴强,在相同的电场强度下,想要形成相同的导通电阻的话,Pmos的导电沟道宽长比(W/L)要做的比Nmos大,才能得到相同的导通电阻。文章来源地址https://www.toymoban.com/news/detail-415022.html

到了这里,关于CMOS反相器基础(数字电路学习笔记)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!