IP核:89C51

FPGA芯片类型:EP4CE6E22CN8

FPGA_LED12 交替亮灭 灯

总体过程描述

先创建

工程1生成51IP核的原理图符号,供工程2使用。再建另一个工程2创建原理图,把所需要的符号都添加进来 或者 利用宏功能生成添加。(除了51IP核,其余的都可以利用宏功能生成添加)再将其烧录进FPGA,配合keil软件生成的.hex文件来调试。

1、下载文件—移动位置

把老师提供的资料中的mc8051文件夹下的vhdl文件夹, 放在你自己

放在你自己新建的要用来烧录的my8051_test文件夹下

其它文件我们本次是用不到的,不用管。

2、创建project1

这一步是 为了获取 51IP核的原理图符号

就是基本的新建工程嘛

【File】--【New Project ...】基本操作啊不

注意:不这样选的话后面的51IP核可能会通过不了哦,会报引脚数目不对的错误

2.1 添加文件

创建好了 是一个空的工程 点击【Assignments】--【setting】--【General】--找到右侧的【...】---找到你工程目录下刚刚添加的 vhdl文件夹--把文件添加进去

添加文件时候可以全选

【ctrl+A】然后按住【ctrl】把带有cfg的文件 和 最底下的带有top的文件取消选择

2.2 重新设置顶层文件

找到mc8051_core.vhd 【右键】设置为顶层文件

2.3 编译

然后就是等待了

2.4 生成符号

生成完以后,你会发现在工程目录下多了一个.bsf文件

project1中的工作告一段落

3、创建project2

这一步是 为了获得单片机最小系统

就是基本的新建工程嘛

【File】--【New Project ...】基本操作啊

此处的命名可以随意 别和上一个一样就行

这里的芯片选型要和自己FPGA开发板上的一样了,因为我们是要烧录这个工程生成的文件的,型号必须适配。

!!!这也是project1的初始创建的唯一不同的地方!!!

3.1在新工程下创建原理图

【File】--【New】 创建一个空白的图

3.2 再次添加文件

重复project1的步骤即可

3.3 添加&宏功能模块_生成 符号

点开这个会发现,已经存在mc8051_core 这个就是你 project1中生成的

,先把它放在原理图中吧,随便放一个位置就行

其它的还没有,因为还需要我们自己弄

3.3.1 宏功能模块_生成计数器

看着符号图应该就能做出来的吧 基本操作哦!

3.3.2 宏功能模块_锁相环

看着符号图应该就能做出来的吧 基本操作哦!

3.3.3 宏功能模块_ROM

看着符号图应该就能做出来的吧 基本操作哦!

a. 注意点 导入.hex文件 & ROM ID的设置

生成这个要添加数据文件--我们可以用keil软件生成 .hex文件,不加会生成不了!!!

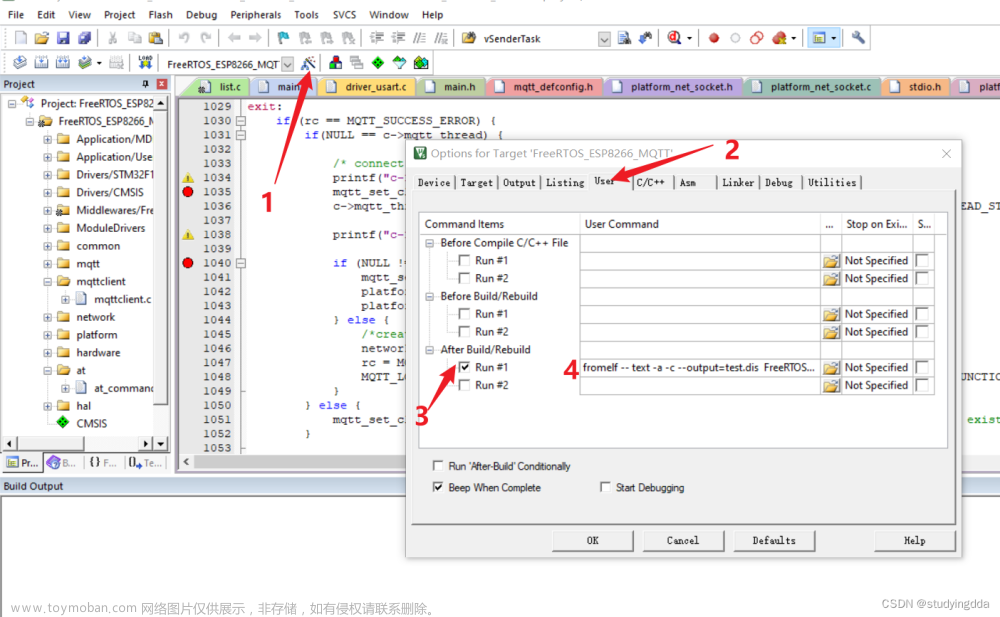

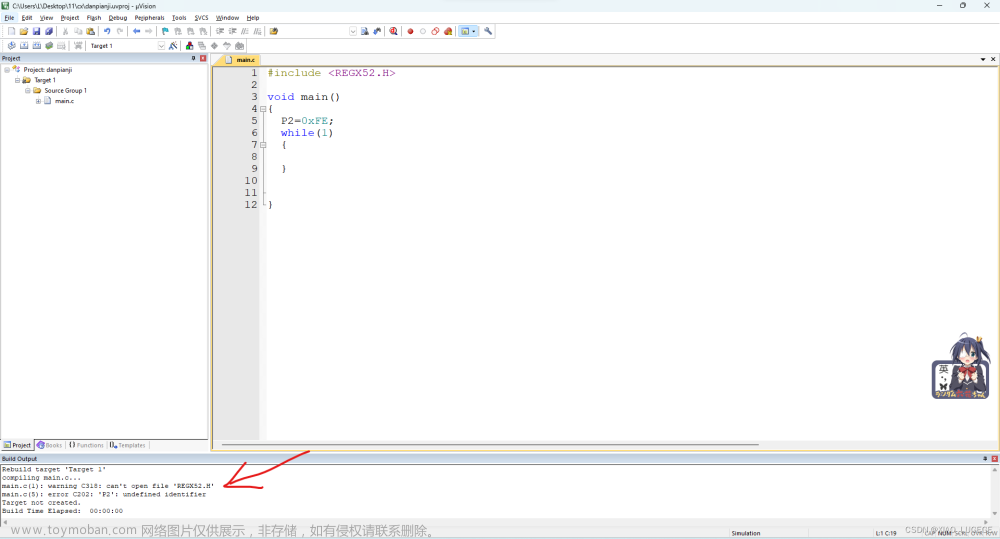

b. 生成.hex文件

把下面这段代码赋值到keil软件中 编译就可以生成.hex文件

不过记得要设置好 才能生成 .hex文件

#include <reg51.h> //此文件中定义了51的一些特殊功能寄存器

#define LED1 P1

#define LED2 P2

void Delayms(unsigned int cnt); //@11.0592MHz

void main()

{

while(1)

{

LED1 = 0x00; //控制D2口 低亮高灭

Delayms(500);

LED1 = 0xff; //置P1口为高电平

Delayms(500); // 调用延时程序

LED2 = 0x00; //置P2口为高电平

Delayms(500); // 调用延时程序

LED2 = 0xff; //置P2口为高电平

Delayms(500); // 调用延时程序

}

}

/*******延时函数*************/

void Delayms(unsigned int cnt) //@11.0592MHz

{

unsigned char i, j, k;

while(cnt--)

{

i = 11;

j = 190;

do

{

while (--j);

} while (--i);

}

}

3.3.4 宏功能模块_RAM

3.4 原理图连线

图有点大 直接截 截不清楚 分部分来吧

3.4.1 左半部分

3.4.2 右半部分

此处将

MCU的P2_OUT[0]设置为LED2的口 对应我们写keil程序的P2P1_OUT[0]设置为LED1的口对应我们写keil程序的P1(我下面有代码)

3.4.3 下半部分

整体原理图

编译原理图工程

和project1一样的操作。。。静静等待。。。。

4、配置引脚

可以根据原理图来配置 或者 看老师给的表格

!!!这样配置!!!

4.1 引脚仿真

看这样配IO 行不行

5、再次编译工程

和project1一样的操作。。。静静等待。。。。

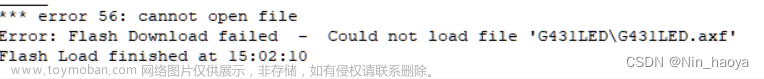

6、烧录原理图程序

6.1 选择.sof文件

烧录完以后可以看到 初始放进 ROM代码 产生的现象了文章来源:https://www.toymoban.com/news/detail-416391.html

7、烧录.hex 替换原来ROM中的文件 观察现象

文章来源地址https://www.toymoban.com/news/detail-416391.html

文章来源地址https://www.toymoban.com/news/detail-416391.html

每天进步一点点 笔记仅供自学,用来回看复习,不一定适合你,如有错误请指出。

到了这里,关于【FPGA】51的IP核烧进FPGA,配合keil生成的.hex文件调试的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!