目录

实验1 存储器实验

一、实验目的

二、实验原理

三、实验电路

四、实验步骤

五、实验数据分析

六、思考题

实验1 存储器实验

一、实验目的

1.熟悉DVCC计算机组成原理实验机的结构,掌握其主要操作。

2.掌握静态随机存储器RAM工作特性。

3.掌握静态随机存储器RAM的数据读写方法。

4.能够运用静态随机存储器进行单步读、写和连续读、写数据。

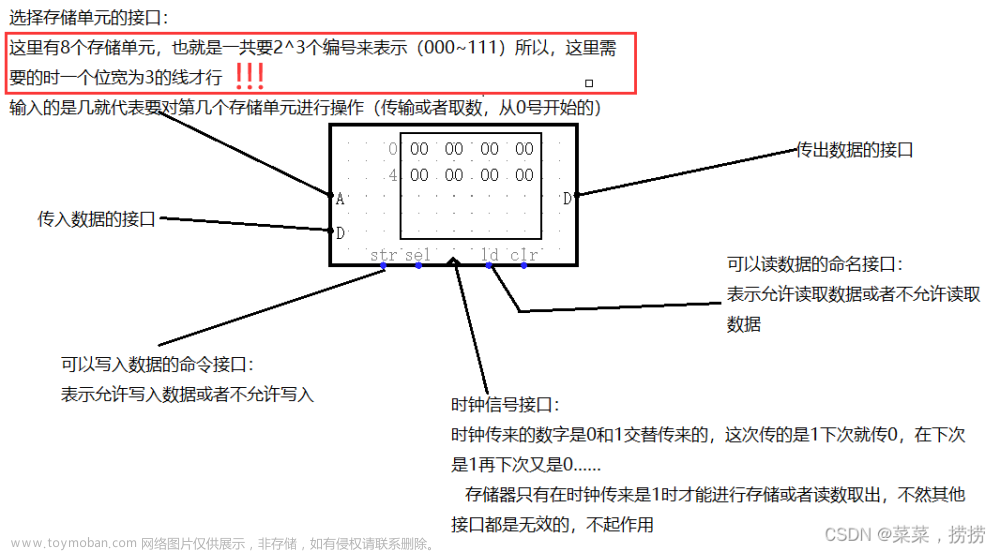

二、实验原理

1.主存储器单元电路主要用于存放实验机的机器指令,它的数据总线挂在外部数据总线EXD0~EXD7上;它的地址总线由地址寄存器单元电路中的地址寄存器74LS273(U37)给出,地址值由8个LED灯LAD0~LAD7显示,高电平亮,低电平灭;在手动方式下,输入数据由8位数据开关KD0~KD7提供,并经一三态门74LS245(U51)连至外部数据总线EXD0~EXD7,实验时将外部数据总线EXD0~EXD7用8芯排线连到内部数据总线BUSD0~BUSD7,分时给出地址和数据。它的读信号直接接地;它的写信号和片选信号由写入方式确定。该存储器中机器指令的读写分手动和自动两种方式。手动方式下 ,写信号由W/R` 提供,片选信号由CE`提供;自动方式下,写信号由控制CPU的P1.2提供,片选信号由控制CPU的P1.1提供。

2.由于地址寄存器为8位,故接入6264的地址为A0~A7,而高4位A8~A12接地,所以其实际使用容量为256字节。6264有四个控制线:CS1 第一片选线、CS2第二片选线、OE读线、WE写线。其功能如表3-1所示。CS1片选线由CE`控制(对应开关CE)、OE读线直接接地、WE写线由W/R`控制(对应开关WE)、CS2直接接+5V。

1.6264静态存储器:

(1)芯片功能:

6264芯片是一个高性能CMOS静态RAM,由8192个存储单元组成。

(2)芯片引脚:

13个地址线::A12~A0

8个数据线:D7~D0

(CE)`:片选信号,低电平有效

CS:片选信号,高电平有效

(OE)`:读允许信号,低电平有效

(WE)`:写允许信号,低电平有效

存储容量:8K*8b=8KB

(3)功能表:

| 模式 |

(CE)` |

CS |

(WE)` |

(OE)` |

D7~D0 |

| 无效信号 |

1 |

* |

* |

* |

高阻态 |

| 无效信号 |

* |

0 |

* |

* |

低阻态 |

| 写 |

0 |

1 |

0 |

1 |

输入 |

| 读 |

0 |

1 |

1 |

0 |

输出 |

2.74LS273芯片:

(1)芯片功能:

74LS273芯片是一个高8位寄存器,由八个D型触发器组成,具有时钟脉冲和异步复位的功能。

(2)芯片引脚:

CLK: 时钟脉冲输入,上升沿有效

D0~D7:数据输入端

Q0~Q7:触发器输出端

MR:复位端,低电平有效

(3)功能表:

| MR |

CLK |

Dn |

Qn |

| 0 |

X |

X |

0 |

| 1 |

↑ |

1 |

1 |

| 1 |

↑ |

0 |

0 |

3.74LS245:

(1)芯片功能:

8路同相三态双向总线收发器,可双向传输数据. 根据方向控制(DIR)输入的逻辑电平,允许从A总线到B总线或从B总线到A总线的数据传输。

(2)芯片引脚:

(CE)`:片选信号,低电平有效

DIR:方向控制端

AB/(BA)`:信号传输方向

(3)功能表:

| (CE)` |

方向AB/(BA)` |

状态 |

| 0 |

0 |

B数据到A总线 |

| 0 |

1 |

A数据到B总线 |

| 1 |

↑ |

隔离 |

图中信号线LDAR由开关LDAR提供,手动方式实验时,跳线器LDAR拨在左边,脉冲信号T3由实验机上时序电路模块TS3提供,实验时只需将J22跳线器连上即可,T3的脉冲宽度可调。

三、实验电路

1、实验接线图

⑴ MBUS连BUS2; ⑵ EXJ1连BUS3;

⑶ 跳线器J22的T3连TS3; ⑷ 跳线器J16的SP连H23;

⑸ 跳线器SWB、CE、WE、LDAR拨在左边(手动位置)。

存储器实验接线图

2、实验原理图

四、实验步骤

1.连接实验线路,仔细查线无误后接通电源。

2.形成时钟脉冲信号T3,方法如下:在时序电路模块中有两个二进制开关“运行控制”和“运行方式”。将“运行控制”开关置为“运行”状态、“运行方式”开关置为“连续”状态时,按动“运行启动”开关,则T3有连续的方波信号输出,此时调节电位器W1,用示波器观察,使T3输出实验要求的脉冲信号;本实验中“运行方式”开关置为“单步”状态,每按动一次“启动运行”开关,则T3输出一个正单脉冲,其脉冲宽度与连续方式相同。

3.给存储器的00地址单元中写入数据05,具体操作步骤如下:

4.读出刚才写入00地址单元的内容,观察内容是否与写入的一致。具体操作步骤如下:

五、实验数据分析

1、记录向存储器写入数据的操作过程。

按照前面介绍的实验步骤向存储器地址为00H, 01H,02H的存储单元分别写入组内同学学号的后两位,则在00H存储单元写入05H,在01H存储单元写入49H,在02H存储单元写入01H。

2、读出存储器单元内容,使用手机拍照记录读出的数据,并记录在下表中。

| 地址 |

内容 |

地址 |

内容 |

| 00H |

|

01H |

|

| 02H |

|

六、思考题

1、静态随机存储器采用是什么原理存放信息,存放在存储器中的信息需要刷新吗,为什么?

静态随机存储器是用触发器工作原理存储信息的,信息读出后,它仍然保持原状态,不需要再生,但电源掉电时,原存信息丢失,所以它属于易失性半导体存储器,存放在存储在存储器中的信息不需要刷新。

2、分析本实验中,SRAM 6264 最大存储容量是多少?实际存储容量是多少?为什么?

最大存储容量: *8位=8K*8b=8KB 实际存储器容量:

*8位=8K*8b=8KB 实际存储器容量: *8位=256*8b,因为其它5个地址线接地了。

*8位=256*8b,因为其它5个地址线接地了。

3、计算机中什么器件采用静态随机存储器 ?什么器件采用动态随机存储器?

静态随机存储器:计算机内部的CPU高速缓存(Cache)、硬盘缓存区、LCD显示器、打印机等;文章来源:https://www.toymoban.com/news/detail-417332.html

动态随机存储器:计算机的主存等。文章来源地址https://www.toymoban.com/news/detail-417332.html

到了这里,关于计算机组成原理实验 实验一 存储器实验的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!