👉个人主页: highman110

👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

目录

1芯片简介

2引脚定义

3功能框图

4器件操作

4.1操作框图

4.2标准SPI

4.3DaulSPI

4.4QaudSPI

4.5QPI

4.6DTR(W25Q128不支持)

4.73-字节/4-字节地址模式(W25Q128只支持3字节)

4.8保持功能

4.9软复位和硬复位

4.10XIP

当下的norflash芯片外部一般都是采用SPI串行接口,并口的用的比较少,后续有机会再分享。下面以常用的华邦W25Q128FV为例,分享下这颗spinorflash的相关特性。

1芯片简介

这是一片128Mbitnorflash,整片包括65536个256字节的可编程page,支持4KB的sector扇区(16个page组成)擦除、32KB(128个page组成)/64KB(256个page组成)的block区块擦除或整片擦除。外部接口支持SPI、DaulSPI、QuadSPI、DPI。

2引脚定义

芯片有多种不同封装形式,这个不列了,大家自行查阅数据手册。常用的是宽体SOIC-8208mil,引脚定义如下:

| No. |

PINNAME |

I/O |

FUNCTION |

| 1 |

CS# |

I |

片选使能 |

| 2 |

DO(DQ1) |

I/O |

串行数据输出(数据输入输出端口DQ1)(1) |

| 3 |

WP#(DQ2) |

I/O |

写保护输入(数据输入输出端口DQ2)(2) |

| 4 |

VSS |

- |

地 |

| 5 |

DI(DQ0) |

I/O |

串行数据输入(数据输入输出端口DQ0)(1) |

| 6 |

CLK |

I |

串行时钟输入 |

| 7 |

HOLD#/RESET#(DQ3) |

I/O |

保持/复位(数据输入输出端口DQ3)(2) |

| 8 |

VCC |

- |

电源输入 |

注:

1、DQ1~0在DualSPI指令有效。

2、DQ3~0在QuadSPI/QPI指令有效。

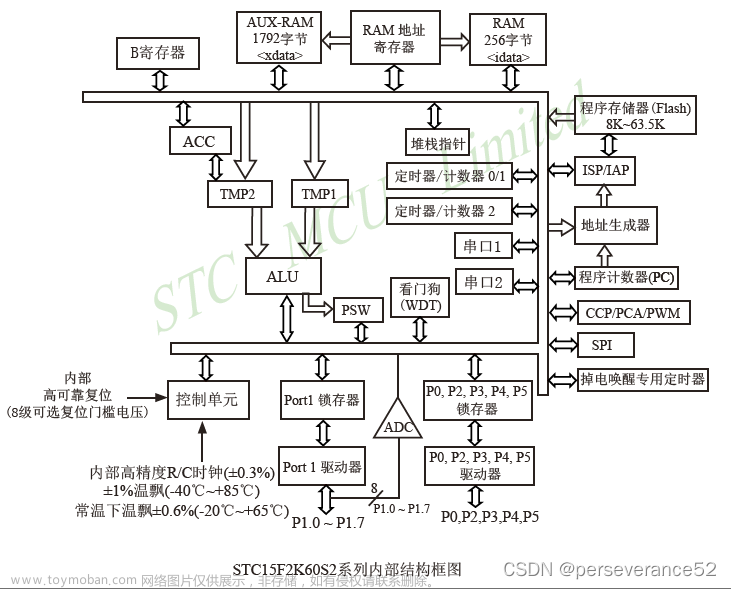

3功能框图

1、SPIcommand&controlLogic:进行SPI串行数据解析,得到得到页地址(可以理解为选中字线)、字节地址(业内偏移地址,可以理解为选中位线)、数据、命令;

2、StatusRegister:片内的状态寄存器;

3、WriteControlLogic:写保护控制逻辑;

4、HighVoltageGenerators:电荷泵生成内部高压,用于存储单元的擦除和读写;

5、PageAddressLatch:页地址锁存

6、ByteAddressLatch:字节地址锁存

7、WriteProtectLogicandrowdecode:写保护逻辑和行解码,行即为字线。

8、Columndecodeand256bytepagebuffer:列解码和256KB页buffer,列即为位线,从这可以看出flash内部的读写是以page为单位。我理解为一页即为一根字线下挂的256*8个存储单元,也即256*8根位线。

9、存储阵列:一共256个64KBblock,每个block有16个4KB的sector。

10、SFDPregister:256字节串行Flash可发现参数(SFDP)寄存器,包含器件配置信息、可用指令和其他特性。

11、Securityregister:芯片提供3个256字节的安全寄存器,用于存储制造信息或其他重要信息,此寄存器可以单独编程或擦除。

4器件操作

4.1操作框图

这是从另一款芯片手册上截下来的图,W25Q128这款不支持4字节地址模式,所以换了这个图能更全面的说明spinorflash的操作特性。

4.2标准SPI

标准SPI接口总线通过CLK、CS#、DI和DO进行访问。W25Q128支持SPI模式0和模式3的操作。当SPI总线控制器处于待机状态不传送数据时,模式0下的时钟信号SCK为低,而模式3下的时钟信号CLK为高。在两种模式下,DI上的数据都是在时钟上升沿被采样,DO上的数据在时钟下降沿输出。如下图所示:

4.3DaulSPI

支持DualSPI操作指令包括“双口输出快速读(3Bh)”、“双口I/O快速读(BBh)”、“4-字节双口输出快速读(3Ch)”、“4-字节双口I/O快速读(BCh)”、“双口输出DTR快速读(3Dh)”、“双口I/ODTR快速读(BDh)”、“4-字节双口输出DTR快速读(3Eh)”、“4-字节双口I/ODTR快速读(BEh)”。这些指令允许数据输入或输出达到普通SPI两倍的速度。双口读指令是快速下载数据到RAM或直接从SPI总线上本地执行非关键速度代码的理想操作。当使用双口SPI指令时,DI和DO引脚成为双向I/O引脚DQ0和DQ1。

以上4字节命令和DTR命令,W25Q128不支持。

4.4QaudSPI

支持QuadSPI操作指令包括“四口输出快速读(6Bh)”、“四口I/O快速读(EBh)”、“4-字节四口输出快速读(6Ch)”、“4-字节四口I/O快速读(ECh)”、“四口输出DTR快速读(6Dh)”、“四口I/ODTR快速读(EDh)”、“4-字节四口输出DTR快速读(6Eh)”、“4-字节四口I/ODTR快速读(EEh)”。QuadSPI读指令在连续和随机访问速度有极大提高,允许快速代码映射到RAM或直接从SPI总线上执行代码(XIP)。当使用QuadSPI指令时,DI、DO、WP#和HOLD#引脚成为双向I/O引脚DQ0、DQ1、DQ2、DQ3。QuadSPI模式要求状态寄存器2中的“QE位”必须设置为1。

以上4字节命令和DTR命令,W25Q128不支持。

4.5QPI

支持完全的四口模式(QuadPeripheralInterface-QPI),即所有指令、地址输入、数据输入输出都为四口。“启用QPI(35h)”指令可以使器件从标准/Dual/QuadSPI模式切换到QPI模式,SPI模式和QPI模式不会同时生效。由于QPI模式下只需要2个时钟输入指令,在XIP应用中可提升系统性能。SPI和QPI模式间通过“启用QPI(35h)”指令和“禁用QPI(35h)”进行切换,也可以通过NVCR和ENVCR寄存器中的“QPI模式位”进行设置.上电、硬件复位或软件复位后,器件的默认模式受NVCR寄存器中的“QPI模式位”控制。当使用QPI指令时,DI、DO、WP#和HOLD#引脚成为双向I/O引脚:DQ0、DQ1、DQ2、DQ3。QPI模式要求状态寄存器2中的“QE位”必须设置为1。

4.6DTR(W25Q128不支持)

为了在不增加时钟频率时有效提高读操作数据带宽,支持标准/Dual/QuadSPI和QPI模式的DTR读操作。DTR读操作时的指令输入和正常的SPI/QPI模式一样,只在时钟上升沿采样指令,一旦DTR指令生效,地址输入和数据输出同时在时钟上升沿和下降沿有效。

4.73-字节/4-字节地址模式(W25Q128只支持3字节)

3-字节地址模式用于兼容256M位容量以下串行SPINORFLASH存储器。为了在3-字节地址模式访问128M位容量以上地址,必须联合使用“扩展地址寄存器(ExtendedAddressRegister)”。4-字节地址模式可以支持256M位到32G位容量,而不需要设置“扩展地址寄存器(ExtendedAddressRegister)”。器件在上电后由“NVCR寄存器”中的“ADP位”确定地址模式处于3-字节地址模式或4-字节地址模式。如果ADP=0,器件工作在3-字节地址模式;如果ADP=1,器件工作在4-字节地址模式。出厂时ADP=0。可通过“进入4-字节地址模式”或“退出4-字节地址模式”进行3-字节和4-字节地址模式切换。标志寄存器(FlagRegister)中的“ADS位”表示器件当前所处的地址模式,“ADS=0”指示3-字节地址模式,“ADS=1”指示4-字节地址模式。

4.8保持功能

在标准/DualSPI模式下,HOLD#信号允许在片选有效时(CS#=0)暂停操作。HOLD功能可以用于器件的数据和时钟管脚与其它器件共享的情况。比如,执行页编程指令过程中仅将部分数据写入缓冲区时,系统中产生了一个更高优先级的中断要求使用SPI总线。在这种情况下,HOLD#功能可以保存当前指令的执行状态以及缓冲区中的数据,当总线可用时恢复指令写入。要进入HOLD状态,CS#必须为低。如果此时CLK信号为低,则芯片会在HOLD#的下降沿进入HOLD状态,否则芯片在下一个时钟的下降沿进入HOLD状态。如果HOLD#的上升沿时CLK为低,则芯片结束HOLD状态,否则芯片在下一个下降沿时结束HOLD状态。在HOLD状态下,串行数据输出脚(DO)为高阻态,串行数据输入脚(DI)和串行时钟脚(CLK)被忽略。片选信号(CS#)在整个HOLD期间必须为低以避免芯片内部逻辑状态被复位。

4.9软复位和硬复位

在SPI或QPI模式下,都可以通过软复位指令序列(包含2个连续指令:使能复位指令“66h”和复位指令“99h”)、硬件复位(HOLD#/RESET#引脚)可以把器件初始化成上电状态。复位过程中除了读状态寄存器,其他指令无效。状态寄存器2中的“HOLD/RST位”可以把HOLD#引脚配置为HOLD#功能或者硬件复位功能。当HOLD/RST=0(出厂默认),HOLD#已经作为HOLD功能引脚;当HOLD/RST=1时,HOLD#作为硬件复位RESET#引脚。维持RESET#低约1us可以把器件复位为上电后的初态。复位可以终止任何的编程、擦除操作,如果编程、擦除中被复位,被操作区域的数据可能会被破坏,需要重新进行编程或擦除操作。当RESET#维持低时,器件不接受任何指令。如果状态寄存器2中的“QE位”为1时,HOLD#将作为DQ3,“HOLD/RST位”无意义。

注意:

1.当RESET#维持低电平小于1us时(几百ns),也可能会触发复位,但是为了稳定可靠复位,建议RESET#维持低电平不小于1us。

2.当器件在擦除、编程过冲中或挂起时接受到复位操作,数据可能会收到破坏。建议复位前先检查状态寄存器1的“WIP位”和标志寄存器中的编程和擦除“SUS位”。

4.10XIP

XIP模式只需要输入地址(不需要指令)就可访问特定地址读出数据,减少随机访问时间,所有的快速读操作都支持XIP操作。为了灵活性,支持多种进入、退出XIP模式。如果需要上电后立即进入XIP模式,需要设置NVCR寄存器中的“XIP模式位”。

为了启用XIP模式,需要2个步骤。首先设置VCR寄存器的“XIP位”(bit3)为0,然后在读操作阶段设置“XIP确认位”(bX)为0,之后XIP模式生效。一旦进入XIP模式,CS#变低后马上跟随地址(不接受指令)。通过设置“XIP确认位”为1退出XIP模式。退出XIP模式时,VCR寄存器的“XIP位”(bit3)会自动恢复到默认状态1。JFM25QL256/EFM25QL256支持上电立即进入XIP模式,需要通过NVCR的“上电XIP位”(bit[11:9])设置,只支持QuadIO模式。跟正常读操作XIP模式一样,上电后进入的XIP模式可通过“XIP确认位”(bX)维持或退出XIP模式。

注:bX是XIP确认位,设置为0保持XIP模式,设置为1则退出XIP模式回到标准的读操作模式(CS#变低后需要读指令进行读操作)。

“XIP确认位”在设置为0或1后可进入或退出XIP模式,位于快速读操作的DUMMY时钟阶段第一拍DQ0数据,时钟上升沿锁存XIP配置。

XIP确认位说明:

| XIP确认位 |

说明 |

| 0 |

进入或维持XIP,即下次读操作仍在XIP模式,不需要指令。 |

| 1 |

退出XIP模式,即下次读操作需要在CS#变低后,输入读指令 |

不同协议下,XIP的影响:

| 协议 |

说明 |

| DualSPI |

DUMMY时钟阶段第一拍DQ1无意义。 |

| QuadSPI或QPI |

DUMMY时钟阶段第一拍DQ3~1无意义。 |

在控制器或存储器复位后退出XIP模式:

如果控制器或存储器异常复位,且存储器是否处于XIP模式,为了退出XIP模式回到待机状态,需进行以下操作:

在QuadSPI或QPI模式下,CS#变低后维持DQ0=1至少7个时钟(3-字节地址模式)或9个时钟(4-字节地址模式),之后CS#变高回到待机状态。

在DualSPI模式下,CS#变低后维持DQ0=1至少13个时钟(3-字节地址模式)或17个时钟(4-字节地址模式),之后CS#变高回到待机状态。

在标准SPI模式下,CS#变低后维持DQ0=1至少25个时钟(3-字节地址模式)或33个时钟(4-字节地址模式),之后CS#变高回到待机状态。

这些序列可以设置“XIP确认位”为1,从而退出XIP模式,器件回到待机状态。文章来源:https://www.toymoban.com/news/detail-417918.html

下一讲继续分享这款芯片的寄存器、写保护操作、指令集等内容,敬请期待!文章来源地址https://www.toymoban.com/news/detail-417918.html

到了这里,关于【FLASH存储器系列五】SPI NOR FLASH芯片使用指导之一的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[深入理解NAND Flash (原理篇)] Flash(闪存)存储器底层原理 | 闪存存储器重要参数](https://imgs.yssmx.com/Uploads/2024/02/735174-1.png)