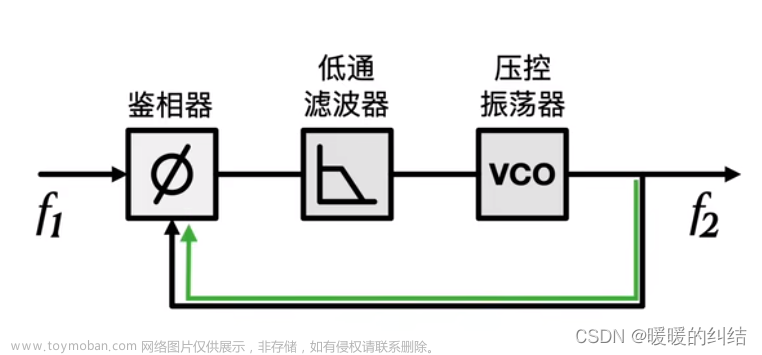

PLL structure

锁相环(PLL, Phase-Locked Loop)包括 三个关键器件: 鉴相器(PD, phase detector)、环路滤波器(loop filter)和压控振荡器(voltage-controlled oscillator)。鉴相器把周期性输入信号的相位与压控振荡器信号的相位进行比较;PD的输出信号是这两个输入信号之间的相位误差的度量。之后该误差e(t)由环路滤波器进行滤波,而环路滤波器的输出被用作控制电压送入VCO。控制电压通过VCO改变其输出的振荡频率,以减小输入信号与VCO 输出之间的相位误差。

当环路被锁定时,控制电压把VCO的输出频率的平均值调整到与输入信号频率的平均值完全一样。锁相并非意味着零相位误差,只能说PLL的锁定状态后的输出信号与参考信号同频,基本同相(如果完全同频同相,零相位误差的话,VCO的控制电压为0,则会输出由电路自身决定的自由振荡频率,如果VCO控制灵敏度极高,则只需要很小的相位误差即可维持频率锁定,可理解是基本同相)。

PLL Classifications

LPLL(APLL):如果一个线性元器件(如四象限乘法器)用作鉴相器,并且环路滤波器与VCO也为模拟元件,则称为模拟或线性PLL。

DPLL:使用数字鉴相器(EXOR栅极或J-K触发器)并且其他元器件保持不变,称为数字滤波器

ADPLL:如果PLL完全用数字模块构建,不带任何无源器件或线性元件,称为全数字PLL

SPLL: 由软件执行并在DSP上运行的称为软件PLL

3.PD-Phase Detector

PLL的核心是鉴相器PD(有时也称鉴频鉴相器PFD),PFD将输入到PLL的Fref的频率与相位与PLL输出值RFout经过反馈通道到PFD的频率与相位进行比较,当比较结果处于稳态,即认为PLL被锁定。

鉴相器的电路类型有很多,最常见的有以下三种电路:

(1)模拟乘法器鉴相器,常用于鉴相器的两路输入信号均为正弦波的PLL电路中

(2)异或门鉴相器,适合两路输入信号均为方波信号的PLL电路,常用于DAPLL。

异或门电路:两路输入相异时,输出结果为1

(3)边沿触发型数字鉴相器,属于数字电路型鉴相器,对输入信号要求不严,可以是方波,可以是矩形脉冲波,常用与高频DPLL中。

4. LF-Loop Filter

LF环路滤波器从实质上讲是低通滤波器,其作用是鉴相器输出的误差电压中的高频及干扰成分,得到低频直线电压,输入至VCO。

比较常用的三种环路滤波器电路如图所示。

a )是简单RC滤波器 ,b) 是RC比例积分滤波器,c) 是有源比例积分滤波器,

三种电路的复杂性依次增加,滤波效果同样依次增加。

5. VCO -Voltage Controlled Oscillator

VCO压控振荡器是PLL的被控对象。VCO是一个电压—频率变换装置,在环路中作为频率可调振荡器,其振荡频率应随输入控制电压线性地变化。它输出的信号根据锁相环的不同要求,可分为正弦波压控振荡器与非正弦波压控振荡器两大类。

正弦波压控振荡器一般由LC点式振荡器与变容二极管组成。变容二极管的容值随外部控制电压而改变,在LC谐振电路中,输出的谐振频率与电容值相关。由于正弦波VCO受到变容二极管结电容变化范围的限制,因此一般振荡频率变化范围都不是太大。

非正弦波压控振荡器的种类较多,由于它的频率变化范围大,控制线性好,所以应用比较广泛。这类压控振荡器常见的几种电路有射极定时压控多谐振荡器、积分型施密特压控振荡器、数字门电路压控振荡器。如图所示

6. Three Indicators

(1)相位噪声phase noise、(2)参考杂散spur、(3)锁定时间

Phase noise(dBc/Hz)是指各种随机噪声所造成的瞬时频率或相位的起伏,它决定着频率合成器的短期频率稳定度。主要的噪声源有VCO内部的相噪和输入参考频率的相噪。是在频域定义的,与时域上的Jitter可相互转化。

Spurs是指PLL中的杂散信号,单位dBc。PLL中最常见的杂散信号是参考杂散,这些杂散信号会因为电荷泵源电流和汇电流的失配、电荷泵漏电流以及电源退耦不大而增大。当鉴相频率较低时,由电荷泵的漏电流引起的杂散占主要地位;当鉴相频率较高时,由电荷泵的交替电流(源电流和汇电流)引起的杂散占主要地位。

7. PLL Common Applications

7.1锁相倍频电路

比基本锁相环在反馈路径中多了分频器(1/N),从而允许PLL可以输出Fref倍数的输出频率Fout。分频器也可用在参考路径中,可以使用比PFD频率更高的参考频率,此时称为预分频器(1/P)。在DPLL中,N分频器是一种可编程器件

由N分频器到双模预分频器的改进:

(1)参考计数器(Refence divided 1/R)

在传统的整数N分频频率合成器中,输出频率的分辨率由参考频率决定。例如需要200kHz间距(如GSM电话中),那么参考频率必须为200 kHz。但是,获取稳定的200 kHz频率源并不容易。一种合理的做法是采用基于晶振的良好高频源并对其进行分频。例如从10 MHz频率基准开始并进行50分频,就可以得到所需的频率间隔,这时会用到参考计数器(Refence divided 1/R)。

(2)预分频器(Prescaler 1/P)

随着N分频器的复杂性逐年增加,在超高频领域会使用预分频器。例如需要分频率为10Hz的900MHz的输出,可以使用10MHz的晶振作为高频参考源,R分频器设置为1000,N分频器设置为90000。这也即N分频器中存在至少17位计数器(2^17>90k)才能正常分频,为处理此范围,可在可编程N分频器之前加上一定计数器单元,将超高输入频率拉低至标准CMOS工作频率,该计数器单元称为预分频器。

(3)双模预分频器

使用标准的预分频器会牺牲掉部分性能,系统的分辨率降低(此时最小的可区分间距为F1*P),可以使用双模预分频器来解决这个问题。双模预分频器是一种可通过外部控制信号将分频比从一个值切换为另一个值的计数器(Low为P,High为P+1),通过使用带有A和B计数器的双模预分频器,仍可以保持F1的输出分辨率。

此时分频器的总分频周期为N=A+BP,N可以取到的最大值、最小值由A,B,P决定。例如ADI公司的新型N频率合成器ADF4111,可以通过编程将预分频器的分频比设置为32/33,A计数器为6位(取值0~63),B计数器为13位(取值0~8191),此时N的取值范围为(992~262175)。

(4)小数N频率合成器

许多新兴无线通信系统都要求本振(LO)具有更快的切换能力和更低相位噪声。整数N频率合成器要求参考频率等于通道间距,该值可能非常低(如GSM系统要求Fref=200kHz),意味着反馈通路的N值高。该高N会产生相应较高的相位噪声。低参考频率会限制PLL锁定时间。

小数N合成是在PLL中同时实现低相位噪声和快速锁定时间的一种方式。文章来源:https://www.toymoban.com/news/detail-418122.html

7.2锁相分频电路

与 倍频电路结构相同,需要将分频器改为倍频器。文章来源地址https://www.toymoban.com/news/detail-418122.html

到了这里,关于PLL基础知识介绍的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!