一、概述

为了尽量给甲方降低成本,决定使用较低成本的PHY芯片RTL8201F-VB-CG芯片。移植官网的以太网demo程序,git上下载了一份很好看的rtl8201F的驱动程序,用来替换官方demo的lan8742程序。并没有直接通,于是开始了调试之路。

二、平台

芯片型号:stm32h753

官网例程文件名:STM32Cube_FW_H7_V1.10.0

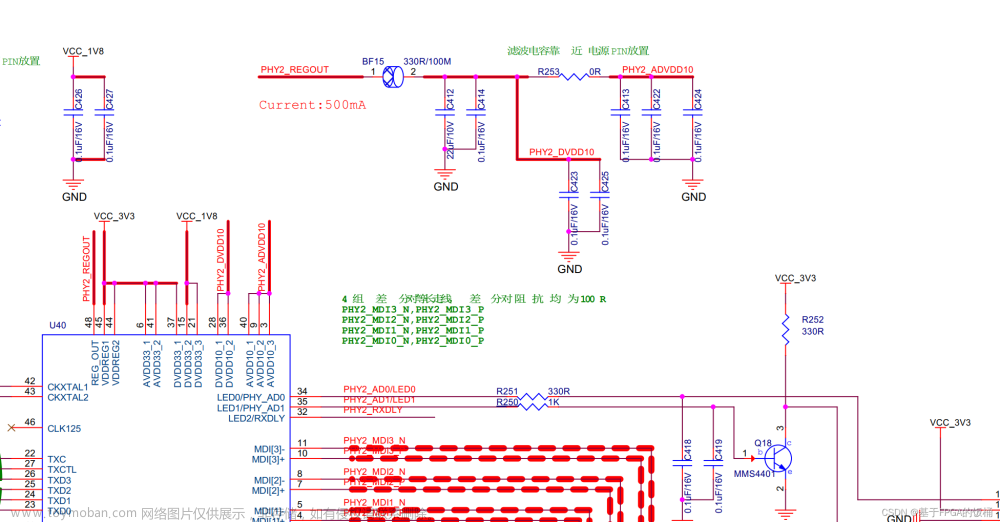

三、原理图

四、遇到的问题

使用官网lwip的demo,下载RTL8201F-VB-CG驱动程序并替换lan8742驱动芯片程序,使用PC机ping设备ping不通

五、调试过程

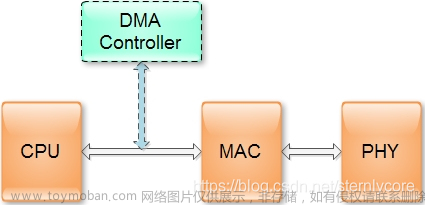

1.确定PHY驱动芯片的寄存器可以读取和写入。

通过函数接口HAL_ETH_ReadPHYRegister和HAL_ETH_WritePHYRegister进行读写。这里我是可以直接正常读写的,所以并没遇到太大阻力。但我还是请教了一下其他朋友,了解到PHY寄存器的读写依靠22,23引脚。22引脚为时钟线,测量波形约2M左右,没记错的话。

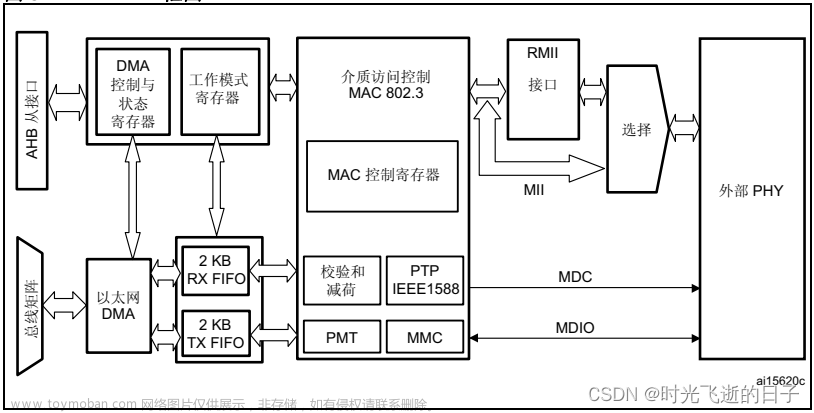

2.深入调试了STM32对于以太网的初始化程序

主要是HAL_ETH_Init函数,先上代码。

HAL_StatusTypeDef HAL_ETH_Init(ETH_HandleTypeDef *heth)

{

uint32_t tickstart;

if (heth == NULL)

{

return HAL_ERROR;

}

if (heth->gState == HAL_ETH_STATE_RESET)

{

heth->gState = HAL_ETH_STATE_BUSY;

#if (USE_HAL_ETH_REGISTER_CALLBACKS == 1)

ETH_InitCallbacksToDefault(heth);

if (heth->MspInitCallback == NULL)

{

heth->MspInitCallback = HAL_ETH_MspInit;

}

/* Init the low level hardware */

heth->MspInitCallback(heth);

#else

/* Init the low level hardware : GPIO, CLOCK, NVIC. */

HAL_ETH_MspInit(heth);

#endif /* (USE_HAL_ETH_REGISTER_CALLBACKS) */

}

__HAL_RCC_SYSCFG_CLK_ENABLE();

if (heth->Init.MediaInterface == HAL_ETH_MII_MODE)

{

HAL_SYSCFG_ETHInterfaceSelect(SYSCFG_ETH_MII);

}

else

{

HAL_SYSCFG_ETHInterfaceSelect(SYSCFG_ETH_RMII);

}

/* Dummy read to sync with ETH */

(void)SYSCFG->PMCR;

/* Ethernet Software reset */

/* Set the SWR bit: resets all MAC subsystem internal registers and logic */

/* After reset all the registers holds their respective reset values */

SET_BIT(heth->Instance->DMAMR, ETH_DMAMR_SWR);

/* Get tick */

tickstart = HAL_GetTick();

/* Wait for software reset */

while (READ_BIT(heth->Instance->DMAMR, ETH_DMAMR_SWR) > 0U)

{

if (((HAL_GetTick() - tickstart) > ETH_SWRESET_TIMEOUT))

{

/* Set Error Code */

heth->ErrorCode = HAL_ETH_ERROR_TIMEOUT;

/* Set State as Error */

heth->gState = HAL_ETH_STATE_ERROR;

/* Return Error */

return HAL_ERROR;

}

}

/*------------------ MDIO CSR Clock Range Configuration --------------------*/

HAL_ETH_SetMDIOClockRange(heth);

/*------------------ MAC LPI 1US Tic Counter Configuration --------------------*/

WRITE_REG(heth->Instance->MAC1USTCR, (((uint32_t)HAL_RCC_GetHCLKFreq() / ETH_MAC_US_TICK) - 1U));

/*------------------ MAC, MTL and DMA default Configuration ----------------*/

ETH_MACDMAConfig(heth);

/* SET DSL to 64 bit */

MODIFY_REG(heth->Instance->DMACCR, ETH_DMACCR_DSL, ETH_DMACCR_DSL_64BIT);

/* Set Receive Buffers Length (must be a multiple of 4) */

if ((heth->Init.RxBuffLen % 0x4U) != 0x0U)

{

/* Set Error Code */

heth->ErrorCode = HAL_ETH_ERROR_PARAM;

/* Set State as Error */

heth->gState = HAL_ETH_STATE_ERROR;

/* Return Error */

return HAL_ERROR;

}

else

{

MODIFY_REG(heth->Instance->DMACRCR, ETH_DMACRCR_RBSZ, ((heth->Init.RxBuffLen) << 1));

}

/*------------------ DMA Tx Descriptors Configuration ----------------------*/

ETH_DMATxDescListInit(heth);

/*------------------ DMA Rx Descriptors Configuration ----------------------*/

ETH_DMARxDescListInit(heth);

/*--------------------- ETHERNET MAC Address Configuration ------------------*/

/* Set MAC addr bits 32 to 47 */

heth->Instance->MACA0HR = (((uint32_t)(heth->Init.MACAddr[5]) << 8) | (uint32_t)heth->Init.MACAddr[4]);

/* Set MAC addr bits 0 to 31 */

heth->Instance->MACA0LR = (((uint32_t)(heth->Init.MACAddr[3]) << 24) | ((uint32_t)(heth->Init.MACAddr[2]) << 16) |

((uint32_t)(heth->Init.MACAddr[1]) << 8) | (uint32_t)heth->Init.MACAddr[0]);

heth->ErrorCode = HAL_ETH_ERROR_NONE;

heth->gState = HAL_ETH_STATE_READY;

return HAL_OK;

}

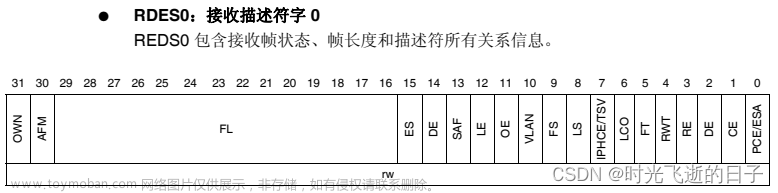

在该代码的这一段发现程序返回了错误。于是查找手册对比这个bit位的作用

while (READ_BIT(heth->Instance->DMAMR, ETH_DMAMR_SWR) > 0U)

{

if (((HAL_GetTick() - tickstart) > ETH_SWRESET_TIMEOUT))

{

/* Set Error Code */

heth->ErrorCode = HAL_ETH_ERROR_TIMEOUT;

/* Set State as Error */

heth->gState = HAL_ETH_STATE_ERROR;

/* Return Error */

return HAL_ERROR;

}

}

3.获取手册上关于这个bit位的描述

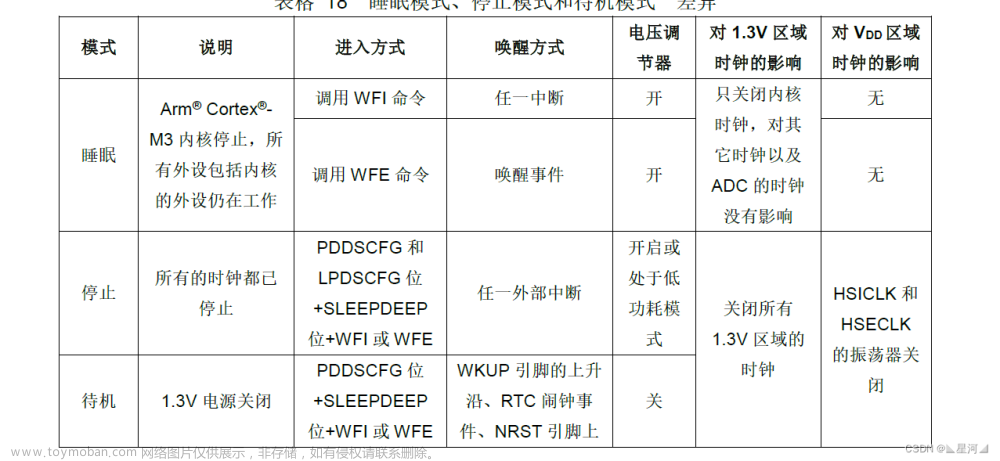

手册上关于这个bit位的描述如下,我的理解是,芯片需要检查所有的时钟,在检测到时钟的情况下,会自动复位完成。

4.测量PHY芯片各个时钟线的状态

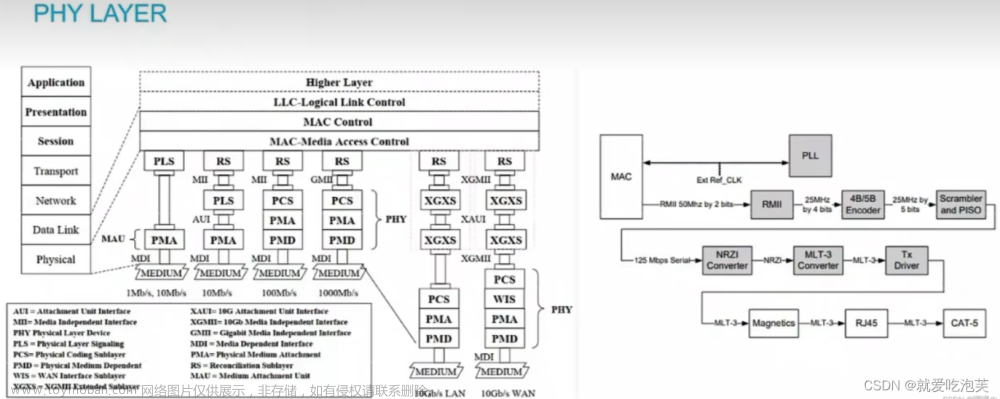

通过向朋友的学习,测量了PHY芯片15引脚的时序,因为使用RMII模式,所以该时钟引脚理论值约为50M。而我的这次调试,问题的根源也在这里。

在运行程序时,我测量了PHY芯片15引脚,发现该引脚有时钟输出,我就误认为这里的时钟没问题,后面总结过后,才发现是寄存器配置后,PHY芯片的时钟才开始输出。所以在测量时,最好是打断点进行调试,断点要打在HAL_ETH_Init初始化之前。

5.阅读PHY芯片手册,找到在HAL_ETH_Init初始化之前提供时钟的办法

通过查看PHY芯片的芯片手册,关于该芯片12引脚的描述如下,在该引脚拉低或者浮空(芯片内部默认接地)的情况下,15引脚会默认输出时钟信号

六、解决的办法

将12引脚的上拉电阻去掉。stm32h7检测到PHY芯片的时钟信号后,以太网驱动的初始化会正常进行。再ping设备,通了!!!文章来源:https://www.toymoban.com/news/detail-419152.html

七、总结

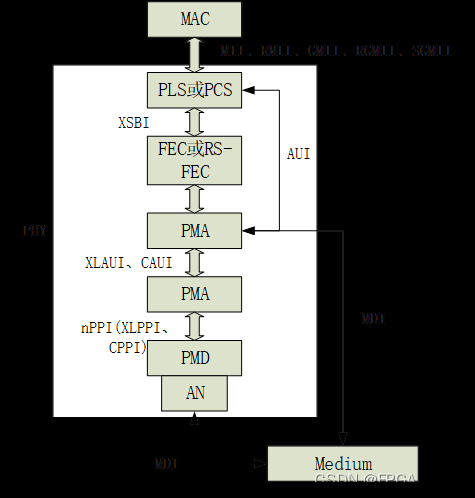

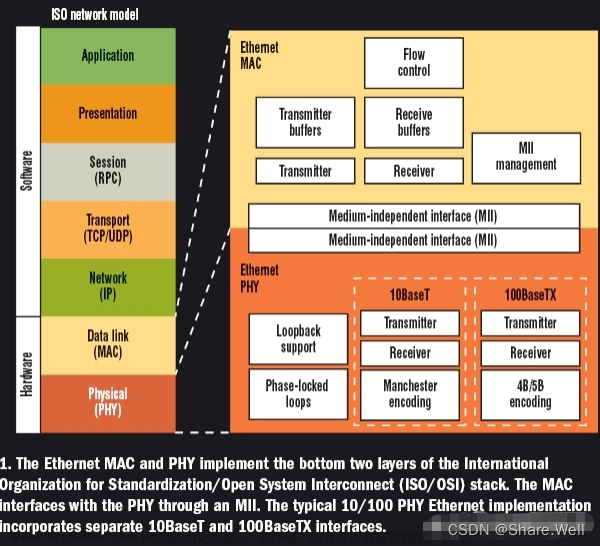

关于这个问题,也是请教朋友的过程中,意外学习到,一般来说以太网的时钟信号应该由控制芯片来提供,在这里也就是该由stm32h7芯片来提供时钟。但是我在手册上并没有看到输出时钟的方法(或许我看漏了吧)。所以在初始化流程并没有正常的进行。

而原理图的来源,是我们硬件工程师从一款海思的产品上copy下来的,所以他认为没什么问题。可能Soc芯片都有以太网时钟信号输出的能力吧。

所以不同的平台,驱动方式会略有差异,但问题终归是解决了。文章来源地址https://www.toymoban.com/news/detail-419152.html

到了这里,关于RTL8201 以太网PHY芯片 调试记录的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!