一、流水线设计介绍

在高速通信系统设计中,如何提高系统的工作速度至关重要,通常使用的方法有两种:

1. 并行方式设计:可减少模块间的延时;

2. 流水线设计:流水线设计如同生产线一样,将整个执行过程分解为若干个工作段,从流水线的起点连续输入,各操作段以重叠方式执行。使得运行的速度只与流水线输入的速度有关,而与处理所需的时间无关,从而提高运行效率。

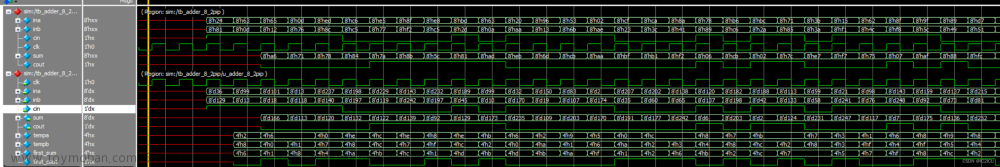

无流水线设计和有流水线设计示意图如下:

图1 无流水线设计

图2 有流水线设计

如果不采用流水线,输入的所有信号都要等前一个处理单元所有运算结束后才能进入处理模块;而采用了流水线设计后,输入信号只需经过一级流水处理后,就可以进入下一个流水线处理模块,数据处理时间减少了N倍。吞吐量也从T变为了NT,是面积换速度思想的具体体现。

流水线的基本结构是将适当划分的N个操作步骤串联起来。流水线操作的最大特点是数据流在各个步骤的处理,从时间上看是连续的,其操作的关键在于时序设计的合理安排,以及前后级接口间数据的匹配。

- 如果前级操作的时间等于后级操作的时间:直接输入即可;

- 如果前级操作的时间小于后级操作的时间:对前级数据进行缓存;

- 如果前级操作的时间大于后级操作的时间:串并转换等方法对数据进行分流处理后,再输入到后级模块。

图3 常用流水线设计时序示意图

二、流水线应用实例

接下来将介绍非流水线设计、二级流水线设计实例。

(1)非流水线实现方式文章来源:https://www.toymoban.com/news/detail-420637.html

module addr1(

input wire clk,

input wire [7:0] cina,

input wire [7:0] cinb,

output reg [7:0] sum,

output reg count);

always @(posedge clk) begin

{count,sum} <= cina + cinb + cin; //8位相加

end

endmodule(2) 二级流水线实现方式文章来源地址https://www.toymoban.com/news/detail-420637.html

module addr2(

input wire clk,

input wire cin,

input wire [7:0] cina,

input wire [7:0] cinb,

output reg [7:0] sum,

output reg count);

reg [7:0] sum1;

reg count1;

always @(posedge clk) begin

{count1,sum1} <= cina[3:0] + cinb[3:0] + cin; //低四位相加

end

always @(posedge clk) begin

{count,sum} <= {{cina[7],cina[7:4]} + {cinb[7],cinb[7:4] + cout1},sum1};

//高四位相加,并且将8位拼起来

end

endmodule到了这里,关于FPGA中的流水线设计(含Verilog范例)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!