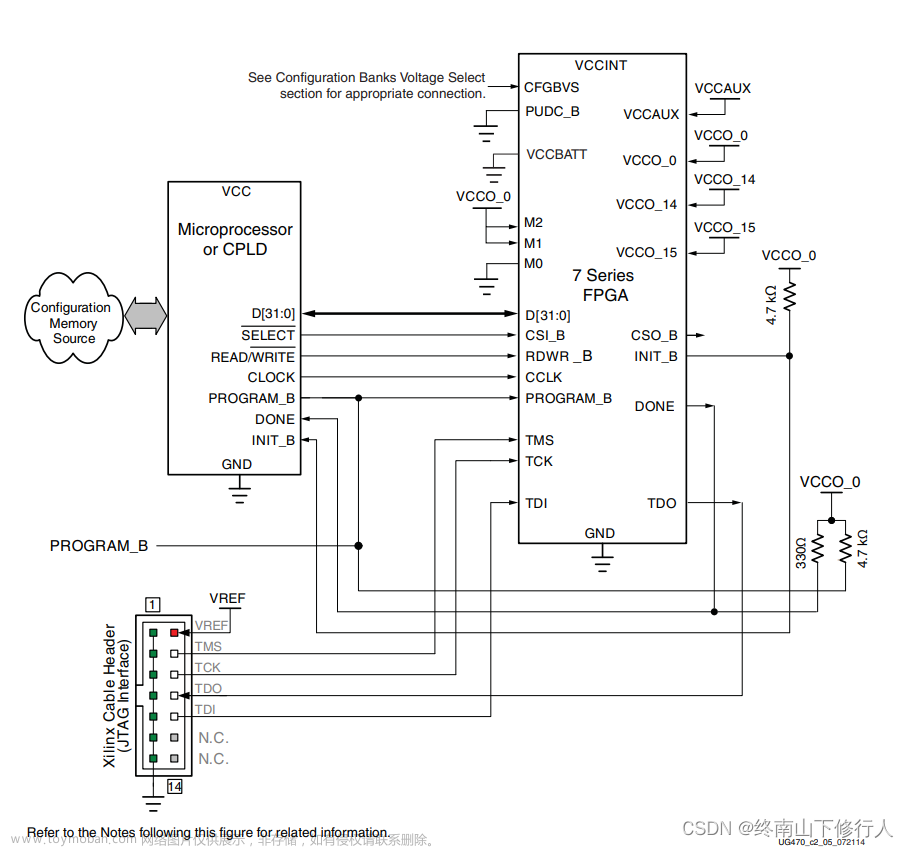

1.在配置过程中,7系芯片需要的电压有,Vcco0,Vccaux,Vccbram和Vccint。

所有的Jtag配置引脚在一个独立的专用bank上,使用的电源也是专用电源Vcco0。多功能pin在14和15bank。bank0,14和15上的专用输入输出引脚使用Vcco0,Vcco14,Vcco15的LVCMOS电平,电平需要匹配,输出引脚使用12mA,fast slew rate。

上电过程中,Vccint必须有1.0V或0.9V的供电。JTAG模式下,只有Vcco0需要供电,其他IO不需供电。

如果配置过程使用了bank14和15的引脚,则Vcco14和Vcco15必须有供电。

Vccbatt用于加密功能,如果不使用AES,Vccbatt接地即可。

Tpl,program延迟

Tpor,上电到INIT的时间

Ticck,cclk的输出延时

Tprogram,program的脉冲宽度

在上电期间,电压要保持单调,电平要达到手册中的推荐电压值,电压异常会导致配置数据丢失。

如果无法保证电压单调,可以外部拉低INIT_B来延迟配置,直到电压正常达到推荐值,如果配置过程涉及bank14和15,则Vcco14和Vcco15也要在INIT_B拉高前完成上电。

注:在上电或者program以后,INIT_B会内部拉低,表明FPGA正在清除内存,在采样模式引脚M之前,INIT_B是输入引脚,可以外部拉低,采样Mode以后,INIT_B变为OD输出,用来表征CRC和ID的error,如果为1表示有error,如果保持为0说明没有error,所以一旦INIT_B已经拉高,即便再次拉低也不能延迟配置。

设备上电后,可以拉低program_B来重新配置。

2.清除内存

一旦上电或者program拉低,马上清除配置空间。然后Block RAM回到初始态,触发GSR,FF回到初始态。触发GTS,IO变为高阻。INIT_B被拉低,Tpor后释放。如果外部拉低,则暂停配置,等到被释放后再继续配置,直到Tpor。

3.采样

拉高后,设备采样M,并发送CCLK,上升沿采样数据。对于BPI或并行模式,会进行位宽检测(初始为8),并刷新状态寄存器。

一次启动流程,模式只采样一次。

4.同步

如果是并行模式,或BPI,首先进行位宽检测。串行,SPI和JTAG不需要位宽检测。

然后接收同步字,告诉设备准备接收并对齐配置数据。

同步字之前的数据不会读取。

bit文件中会包含位宽模式和同步字。

5.检查ID

设备同步后,检查设备ID,检查指令包含在bit文件里,以防读取错误。如果ID错误,尝试重启。

6.加载配置数据,透明的

7.周期冗余检测CRC

如果错误,INIT_B拉低,设备放弃配置。

如果同步字读取丢失,会导致设备无法读取指令,也就不会进行CRC,也就不会拉低INIT_B,所以会出现DONE低,但是INIT_B为高的情况。

8.启动

bit文件指挥设备进入启动序列,启动序列由一个人8相状态机控制。用户可选的启动事件如下:

1.等待MMCM lock,可选。默认使用pll。

2.等待DCI match,可选。

3.默认触发GWE,可关。

4.默认反向GTS,激活IO,可关。

5.默认释放DONE,可关。

6.总是触发EOS,不可编程。

以上1到5可编程,6不可。

启动过程可以设置等待MMCM或DCI,此设置可以用来阻止DONE,GTS,GWE。

Done是OD门双向信号,设备释放后,使用内部上拉电阻使其拉高。

bank14和15的Vcco14和Vcco15如果低于1.8,则他们的IO有可能会经历一个010的逻辑转变,这个转变可能会干扰内部逻辑,因此Vcco14和15要设置为2.5V或3.3V。

对flash进行回读readback有2种方式。

回读检查。可以读出所有配置存储单元,包括LUT,Block RAM,SRL。

回读捕获。增强版。除了以上内容,还可以读所有CLB和IOB寄存器。

用户可以使用MCU,cpld或FPGA向设备发送指令,然后设备将配置存储器空间的内容回传给JTAG或SelectMAP,从而完成回读。文章来源:https://www.toymoban.com/news/detail-421003.html

回读以后,通过对比readback和configuration bitstream的方式进行错误判断。文章来源地址https://www.toymoban.com/news/detail-421003.html

到了这里,关于XILINX FPGA K7配置启动流程(官方手册整理)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!