作业5

题量: 21 满分: 100 作答时间:03-23 09:45至03-29 23:59 91.7分

一. 单选题(共11题,35分)

1. (单选题, 3分)计算机的存储器采用分级存储体系的主要目的是________。

- A. 便于读写数据

- B. 便于系统升级

- C. 解决存储容量、价格和存取速度之间的矛盾

- D. 减小机箱的体积

2. (单选题, 3分)存储器进行一次完整的读写操作所需的全部时间称为________。

- A. 机器周期

- B. 存取周期

- C. CPU周期

- D. 存取时间

3. (单选题, 3分)用户程序存放的主存空间属于________。

- A. 直接存取存储器

- B. 随机存取存储器

- C. 顺序存取存储器

- D. 只读存储器

我的答案: B:随机存取存储器;正确答案: B:随机存取存储器;

3分

4. (单选题, 3分)计算机系统中的存贮器系统是指________。

- A. 主存贮器

- B. cache、主存贮器和外存贮器

- C. RAM存贮器

- D. ROM存贮器

我的答案: B:cache、主存贮器和外存贮器;正确答案: B:cache、主存贮器和外存贮器;

3分

5. (单选题, 3分)某SRAM芯片,其存储容量为64K×16位,该芯片的地址线和数据线数目为________

- A. 64,8

- B. 64,16

- C. 16,16

- D. 16,64

我的答案: C:16,16;正确答案: C:16,16;

3分

6. (单选题, 3分)某计算机字长32位,其存储容量为4GB,若按双字编址,它的寻址范围是________ 。

- A. 8G

- B. 2G

- C. 4G

- D. 0.5G

我的答案: D:0.5G;正确答案: D:0.5G;

3分

答案解析:

4GB

字长32位,双字编址,一个地址存放字节数 32*2/8=8

共有地址数 4G/8=0.5G

7. (单选题, 3分)下列说法正确的是________ 。

- A. 半导体RAM是易失性RAM,而静态RAM中的信息不易失

- B. 半导体RAM是易失性RAM,而静态RAM只有在不掉电时信息才不丢失

- C. 半导体RAM信息是可读写的,且断电后能够保持

- D. 三者均错误

我的答案: B:半导体RAM是易失性RAM,而静态RAM只有在不掉电时信息才不丢失;正确答案: B:半导体RAM是易失性RAM,而静态RAM只有在不掉电时信息才不丢失;

3分

8. (单选题, 3分)存储单元是指( )。

- A. 存放 1 个二进制信息位的存储元

- B. 存放 1 个机器字的所有存储元集合

- C. 存放 1 个字节的所有存储元集合

- D. 存放 2 个字节的所有存储元集合

我的答案: B:存放 1 个机器字的所有存储元集合;正确答案: B:存放 1 个机器字的所有存储元集合;

3分

9. (单选题, 3分)某 DRAM 芯片,其存储容量为 512×8 位,该芯片的地址线和数据线的数目是( )。

- A. 8,512

- B. 512,8

- C. 18,8

- D. 9,8

我的答案: C:18,8;正确答案: D:9,8;

0分

10. (单选题, 3分)某机字长 32 位,存储容量 1MB,若按字编址,它的寻址范围是( )。

- A. 0-1M

- B. 0-512K

- C. 0-56K

- D. 0-256K

我的答案: D:0-256K;正确答案: D:0-256K;

3分

11. (单选题, 5分)某SRAM芯片,其容量为512×8位,除电源端和接地端外,该芯片引出线的最小数目应为______。

- A. 23

- B. 25

- C. 50

- D. 19

我的答案: D:19;正确答案: D:19;

5分

答案解析:

某SRAM芯片,其容量为512×8位,

数据线8,地址线 9

至少还包含2条:选片信号、读写信号的连接线。

二. 填空题(共10题,65分)

12. (填空题, 4分)SRAM靠____存储信息。DRAM靠____存储信息。

我的答案:

2分

(1) 触发器

(2) 电容

正确答案:

(1) 双稳态触发器

(2) 电容

13. (填空题, 4分)若RAM芯片内有1024个单元,用单译码方式,地址译码器有____条输入线,地址译码器有____条输出线。

我的答案:

4分

(1) 10

(2) 1024

正确答案:

(1) 10

(2) 1024

14. (填空题, 4分)若RAM芯片内有1024个单元,用双译码方式,地址译码器有____条输入线, 地址译码器有____条输出线。

我的答案:

4分

(1) 10

(2) 64

正确答案:

(1) 10

(2) 64

答案解析:

1024=2^10 共需10条地址线,

5条输入行译码器,5条输入列译码器

行、列译码器各输出2^5=32条输出线

32+32=64

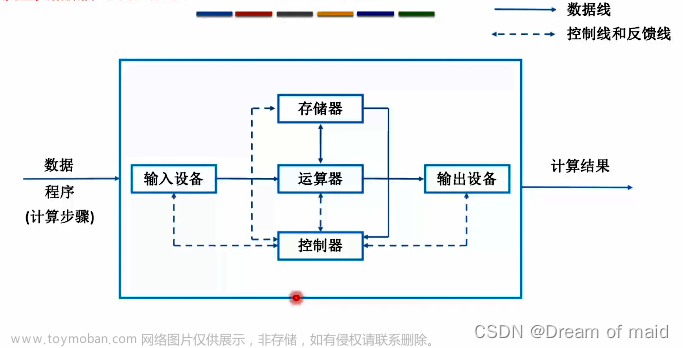

15. (填空题, 4分)

对存储器的要求是容量大、速度快、成本低,为了解决这三方面的矛盾,计算机采用多级存储体系结构。

三级存储系统包含____、____、____。(为方便比对,简写)

我的答案:

4分

(1) cache

(2) 主存

(3) 外存

正确答案:

(1) cache

(2) 主存

(3) 外存

16. (填空题, 4分)当一个存储字的字长高于8位时,就存在一个存储字内部的多字节的排列顺序问题,其排列方式称为端模式。______(大端/小端)模式是将一个字的低有效字节放在内存的低地址端,高有效字节放在内存的高地址端。

我的答案:

4分

(1) 小端

正确答案:

(1) 小端

17. (填空题, 5分)设有一个具有20位地址和32位字长的存储器,它能存储____(nKB/MB/GB)的信息。 采用字存储方式,CPU中地址寄存器的宽度为____,数据寄存器的宽度为____。 如果存储器由512K×8位 SRAM芯片组成,需要____片,组织方式为____片1组,共____组,需要____位地址作芯片选择。 为方便比对,请输入阿拉伯数字。

我的答案:

5分

(1) 4MB

(2) 20

(3) 32

(4) 8

(5) 4

(6) 2

(7) 1

18. (填空题, 5分)若一个16M×64位的内存条,用4MX8位的DRAM芯片组成,需要____片,组织方式,____片1组,共____组。 若某64位机主存采用半导体存储器,其地址码为26位,使用上述的内存条,最多可以插____条。若采用顺序存储方式,各内存条共用地址线为____条,A____~A0,完成内存条内存储单元寻址。A25~A____通过2-4译码器完成对各内存条的选择。

我的答案:

5分

(1) 32

(2) 8

(3) 4

(4) 4

(5) 24

(6) 23

(7) 24

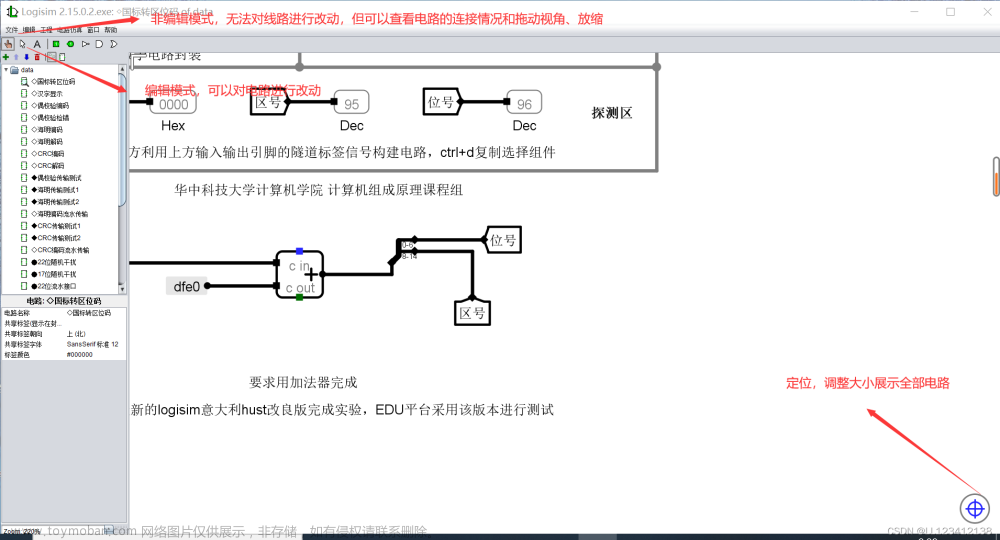

19. (填空题, 10分)用16K×8位的 DRAM 芯片构成64K×32位存储器, 请对该存储器的组成逻辑框图加以补充。 芯片扩展: 位扩展4片1组,字扩展共4组, 单片芯片大小为____(nKxm)(为方便比对,乘写成字母x即可)。 (为方便比对,最低位为第0位,高位在前,中间用英文波浪线) 地址线 高位地址线____(格式如:Am~An)通过2-4译码器选择第几组。 低位地址线____共用,进行片内地址的选择。 数据线 数据线32位:____(格式如:Dm~Dn),通过分支流入组内的4个芯片, 最高8位为____,最低8位为____。

我的答案:

正确答案:

(1) 16Kx8

(2) A15~A14

(3) A13~A0

(4) D31~D0

(5) D31~D24

(6) D7~D0

答案解析:

20. (填空题, 10分)要求用256K×16位 SRAM 芯片设计 1024K×32位的存储器。 SRAM 芯片有两个控制端:当CS有效时,该片选中。当W#/R=1时执行读操作,当W#/R=0时执行写操作。 请对该存储器的组成逻辑框图加以补充。 芯片扩展: 位扩展2片1组,字扩展共4组, 单片芯片大小为____(nKxm)(为方便比对,乘写成字母x即可)。 (为方便比对,最低位为第0位,高位在前,中间用英文波浪线) 地址线 高位地址线____(格式如:Am~An)通过2-4译码器选择第几组。 低位地址线____共用,进行片内地址的选择。 数据线 数据线32位:____(格式如:Dm~Dn),通过分支流入组内的不同的芯片, 高位为____,低位为____。

正确答案:

(1) 256Kx16

(2) A19~A18

(3) A17~A0

(4) D31~D0

(5) D31~D16

(6) D15~D0

答案解析:

21. (填空题, 15分)

某机器中,存储器由ROM和RAM芯片组成。

ROM区域的地址空间为 0000H~3FFFH 的 ROM区域。

RAM区域的起始地址为6000H,区域大小40K×16位,由8K×8的RAM芯片构成。

假设 CPU的地址总线为A15~A0,数据总线为D15~D0,绘制该存储器的组成逻辑框图。

控制信号为R/W(读/写), MREQ(访存),RAM 芯片有 CS 和 WE 信号控制端略。

请对解题步骤加以补充

解题步骤:

1)将ROM区域的地址0000H~3FFFH写成2进制形式

0000H即 0000000000000000B

3FFFH 即 ____B (16位2进制数)

访问这个区域需要____条地址线,区域大小为____K

2)RAM区域40K×16位,共需____片8K×8RAM芯片,____片1组,共5组。

8K芯片的地址 0~8K-1,

因此各组RAM芯片的地址区间:起始地址~起始地址+8K-1

8K-1 对应 1 1111 1111 1111B(13个1)

3)40K的RAM区域,地址分布从6000H开始,5个8K区域的地址为

6000H~6000H+8K-1、6000H+8K~6000H+8K+8K-1、………………………………

即 0110 0000 0000 0000B~ 0111 1111 1111 1111 (8K=2^13)

1000 0000 0000 0000B~1001 1111 1111 1111

1010 0000 0000 0000B~1011 1111 1111 1111

1100 0000 0000 0000B~1101 1111 1111 1111

1110 0000 0000 0000B~1111 1111 1111 1111

4)芯片容量位8K,因此地址线低13位均为片内地址,

共16条地址线,高3位地址线用来进行芯片选择。

5个区域的高3位地址线分别为____、____、101、110、111

5)用A15~A13作为选片信号, 经过3-8译码器选择RAM芯片。

ROM区域的高3位地址位____、____,因此3-8译码器输出为0、1时均选择ROM区域。

因为3-8译码器输出为低电平有效,选片信号也为低电平有效,

即3-8译码器0或1输出任何一个为低电平时选择ROM区域,因此如图示,用了____(与/或)门连接后作为ROM的选片信号。

正确答案:

(1) 0011111111111111

(2) 14

(3) 16

(4) 10

(5) 2

(6) 011

(7) 100

(8) 000

(9) 001文章来源:https://www.toymoban.com/news/detail-422233.html

(10) 与文章来源地址https://www.toymoban.com/news/detail-422233.html

到了这里,关于计算机组成原理 作业5的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!