1. 首先,不同型号的FPGA对外部QSPI Flash支持的最高频率是不一样的。XC6SLX45支持的最高频率仅为26MHz, 而XC7K325T支持的最高频率高达66MHz。

所以,当我们添加 set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design] 的时候,需要留意flash芯片支持的最高读命令频率, 这个在芯片的手册中可以查看到:

上图可以看出,Micron公司的N25Q064A支持的最高频率为108MHz,但支持的读命令频率为54MHz,对于这个器件来说Configuration Rate不能选的高于54MHz。

Macronix公司的MX25L25645G支持的最高频率为133MHz,但支持的读命令频率为50MHz,对于这个器件来说Configuration Rate不能选的高于50MHz

Winbond公司的W25Q128BV支持的最高频率为104MHz,但支持的读命令频率为33MHz

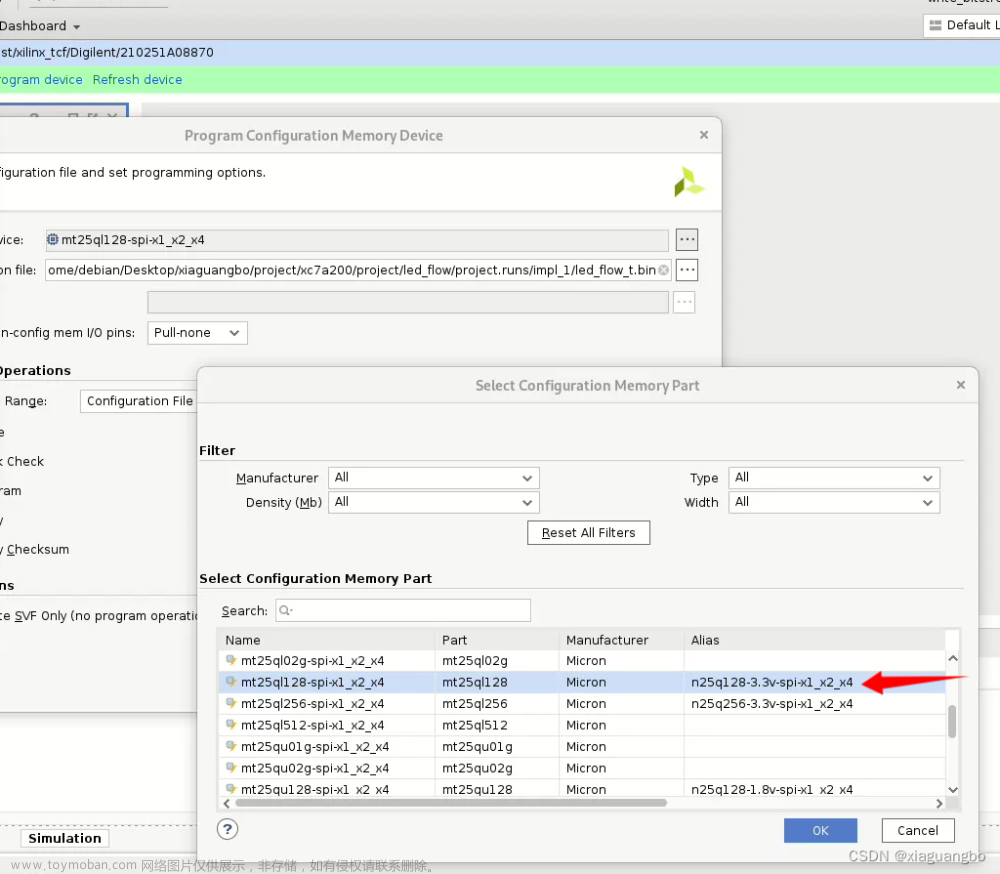

2. set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

Set SPI Configuration Bus Width可以设置为4的前提是你的开发板上QSPI Flash和FPGA之间四根数据线都是连通的。有的开发板只能用2,即x2.

3. set_property BITSTREAM.GENERAL.COMPRESS true [current_design]

压缩bit文件可以加快加载速度。文章来源:https://www.toymoban.com/news/detail-422673.html

最后, 编译后生成的文件大小与FPGA的型号有关, 与代码的多少并没有多大关系。 即在同一个FPGA芯片中,你写一个流水灯的代码 和 写一个添加有microblaze, dma, gpio, uart等IP核的代码,生成的文件大小并不会相差多少。文章来源地址https://www.toymoban.com/news/detail-422673.html

到了这里,关于Xilinx FPGA下如何加快QSPI Flash加载速度的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!