一、半加器和全加器简介

1.1 半加器

1、半加器是指对输入的两个一位二进制数相加,输出一个半加结果位和半加进位的组合电路,是没有进位的输入加法器电路,是一个实现一位二进制数的加法电路。

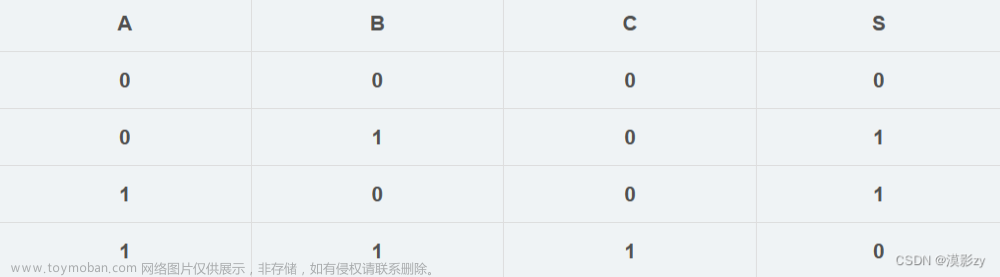

2、半加器的真值表如下;

S位结果位,C为进位

3、由真值表可以推出半加器的逻辑表达式为:

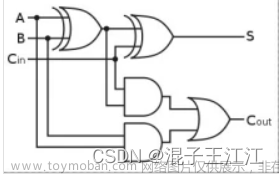

4、半加器逻辑电路图

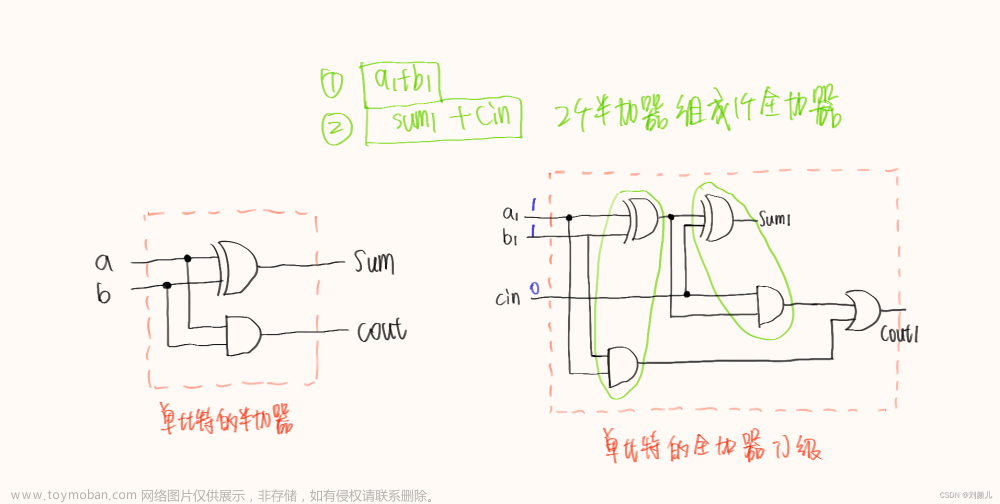

1.2 一位全加器

1、若两个多位数相加,除了要考虑对应位的数相加外,还必须考虑与低一位的进位数相加。因此,两个多位数相加时,每位加法器需要有三个输入端和两个输出端,这种加法器称为全加器。

2、 一位全加器的真值表:

3、一位全加器的逻辑电路图

二、原理图实现半加器与全加器

2.1 半加器

2.1.1 创建项目

按照下图所示顺序启动Quartus Ⅱ并完成项目:

设置文件路径顶层文件名后基本一路next

选择相应的芯片与器件库,博主所用器件库为cyclone Ⅳ E,芯片为EP4CE115F29C7

最后点击finish

2.1.2 原理图设计半加器

点击左上角File——New

选择Block Diagram/Schematic File

双击空白处,弹出器件选择窗口,输入and2 xor选择与门和异或门,并添加输入输出(input、output),同时可以通过双击器件,对器件进行命名,最终结果如下图所示:

保存文件,并编译

编译通过后可通过下图所示操作查看电路图

半加器数字逻辑电路图如下:

2.1.3 半加器波形仿真

按照下图所示进行操作:

File——New

(或者双击左方空白处)

而后对插入的输入信号进行波形编辑,赋予真值

选择信号波形时,长按鼠标左键选中波形上方空白处即可,如下图所示(若选到横线则会同时选中上下两段信号)

选中后通过点击工具栏的高低电平进行设置

点击下图按钮进行仿真

仿真结果如下:

如果出现报错,可查看博主过往博客,进行仿真器设置,或查看文章末尾的参考博客。

运行结果符合半加器真值表

2.1.4 将半加器设置为可调用元件

为了方便构建全加器,可先将半加器设置为可调用的元件

2.2 全加器

2.2.1 新建原理图

基本步骤同半加器(若要调用上文设计的半加器元件,需要将全加器与半加器文件设置为同一路径),设计结果如下:

2.2.2 Verilog语言设计全加器

新建verilog文件,输入以下代码:

module fulladder(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

注意,顶层文件名需要同module模块名一致,否则将编译失败!

进行编译:

无报错

查看电路逻辑图(同半加器):

进行波形时序仿真(同半加器):

三、上板测试

3.1 全加器

点击此按钮,进行引脚的绑定(或者点击工具栏Assignments——PIN Planner):

由于博主所有的板子为DE2-115,芯片为EP4CE115F29C7,该板引脚图如下所示:

博主的引脚设置如下:

设置完成后需要再进行一次编译,才可绑定完成上板!

第一次连接开发板后会提醒下载相关驱动,如果没有提醒,参考此博文

驱动设置完成后点击如下按钮:

然后如下图进行选择,Hardware选择USB-Blaster(博主实验已经完成,未连接板子所以下图无显示驱动),点击Start后待右上角Progress显示100%即证明烧录成功!

运行效果如下:

开关上拨为置1,LED亮为1

3.2 拓展:四位全加器

代码如下:

module fulladder4(cout,sum,a,b,cin);

output[3:0] sum;

output cout;

input[3:0] a,b;

input cin;

assign {cout,sum}=a+b+cin;

endmodule

引脚绑定如下图:

运行结果如下:

四、总结

本次实验复习了Verilog语言的一些基本语法与QuartusⅡ的一些基础设计、调试功能。设计并实现了半加器,全加器,四位全加器,使我对他们的电路结构有了进一步的理解。文章来源:https://www.toymoban.com/news/detail-424346.html

五、参考资料

https://blog.csdn.net/weixin_56102526/article/details/123536389

https://blog.csdn.net/qq_43279579/article/details/115480406

https://blog.csdn.net/lvzhshengh/article/details/115918262文章来源地址https://www.toymoban.com/news/detail-424346.html

到了这里,关于FPGA入门:QuartusⅡ实现半加器,全加器,四位全加器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!