0 🌈实验目的

(1)掌握数据选择器和译码器的功能。

(2)用数据选择器实验逻辑函数。

(3)用译码器实现逻辑函数。

1 🌈实验仪器及材料

2 🌈实验原理

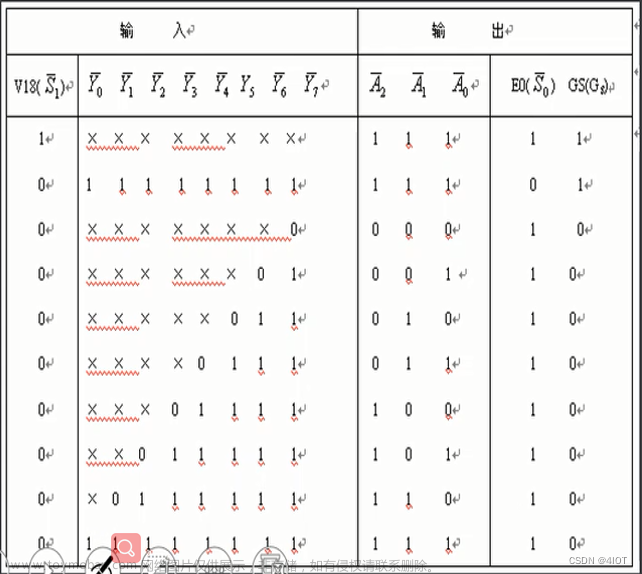

(一)74LS151

74LS151是常用的8选1数据选择器,芯片内部有一个8选1数据选择器。通过输入不同的地址码C、B、A,可以控制输出Y选择8个输入数据D0~D7中的一个。

连线图和逻辑功能表如下图所示。

S为使能端;

C、B、A为地址输入端;

D0~D7为8选1数据选择器的数据输入端;

Y为输出端。

74LS151输出的逻辑式可以写成:

(二)74LS153

74LS153简介

74LS153是常用的双4选1数据选择器,芯片内部含有两个地址码共用的4选1数据选择器。通过输入不同的地址码B、A,可以控制输出Y选择4个输入数据C0~C3中的一个。

连线图和逻辑功能表如下图所示。

1G、2G为两个独立的使能端;

B、A为公用的地址输入端;

1C0~1C3和2C0~2C3分别为两个4选1数据选择器的数据输入端;

Y1、Y2为两个输出端。

74LS153输出的逻辑式可以写成:

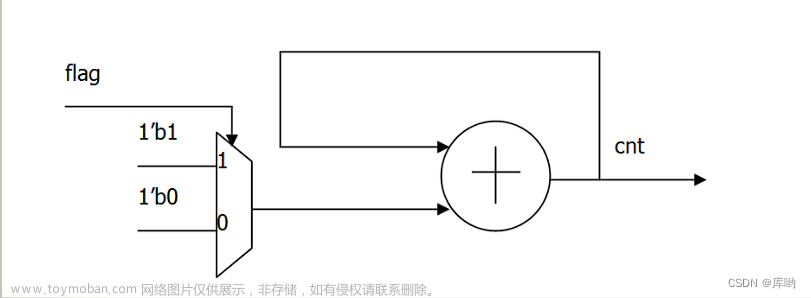

若将B、C作为两个输入变量,同时令C0~C3为第三个输入变量的适当状态(包括原变量、反变量、0和1),就可以在数据选择器的输出端产生任何形式的三变量组合逻辑函数。

同理,使用具有n位地址输入的数据选择器,可以产生任何形式输入变量数不大于n+1的组合逻辑函数。

3 🌈实验内容及步骤

按下表的要求设计一个逻辑电路

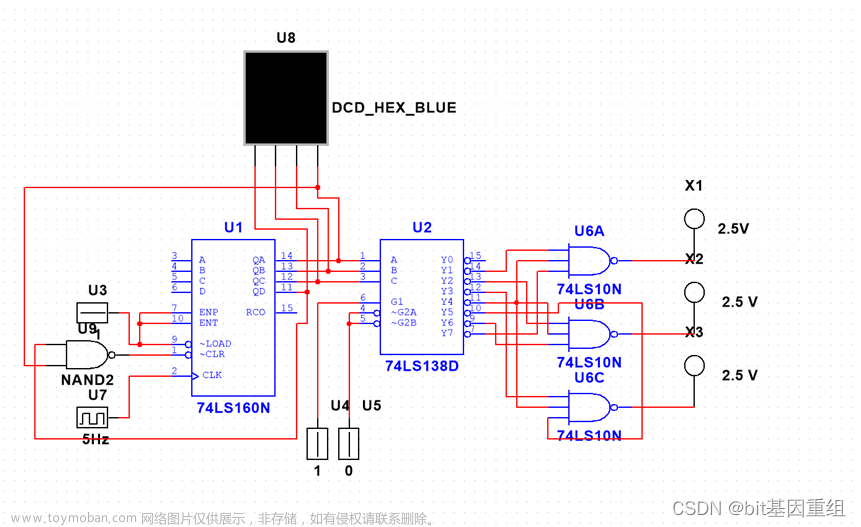

(1)写出逻辑表达式的变换,F=A'BD+AB'CD+BC'D+ABCD'

(2)将F表达式与74LS151输出Y的表达式比较,得到74LS151输入信号的表达式:

C=A D0=0

B=B D1=0

A=C D2=D

D3=D

D4=0

D5=D

D6=D

D7=D'

(3)画出电路图文章来源:https://www.toymoban.com/news/detail-426183.html

(4)功能测试(实测结果)文章来源地址https://www.toymoban.com/news/detail-426183.html

4🌈实验报告以及实验电路图等下载链接

数字逻辑实验:内含实验报告,和所用实验软件,还有实验电路图,其中包括七个实验实验报告中的各个实验的答案都已填好!!!-C++文档类资源-CSDN文库

到了这里,关于组合逻辑电路二——数字逻辑实验的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!