【LabVIEW FPGA图形化】 ngc、edf网表文件的编写:LED流水灯

前言

FPGA图形化可以提高FPGA的开发效率,为产品迭代、功能机验证,产品参数调试提供的便捷的编程方式。LabVIEW作为一款图形化开发软件可以为FPGA提供零代码开发,图形化界面可以非常直观的展示出FPGA的并行结构。LabVIEW的开发思路是顶层调用,其自身有丰富的函数和滤波器,同时支持在线前面板调试,对于PID调参等工业实践具有很大的帮助。但FPGA图形化编程的过程中,如果仅仅利用LabVIEW自身的资源,脱离底层Verliog就会缺乏灵活性,例如需要对新的传感器进行开发时,没有可以依赖的IP集成节点或Socket,程序框图就会比较复杂,FPGA图形化开发既要具有图形化编程的简洁性,又需要Verliog语言的灵活性,两者相辅相成使得LabVIEW FPGA大大节约了工程师的时间。

一、什么是FPGA图形化设计

随着FPGA的发展,国内外在数字电路相关的课程学习中都开始学习HDL(硬件描述语言)进行电路的设计,但是在HDL语言上由于它是用来描述底层的硬件,底层的语言学习过程花费的学习成本相对较高,例如VHDL,这种语言并不直观,而这会大大增加硬件设计的门槛。

因此,FPGA图形化设计为降低编程学习的门槛提供了新的思路,利用LabVIEW图形化程序编译平台,以框图的形式编写程序,通过LabVIEW开发环境设计、编译程序后下载至微处理器或FPGA芯片,最终达到独立运行的功能。

二、为什么要学习FPGA图形化开发?

FPGA图形化开发对于刚入坑的FPGA的小白来说比较友好,以图形化的界面呈现出了FPGA设计中的要素,而传统Verilog界面面向代码,语言描述硬件较为抽象,同时在LabVIEW中,它的时钟、FIFO、IO、LED、与或非门、条件结构、循环结构、顺序结构等都是以图形化的方式呈现,理解代码逻辑能有一个直观的印象。

FPGA有两条蔡氏定律:

1、FPGA不仅仅是FPGA。

2、FPGA的最终目的是做出可用的电路。

在产品级的FPGA开发上,应用工程师不关心FPGA内核是用什么语言去开发,更希望产品功能可以尽快实现,因此FPGA工程师不能仅仅专注于FPGA本身,更要去关注FPGA的硬件电路,不关注硬件电路的FPGA在实现功能上是有欠缺的,就比如USB通信,在STM32上由于集成的硬件的USB控制器,在驱动USB相对简单,但是对于FPGA来说就是一张白纸,如果从协议开始写会大大的提高FPGA的开发难度,于是采用USB芯片,FPGA只需要处理数据就行了,对于不同的芯片,控制方法不尽相同,但最终的目的都是一样的——做出可用的电路,实现产品功能。

两个界面的代码给人的感觉是不一样的。

三、Xilinx Spartan-6 系列网表文件封装的注意事项

由于Spartan6系列属于旧版本,不被新的编程软件Vivado支持,只能用ise进行下载编程,而ISE14.7生成网表文件格式为ngc,Vivado软件生成的网表文件为edf,在ISE环境下调用edf文件会提示black box,认为edf文件不被Spartan6支持,但是若使用LabVIEW封装成IP集成节点,可以跳过这个警告,从而可以在Spartan6系列中调用edf文件。

edf—>ISE14.7–×—>Spartan6 不支持

edf—>LabVIEW---->Spartan6 支持

要是现有edf文件运行很稳定,可以考虑用LabVIEW封装成IP集成节点进行调用。

四、传统HDL语言流水灯逻辑

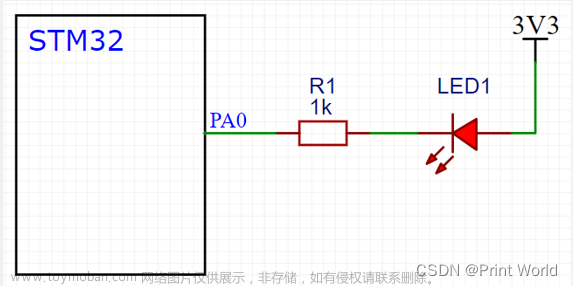

我们希望实现功能是实现任意时间间隔的LED灯流水,因此我们的输入接口留出了Count,在输出接口留4位的LED变量,以实现流水功能。

它的代码实现

module flow_led(

input clk,

input reset,

input wire [31:0] Count,

output reg [3:0] led

);

reg [31:0] counter;

reg [1:0] State;

always@(posedge clk or posedge reset) begin

if(reset)

counter<=24'd0;

else if(counter<Count)

counter<=counter+1'b1;

else

counter<=24'd0;

end

always@(posedge clk or posedge reset) begin

if(reset)

State<=2'b00;

else if(counter==Count)

State<=State+1'b1;

else

State<=State;

end

always @(posedge clk or posedge reset)begin

if(reset)

led[3:0]<=4'b0001;

else if(State==2'b00)

led[3:0]<=4'b0001;

else if(State==2'b01)

led[3:0]<=4'b0010;

else if(State==2'b10)

led[3:0]<=4'b0100;

else

led[3:0]<=4'b1000;

end

endmodule

注意,传统HDL语言编写好逻辑后,需要在综合设置中取消插入IO buffer,否则在调用的时候编译不通过。

设置好后综合,检查语法,并导出生成好的ngc文件,若读者采用Vivado可尝试同样方式生成网表,本文不再赘述。

五、Labview调用网表文件

-

新建FPGA工程,添加需要的vi和IO,将ngc网表复制到工程目录下

-

将ngc网表复制到工程目录下

-

-

在程序框图中添加IP集成节点,添加网表文件,将仿真行为设置成综合后模型,生成支持文件,并调整好接线端。

-

添加好节点后编写好程序:

六、实验验证

经过编译后,下载至FPGA验证流水灯时序,在在线前面板可以观察到LED灯不断地进行流水。 文章来源:https://www.toymoban.com/news/detail-426861.html

文章来源:https://www.toymoban.com/news/detail-426861.html

总结

通过以上网表文件,我们实现了Verliog语言与FPGA图形化的交互,打通了底层硬件语言在高级语言中调用的困难,对FPGA图形化编程的推广大有裨益。以上的代码资源和LabVIEW程序均开源在我的创作中心,欢迎下载交流。文章来源地址https://www.toymoban.com/news/detail-426861.html

到了这里,关于【LabVIEW FPGA图形化】 ngc、edf网表文件的编写:LED流水灯的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!