我们平时在PCB布线的时候,对于比较重要的信号都要做特殊处理,比如包地或者时“3W”,所谓3w指的是线与线之间的间距要满足三倍的线宽,那么我们怎么理解这个3W原则呢,他是如何降低信号之间的串扰的呢?

我们要了解这个原因可以先了解电容的概念,电容的组成无非就是两个导体组成的,而且这两个导体要处于不连接的状态,两个导体之间的是绝缘体,这个绝缘体也可以是空气。

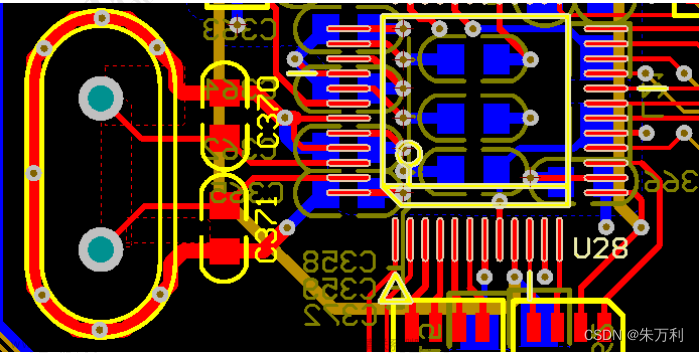

那我们可以看一下我们上图所示的场景,其实导线与导线之间就和我们的电容的概念一样,所以我们的导线是存在寄生电容的。

那么我们假设我们上图的data信号他是在传输的过程当中,那么由于有寄生电容的存在他有一部分信号就会串扰到上面那根时钟线上面去,那么由于我们的时钟线是比较重要的,和他相邻的导线会把一部分信号传到时钟线上面,那么这个时候我们这个时钟线重要信号就很有可能出现误判等情况,从而影响我们的板子的运行。

那这个时候我们要减小这个串扰我们可以根据容抗公式R=1/2π*F*C来计算,我们希望时钟线所分到data信号的电压越小越好,那么按照分压原理,CLK与DATA信号之间的电阻越大,CLK与GND之间的电阻越小则可以实现时钟线所分到data信号的电压越小,根据容抗公式R=1/2π*F*C,我们可以减小C的大小,从而增大clk与data信号之间R的值,那么这个时候我们又可以根据电容公式c=εs/d,得出我需要减小c可以减小ε(导体的介电常数)或者减小s(导体的面积),以及增大导体间的距离来实现,一般来说我们改变不了导体的介电常数和导体的面积,但是我们可以通过增大导体之间的距离来减小c的大小从而达到降低串扰的目的。

那么在实际应用中应该要把这两根导线相隔多远呢,我们一般是采用3倍线宽的距离来降低信号的线间串扰,这就是我们平时设计当中的3w原则的原理。

当然,我们还有一种方法也可以减小线间串扰,那么就是这个重要信号两边都加上两根地线,那么这个时候地线两边的串扰信号通过我们的地线流走了,那么这个时候线与线之间的串扰就变小了,当然包地的时候,我们最好相隔一定的距离打上地空,那么这个时候他的效果就更好了!文章来源:https://www.toymoban.com/news/detail-427303.html

声明:本文凡亿教育原创文章,转载请注明来源!

文章来源地址https://www.toymoban.com/news/detail-427303.html

到了这里,关于如何理解PCB布线3W规则的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!