-

分时: 同一总线在同一时刻,只能有一个部件占领总线发送信息,其他部件要发送信息得在该

部件发送完释放总线后才能申请使用。

-

共享: 在总线上可以挂接多个部件,它们都可以使用这一信息通路来和其他部件传送信息。

一、实验目的

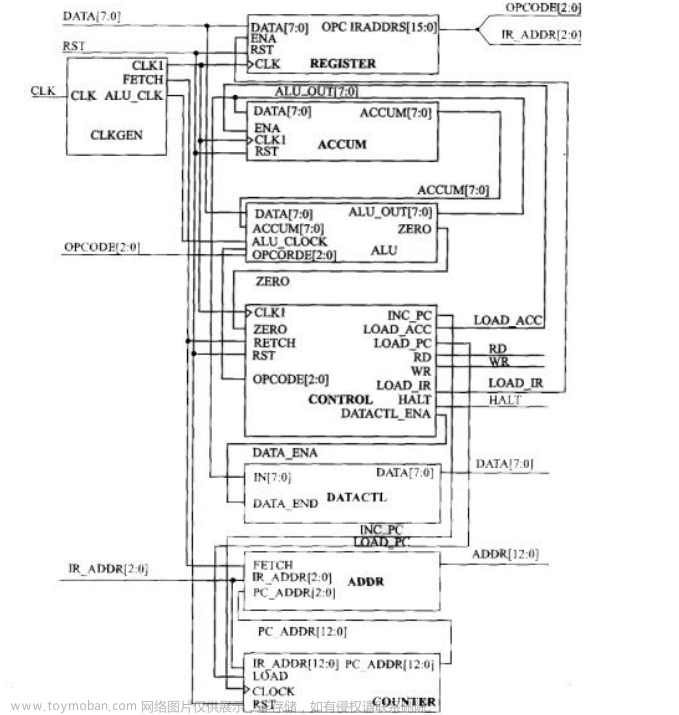

- 理解总线的概念及其特性。

- 掌握控制总线的功能和应用。

- 理解总线的功能和和典型工作流程。

- 掌握在总线上协调ALU和外设交换数据的方法。

文章来源地址https://www.toymoban.com/news/detail-427357.html

文章来源:https://www.toymoban.com/news/detail-427357.html

到了这里,关于计算机组成原理实验三-----系统总线和具有基本输入输出功能的总线接口实验的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!