一、DAC

权电阻DA

具体参考数字电路。我们输入数字量,这里以4位为例,比如D3-D0=1001,对应得到一个

,通过Rf,得到输出电压U0。

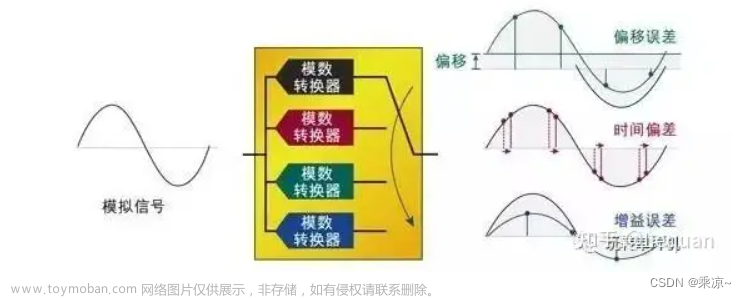

二、ADC

主要就是采样定理和编码。取样、保持、量化、编码。

量化后就可以进行编码然后输出数字信号了。比如输入模拟量是t1时刻的值,对应101.这个是一个8位精度的。当然一般我们还会带一个符号位。0正1负。

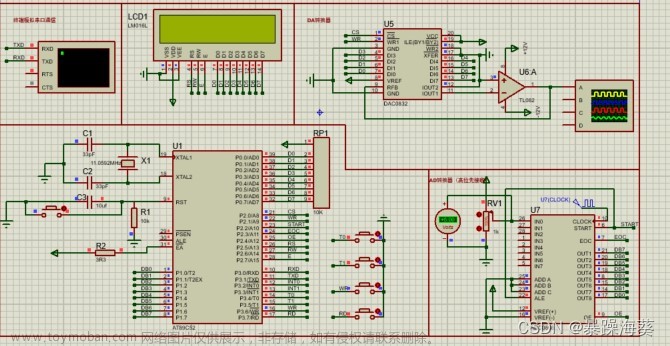

本实验我们使用的 AD-DA 模块是正点原子推出的一款高速模数-数模转换模块(ATK_HS_AD_DA),高速 AD 转换芯片和高速 DA 转换芯片都是由 ADI 公司生产的,分别是 AD9280 和 AD9708。学习ADDA芯片我们只需要知道它有哪些引脚怎么用就可以了。

三、实验任务

实验任务是使用领航者 ZYNQ 开发板及高速 AD-DA 扩展模块(ATK_HS_AD_DA 模块)实现数模 及模数的转换。首先 ZYNQ PL 产生正弦波变化的数字信号,经过 DA 芯片后转换成模拟信号,将 DA 的模 拟电压输出端连接至 AD 的模拟电压输入端,AD 芯片将模拟信号转换成数字信号,然后通过 ILA 观察数字 信号的波形是否按照正弦波波形变化。系统框图如下。

原理图如下:由ROM发送数字信号给发送模块,由DA转换芯片转换成模拟量,模拟量再由AD转换成数字量由接受模块接受带FPGA中,用ILA核去抓取信号。

接下来介绍FPGA内部模块的编写。

首先是send模块。这个模块就是发送地址给ROM然后将ROM读出数据再发送给DA模块。这里要注意的是,send模块还要给DA芯片提供一个时钟信号。这个时钟有这样的特点。

//数据rd_data是在clk的上升沿更新的,所以DA芯片在clk的下降沿锁存数据是稳定的时刻

//而DA实际上在da_clk的上升沿锁存数据,所以时钟取反,这样clk的下降沿相当于da_clk的上升沿

同时我们还要对读数据频率进行调节。有一下设计我们计数值越大,读数据速度越慢,但是就越稳定。找到稳定且高速的值。我们这里填5,就是,就是5*20=100ns一个数据。

module da_wave_send(

input clk , //时钟

input rst_n , //复位信号,低电平有效

input [7:0] rd_data, //ROM读出的数据

output reg [7:0] rd_addr, //读ROM地址

//DA芯片接口

output da_clk , //DA(AD9708)驱动时钟,最大支持125Mhz时钟

output [7:0] da_data //输出给DA的数据

);

//parameter

//频率调节控制

parameter FREQ_ADJ = 8'd5; //频率调节,FREQ_ADJ的越大,最终输出的频率越低,范围0~255

//reg define

reg [7:0] freq_cnt ; //频率调节计数器

//*****************************************************

//** main code

//*****************************************************

//数据rd_data是在clk的上升沿更新的,所以DA芯片在clk的下降沿锁存数据是稳定的时刻

//而DA实际上在da_clk的上升沿锁存数据,所以时钟取反,这样clk的下降沿相当于da_clk的上升沿

assign da_clk = ~clk;

assign da_data = rd_data; //将读到的ROM数据赋值给DA数据端口

//频率调节计数器

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

freq_cnt <= 8'd0;

else if(freq_cnt == FREQ_ADJ)

freq_cnt <= 8'd0;

else

freq_cnt <= freq_cnt + 8'd1;

end

//读ROM地址

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

rd_addr <= 8'd0;

else begin

if(freq_cnt == FREQ_ADJ) begin

rd_addr <= rd_addr + 8'd1;

end

end

end

endmodule接下来介绍recv模块。数字信号经过,DAC已经转换成模拟信号了,这里如果是再项目中,已经可以对一些东西进行处理比如对什么施加转换好的模拟电压。得到的值再由DAC转换成数字信号再进行分析。

这个实验只是为了使用ADDA,我们将模拟信号直接接到AD接口,进行转换得到数字信号由RECV接收。所以我们这个模块只需要输出一个驱动时钟就可以。我们本次实验的芯片的最大时钟频率是32MHZ我们对50mhz2分频。

module ad_wave_rec(

input clk , //时钟

input rst_n , //复位信号,低电平有效

input [7:0] ad_data , //AD输入数据

//模拟输入电压超出量程标志(本次试验未用到)

input ad_otr , //0:在量程范围 1:超出量程

output reg ad_clk //AD(TLC5510)驱动时钟,最大支持20Mhz时钟

);

//*****************************************************

//** main code

//*****************************************************

//时钟分频(2分频,时钟频率为25Mhz),产生AD时钟

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

ad_clk <= 1'b0;

else

ad_clk <= ~ad_clk;

end

endmodule值得注意的是两个模块对DA DA芯片提供的时钟不一样。

之后代AD转换后输入到FPGA中我们用ILA核去观察波形就可以了。还有AD模块还会输出一个ad_otr,这个如果是1,则表示我们超出量程了。当输入的模拟电压超出量程时,会拉高 OTR(out-of-range) 信号.

补充:(17条消息) FPGA学习专题-ADC的使用_南山维拉的博客-CSDN博客_fpga采集adc数据后如何处理

在一个系统中ADC和DAC的参考电压应该一致。

设计时,经过FPGA内部的时钟,可能会导致抖动好相位噪声不好。但是在资源有限的情况下可以用PLL生成时钟,不做太多处理。

ADC的超量程标志位非常重要,一旦超量程将对采样造成严重的影响。一旦有溢出一定要先处理输入信号。

对于无符号的DAC,有符号补码需要先把高位取反再送给DAC

有符号数转换为无符号数时,负数转换为大的正数,相当于在原值上加上2的n次方,而正数保持不变。文章来源:https://www.toymoban.com/news/detail-428006.html

文章来源地址https://www.toymoban.com/news/detail-428006.html

到了这里,关于9.8日fpga之DA/AD的学习的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!