1.1设计要求

理解和掌握 CPU 中的算术逻辑运算部件(ALU)和寄存器堆(Register File)的工作原理,并使用 Verilog 和 ModelSim 进行设计和仿真。

1. 使用 Verilog 完成 ALU 的设计,并编写测试仿真文件验证其正确性。要求:

ALU 支持 16 位的加、减、与、或以及移位运算。

2. 使用 Verilog 完成通用寄存器堆的设计,并编写测试仿真文件验证其正确性。要求:

寄存器堆包含 8 个 16 位的寄存器;

寄存器堆有两个读端口和一个写端口。

-

- 方案设计

(1)ALU方案设计

我们所要设计的ALU需要实现16位的加、减、乘、除、与非、或非、同或、异或、逻辑左移、算术左移、逻辑右移、算术右移的功能。

图 1.1 ALU算术逻辑单元图

图 1.2 ALU模块电路图

(2)寄存器堆方案设计

CPU内部通常包含若干个通用寄存器,以暂存参加运算的数据和中间结果。寄存器速度快,个数少,但是RISC CPU的设计强调设置大量的寄存器。例如,Intel 80x86系列CPU中只有8个寄存器,而SPARC RISC CPU中却有120个寄存器。MISP CPU中有32个32位的寄存器堆。

所谓寄存器堆,就是一个寄存器的集合,为方便访问其中的寄存器,对寄存器堆中的寄存器进行统一编码,称为寄存器号或者寄存器地址,每个寄存器均通过制定寄存器好进行访问。

图 1.3 寄存器堆模块电路图

-

-

- Verilog 关键代码实现

-

(1)ALU关键代码实现

图 1.4 ALU模块描述

ALU 模块的输入输出功能及特点描述如图1.4所示,该模块的verilog 代码如下所示:

(2)寄存器堆关键代码实现

图1.5 寄存器堆模块描述

寄存器堆模块的功能描述如表 1.2 所示,模块的verilog 代码如下:

-

-

- 测试文件(test)关键代码描述

-

- ALU测试代码

(2)寄存器堆测试代码

-

- 实验步骤

- 明确实验要求

1.1实验目的

理解和掌握 CPU 中的算术逻辑运算部件(ALU)和寄存器堆(Register File)的工作原理,并使用 Verilog 和 ModelSim 进行设计和仿真。

1.2实验内容

1.2.1 使用 Verilog 完成 ALU 的设计,并编写测试仿真文件验证其正确性。

要求:ALU 支持 16 位的加、减、与、或以及移位运算。

2. 使用 Verilog 完成通用寄存器堆的设计,并编写测试仿真文件验证其正确性。要求:寄存器堆包含 8 个 16 位的寄存器;寄存器堆有两个读端口和一个写端口。

- 设计实验方案

包括设计实验的功能表和电路图。

实验功能表见图1.4与1.5;

电路图如下:

图 1.6 ALU实验电路图

图1.7寄存器堆实验电路图

- 完成实验代码并调试和仿真

实验代码见1.2方案分析,调试见1.4故障与调试,仿真见1.5仿真及分析。

-

-

故障与调试

- 故障1

-

故障与调试

故障现象:

在ModelSim中成功调试,却仿真失败。

原因分析:

首先分析项目文件名称是否有中文;其次,可能是软件安装过程中有些环境没有配置好,需要检查配置的环境。

解决方案:

项目文件名需要替换为英文;卸载ModelSim,安装Vicado,检查配置环境,直至可以正常仿真。

-

-

- 故障2

-

故障现象:

运算结果无法写入。

原因分析:

Input_Data冲突的问题。

解决方案:

将运算结果F做为输出,定义一个ALU_F作为中间变量。ALU_F和Input_Data设计一个二选一控制电路,外加一个控制信号。

-

-

- 故障3

-

故障现象:

Vivado闪退,点击 RTL ANALYSIS 下面的Open Elaborated Design闪退。

原因分析:

电脑环境不兼容,或者文件运行中出现问题

解决方案:

点击项目文件夹的.xpr文件进入vivado而不是打开vivado再打开项目。

-

- 仿真及分析

仿真结果如以下:

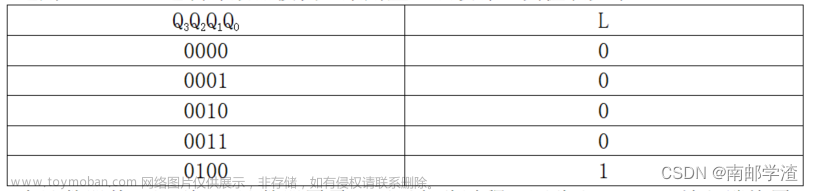

ALU仿真测试用例见表 1.3。

表 1.3 ALU仿真测试用例

寄存器堆仿真测试用例见表 1.4。

表 1.4 寄存器堆仿真测试用例

文章来源:https://www.toymoban.com/news/detail-428242.html

文章来源:https://www.toymoban.com/news/detail-428242.html

注:修改仿真文件后需要先进行保存,之后再进行测试仿真。 文章来源地址https://www.toymoban.com/news/detail-428242.html

到了这里,关于实验二 CPU 部件实现之 ALU 和寄存器堆的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!