如表1所示是dds_ip_transform模块信号列表,在正弦波模块中我们需要把上游指令解析模块中发来的频率控制字和指示信号即dds_din_freq和dds_din_freq_vld、相位控制字和指示信号即dds_din_phase和dds_din_phase_vld、复位信号即ddsip_sclr写入到DDS IP核中,如图1所示是正弦波模块的代码设计。

本模块中存在了比例系数的计算问题,在这里DDS IP核和前面Modelsim仿真的配置保持一致,同样的在程序设计中也有几个地方值得注意:

1. DDS IP核的输出信号包含了SIN、COS混合信号和其指示信号即m_axis_data_tdata和m_axis_data_tvalid;相位累加器数值和其指示信号即m_axis_phase_tdata和m_axis_phase_tvalid,这两对信号在程序设计中是非常重要的,可以在m_axis_data_tvalid有效时对m_axis_data_tdata进行数据拆分把SIN正弦波提取出来。正常情况下m_axis_phase_tdata在每个时钟周期都是累加递增的,若当前时钟下的m_axis_phase_tdata比上一个时钟下的m_axis_phase_tdata值小,则说明DDS IP核累加器刚跑完一圈,可以作为ddsip_done信号输出给上游模块作为读FIFO的rdy指示信号;

2. DDS IP核的输入信号s_axis_config_tdata在其指示信号s_axis_config_tvalid为高时有效,且信号s_axis_config_tdata的低32位是频率控制字,高32位是相位控制字,所以需要在dds_din_freq_vld和dds_din_phase_vld高有效时分别去赋值给s_axis_config_tdata对应的位;3. 关于频率控制字和相位控制字的计算在前面也详细介绍过,这里由上位机PC端进行计算,并将其结果通过不同接口发给FPGA开发板端,正弦波频率控制字是2^n*fout/fclk = 2^26/(500*10^3) = 134.217728,这个参数由上位机计算即用户输入Xhz的频率,则上位机下发设定正弦波频率控制字的数据码为134.217728*X,相位控制字是Y(0-360),则上位机下发设定正弦波相位控制字的数据码为2^26*Y/360。

| 信号列表 | ||

| 信号名 |

I/O |

位宽 |

| clk |

I |

1 |

| rst_n |

I |

1 |

| dds_din_freq |

I |

32 |

| dds_din_freq_vld |

I |

1 |

| dds_din_phase |

I |

32 |

| dds_din_phase_vld |

I |

1 |

| ddsip_sclr |

I |

1 |

| ddsip_done |

O |

1 |

| sin_out |

O |

8 |

表1 dds_ip_transform模块信号列表

图1 正弦波模块的代码设计

图1 正弦波模块的代码设计

如图2所示是任意波模块的设计示意图,在这个模块中我们要去完成给定频率方波、三角波、梯形波的波形输出,其实和正弦波模块在实施方式上大同小异,只是在这个模块中我们采用ROM查表法和状态机切换相结合的方法去巧妙实现。

大家在这里不妨静下心去想一想,常规的任意波形即方波、三角波、梯形波甚至锯齿波,说到底透过现象看本质完全可以把整个波形拆分成一段段的子波形,对于豌豆开发板板载的AD9708而言本身是8位DAC,故其数字变化的范围是0-255,那么我们完全可以把输出任意波的过程还原成“上升时间1“、”保持时间1“、”下降时间“、”保持时间2“、”上升时间2“五个状态。

在这里笔者使用Guagle_wave插件把一个三角波完整地裁剪成512个点,即DAC的输入值先从8‘h80涨到8’hff接着降到8’h0最后涨到8‘h80,笔者将其分为3段即图7-78中的“上升时间1“、”下降时间“、”上升时间2“,注意到下降时间是一段即每段对应了256个点,但是上升时间被分为两段即每段对应了128个点。

我们把这三段波形依次存到ROM表中即triangle_rom0、triangle_rom1、triangle_rom2,参考数字变频的相关技术,在这里只需要把两段上升沿、一段下降沿的频率控制字计算出来即可,在”保持时间1“内DAC输入值为8’hff,而在”保持时间2“内DAC输入值则为8’h0,那么只用调整好状态机的切换就可以实现三角波、方波、梯形波的任意频率输出。

上位机端要把保持时间、上升时间和下降时间都计算出来,再通过命令码“0x05”、“0x06”、“0x07”分别发送上升时间、下降时间、保持时间的频率控制字的数据码。

对于保持时间很容易理解,因为在整个模块中用到了500Khz的时钟作为DAC的时钟,即对应一个时钟周期是2us而上位机端均以ms计数,所以1ms就折合500个时钟周期,如果用户设置Xms的保持时间,则上位机下发设定任意波保持时间频率控制字的数据码为500*X。

对于上升时间和下降时间,为了提高精度统一选取了32位的相位累加器,上升时间可以看成是由256个点组成的完整三角波形(“上升时间1“对应DAC的输入值先从8‘h80涨到8’hff接着降到8’h80,“上升时间2“对应DAC的输入值先从8‘h80降到8’h0接着涨到8’h80),故和前面所介绍的计算公式相同,这里由上位机PC端进行计算,并将其结果通过不同接口发给FPGA开发板端,上升时间频率控制字是2^n*fout/fclk = 2^32/(500*10^3)=8589.934,故当用户输入Yms的上升时间,则上位机下发设定任意波上升时间频率控制字的数据码为8589.934*1000/Y。

而下降时间可以看成是由512个点组成的完整三角波形(“下降时间“对应DAC的输入值先从8‘h0涨到8’hff再降到8’h0),所以需要对其累加器步长乘二,下降时间频率控制字是8589.934*2=17179.868,故当用户输入Zms的下降时间,则上位机下发设定任意波下降时间频率控制字的数据码为17179.868*1000/Z。

图2 任意波模块的设计示意图

图2 任意波模块的设计示意图

如表2所示是任意波模块的信号列表,如图3所示是其对应的代码设计,在这个模块中,我们需要把指令解析模块中解析到的上升时间、保持时间、下降时间以及波形种类信息发向本模块,同样地在代码设计当中也存在几点值得注意:1. 对于三角波、方波、梯形波用了同样的状态机实现,只不过三角波不存在保持时间而方波不存在下降时间和上升时间,需要根据波形种类进行状态机的跳转以实现输出不同任意波的效果;2. 本模块同样的输出wave_done作为上游模块作为读FIFO的rdy指示信号,这样就可以保证跑满整个波形周期再改变波形种类和参数,有效预防本模块状态机由于参数错误跑飞;3. 对于上升时间和下降时间都用了32位的累加器,在状态到来时对其进行累加操作,再由32位累加器的最高位地址映射到ROM表,查表得到当前时刻对应的8位DAC输入值。

| 信号列表 | ||

| 信号名 |

I/O |

位宽 |

| clk |

I |

1 |

| rst_n |

I |

1 |

| wave_din |

I |

104 |

| wave_din_vld |

I |

1 |

| wave_done |

O |

1 |

| wave_out |

O |

8 |

表2 arbitrary_wave模块信号列表

图3 任意波模块的代码设计

图3 任意波模块的代码设计

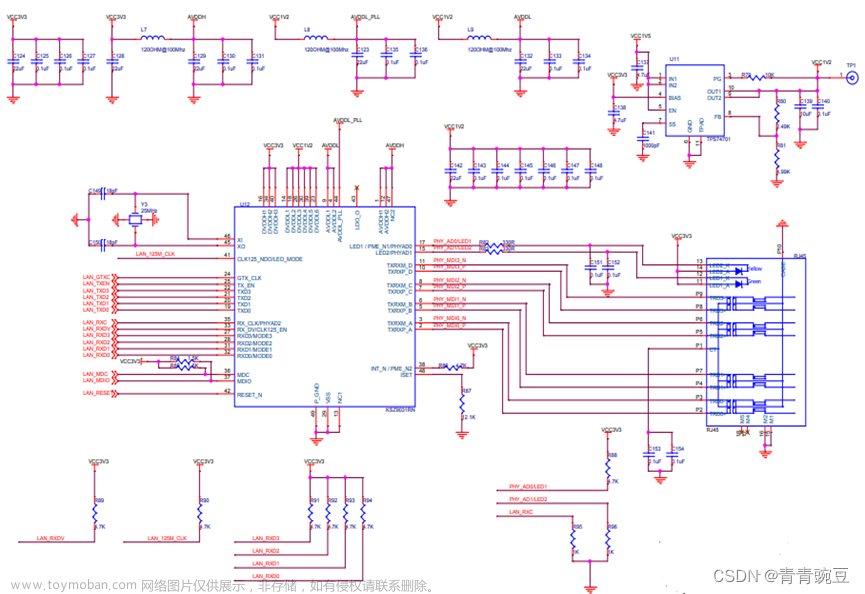

如图4所示是整个模块顶层文件的代码设计,在顶层模块中我们需要把USB2.0顶层模块、RS232串口顶层模块、ETH千兆网口顶层模块、指令解析模块、任意波发生模块、正弦波发生模块相关信号量都例化好。

这也是豌豆开发板“20个例程”篇的最后一个,选取在这里也是一个比较新颖的工程项目,笔者用Labview精心地搭建了一套PC端上位机测试软件,大家完全可以将其看成一个支持多种通信接口的程控波形发生器,在下位机FPGA端沿用了自顶向下的设计理念。

首先把三种接口即RS232、USB2.0、ETH做成独立的接口模块,其次也把指令解析模块单独拿了出来,对上接收各种接口发来的指令报文并回复,对下用FIFO缓存数据码并将其发送给任意波和正弦波模块,有效解决了数据跨时钟域和数据不同步问题,再次按照功能把波形发生模块划分为正弦波模块和任意波模块,两个模块独立工作同一时刻DAC只输出其中一个模块的输出波形或者选择关闭,最后整个例程也把信号处理和接口设计融入到一起,并引入了上位机搭建测试系统的理念。

当然“20个例程”篇并不是最后的结尾,在后期笔者也会基于这款豌豆Artix7开发板推出更多更接近实战项目的工程,包括和上位机端以及和ARM、MCU端等。

图4 USB2.0/RS232/ETH控制并行DAC输出任意频率

正弦波、梯形波、三角波、方波顶层模块的代码设计

笔者通过上位机波形助手依次输出如图5所示10ms保持时间的方波,如图6所示10ms上升时间、10ms下降时间的三角波,如图7所示10ms上升时间、10ms下降时间、10ms保持时间的梯形波,如图8所示10hz频率的正弦波。

这里豌豆开发板硬件上配置了10千欧的电位器调节DAC模拟输出范围,同时大家可以打开波形助手实际操作下,通过ILA IP核在线观察报文数据,以及各个模块的关键信号加深对整个项目工程的理解。

图5 输出10ms保持时间的方波

图5 输出10ms保持时间的方波

图6 输出10ms上升时间、10ms下降时间的三角波

图6 输出10ms上升时间、10ms下降时间的三角波

图7 输出10ms上升时间、10ms下降时间、10ms保持时间的梯形波

图7 输出10ms上升时间、10ms下降时间、10ms保持时间的梯形波

图8 输出10hz频率的正弦波文章来源:https://www.toymoban.com/news/detail-428951.html

图8 输出10hz频率的正弦波文章来源:https://www.toymoban.com/news/detail-428951.html

FPGA波形助手调试文章来源地址https://www.toymoban.com/news/detail-428951.html

到了这里,关于FPGA 20个例程篇:20.USB2.0/RS232/LAN控制并行DAC输出任意频率正弦波、梯形波、三角波、方波(五)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!