实验目的

用连续值 或者always语句实现3-8译码器74138

了解3-8译码器的功能,锻炼根据功能表实现硬件功能的能力

熟悉上板操作的步骤和流程

74138的器件手册中的Function Tables:

文章来源:https://www.toymoban.com/news/detail-431148.html

文章来源:https://www.toymoban.com/news/detail-431148.html

实验内容

(一)实验流程:

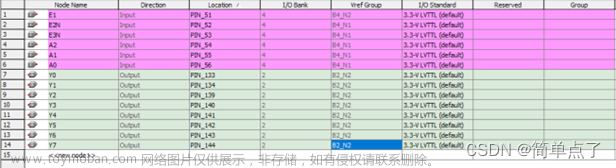

用verilog语言在vivado环境下编写源文件,实现3-8译码器。经综合、实现、生成bitstream文件后,将bit文件下载到NEXYS4 DDR开发板上测试功能(三个指定的拨动开关代表输入,上拨值为1,下拨值为0; 八个指定的led灯代表输出&#文章来源地址https://www.toymoban.com/news/detail-431148.html

到了这里,关于数字逻辑与部件设计基础实验——3-8译码器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!