概述

预分频器 (Prescaler) 是数字系统中用于降低时钟频率的关键组件. 本文小白我将介绍预分频器的工作原理, 应用场景和实现方法, 来帮助大家更好的理解和应用预分频器的技术.

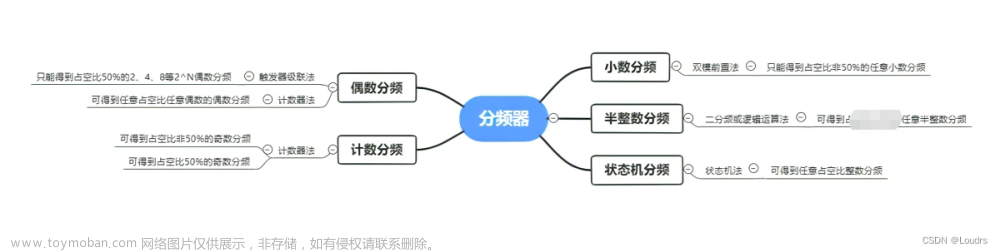

分频器是什么

分频器 (Prescaler) 是一种用于将输入时钟信号频率降低的电子设备. 通常, 预分频器可以将输入频率降低为整数倍, 小数倍或任意比例. 预分频器在数字系统中具有广泛应用, 例如微控制器, 通信系统, 计时器等.

工作原理

预分频器的工作原理主要依赖于计数器, 触发器, 模数计数器等电子元件. 通过这些元件, 预分频器可以将输入信号的周期按照特定的规律进行累积和清零, 从而实现频率降低的目的.

计数器预分频器

计数器预分频器是一种基于二进制计数器的预分频技术. 计数器对输入信号的上升沿或下降沿进行计数, 当计数值达到预设值时, 计数器清零并输出一个信号脉冲. 通过调整计数器的预设值, 可以实现不同的预分频比例.

触发器预分频器

触发器预分频器主要利用 D 触发器或 JK 触发器实现. D 触发器在输入信号的上升沿或下降沿时, 将数据输入端的状态传递到输出端. 通过将触发器的输出端与输入端相连, 可以实现 2 分频. JK 触发器的工作原理类似, 可以实现 2 分频和 4 分频等不同的预分频比例.

模数计数器预分频器

模数计数器预分频器是一种基于模数计数器的预分频技术. 模数计数器可以对输入信号进行连续计数, 当计数值达到预设值时, 计数器清零并输出一个信号脉冲. 通过调整计数器的模数值, 可以实现任意整数倍的预分频比例.

上升沿和下降沿

上升沿和下降沿是数字信号处理中常见的概念, 它们分别描述了数字信号从低电平跳变到高电平 (0 到 1) 以及从高电平跳变到低电平 (1 到 0 ) 的瞬间.

- 上升沿: 当数字信号从低电平 (0) 变为高电平 (1) 时, 这个转变过程称为上升沿. 在此时此刻, 信号的店铺发生了正向跳变. 上升沿通常用于触发器, 计数器和其他数字电路的时钟输入, 因为它表示一个新的计数周期的开始

- 下降沿: 当数字信号从高电平 (1) 变为低电平 (0) 时, 这个转变过程称为下降沿. 此时此刻, 信号的电平发生了负向跳变. 下降沿同样可以用于触发器, 计数器和其他数字电路的时钟输入, 因为它也可以表示一个新的计数周期的开开

在数字电路中, 上升沿和下降沿的概念非常重要, 因为它们通常用于同步和计时操作. 许多数字电路元件, 如触发器, 计数器, 锁存器等, 都依赖于上升沿或下降沿来控制其工作状态. 此外, 上升沿和下降沿的概念也常用与通信系统中的数据传输, 例如用于检测和解码脉冲编码调制 (PCM) 信号.

应用场景

微控制器时钟预分频

在微控制器中, 预分频器通常用于生成不同频率的系统时钟. 例如, STM32 微控制器可以通过 PLL (锁相环) 和预分频器生成多种频率的系统时钟, 以适应不同外设的功耗要求.

通信系统中的频率合成

在无线通信系统中, 预分频器常用与频率合成和信号处理. 例如, 无线通信设备需要在不同频率下工作, 可以通过混频器, 锁相环 (PLL) 和预分频器相结合的方式, 实现频率的转换和合成.

计时器与 PWM 波形生成

在计时器和 PWM 波形生成应用中, 预分频器可以用于调整输出信号的频率. 通过改变预分频器的分频比例, 我们可以实现不同频率的计时和 PWM 波形.

数字电路设计中的同步与计时

在数字电路设计中, 预分频器可以用于生成不同频率的时钟信号, 以实现各种功能模块之间的同步和计时. 例如: 在数字信号处理器 (DSP) 或微处理器中, 预分频器可以为数据采集, 运算, 存储等模块提供适当的时钟信号.

预分频器实现方法

在实际应用中, 预分频器可以通过硬件和团建两种方式实现.

硬件预分频器

硬件预分频器主要依赖于计数器, 触发器, 模数计数器等电子元件. 这种方式实现的预分频具有较高的精度和稳定性, 适用于对时钟信号要求较高的场合. 常见的硬件预分频器有集成电路 (如 74 系列, CD4040 等) 和可编程逻辑器件 (如 CPLD, FPGA 等).

软件预分频器

软件预分频器是在微控制器内部通过软件编程实现的预分频方法. 这种方式的优点是灵活性高, 成本低, 但精度和稳定性相对较差. 在 STM32 等微控制器中, 可以通过定时器, PWM 等外设实现团建预分频.

案例

在 STM32 中, 预分频器广泛应用于定时器, PWM 波形生成和系统时钟设置等场景. 这里我们以一个使用 STM32 定时器产生不同频率的 PWM 波形为例, 来说明预分频器在 STM32 中的应用.

使用 STM32F103 系列产生一个 1kHz 的 PWM 波形:文章来源:https://www.toymoban.com/news/detail-431500.html

#include "stm32f1xx_hal.h"

TIM_HandleTypeDef htim2;

void SystemClock_Config(void);

static void MX_GPIO_Init(void);

static void MX_TIM2_Init(void);

int main(void)

{

HAL_Init();

SystemClock_Config();

MX_GPIO_Init();

MX_TIM2_Init();

// 开启TIM2 PWM输出

HAL_TIM_PWM_Start(&htim2, TIM_CHANNEL_1);

while (1)

{

}

}

void SystemClock_Config(void)

{

RCC_OscInitTypeDef RCC_OscInitStruct = {0};

RCC_ClkInitTypeDef RCC_ClkInitStruct = {0};

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSE;

RCC_OscInitStruct.HSEState = RCC_HSE_ON;

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;

RCC_OscInitStruct.PLL.PLLMUL = RCC_PLL_MUL9;

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)

{

Error_Handler();

}

RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_HCLK|RCC_CLOCKTYPE_SYSCLK

|RCC_CLOCKTYPE_PCLK1|RCC_CLOCKTYPE_PCLK2;

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;

RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1;

RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV2;

RCC_ClkInitStruct.APB2CLKDivider = RCC_HCLK_DIV1;

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_2) != HAL_OK)

{

Error_Handler();

}

}

static void MX_TIM2_Init(void)

{

TIM_ClockConfigTypeDef sClockSourceConfig = {0};

TIM_MasterConfigTypeDef sMasterConfig = {0};

TIM_OC_InitTypeDef sConfigOC = {0};

htim2.Instance = TIM2;

htim2.Init.Prescaler = 7199; // 预分频器:7200 - 1

htim2.Init.CounterMode = TIM_COUNTERMODE_UP;

htim2.Init.Period = 99; // 自动重装载寄存器:100 - 1

htim2.Init.ClockDivision = TIM_CLOCKDIVISION_DIV1;

if (HAL_TIM_Base_Init(&htim2) != HAL_OK)

{

Error_Handler();

}

sClockSourceConfig.ClockSource = TIM_CLOCKSOURCE_INTERNAL;

if (HAL_TIM_ConfigClockSource(&htim2, &sClockSourceConfig) != HAL_OK)

{

Error_Handler();

}

if (HAL_TIM_PWM_Init(&htim2) != HAL_OK)

{

Error_Handler();

}

sMasterConfig.MasterOutputTrigger = TIM_TRGO_RESET

总结

预分频在数字系统中起着关键作用, 通过降低时钟频率, 可以实现不同功能模块的同步, 计时以及频率合成等目的. 了解预分频器的工作原理, 应用场景和实现方法, 有助于我们在实际工程中更好的应用预分频技术.文章来源地址https://www.toymoban.com/news/detail-431500.html

到了这里,关于【STM32】知识补充 深入探讨预分频器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!