使用FPGA驱动AD9910的方法总结

前言

虽然AD9910芯片老掉牙了,但是还有人在使用。前段时间一直比较忙,又赶上换工作,没时间写博文。最近才慢慢的闲下来,所以又开始分享一下自己工作中的调试经验。

一、概述

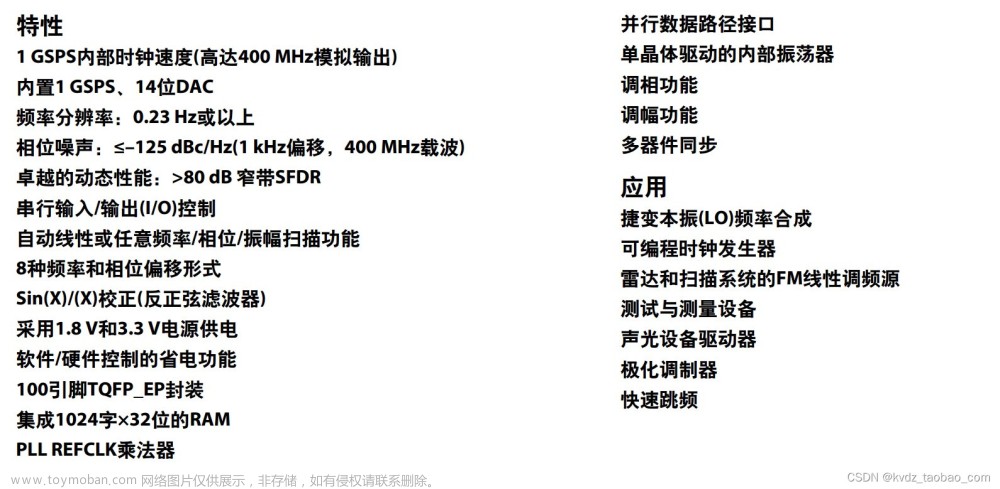

AD9910是一种直接数字合成器(DDS),具有集成的14位DAC,支持高达1 Gsps的采样率。AD9910采用了先进的专有DDS技术,在不牺牲性能的情况下显著降低了功耗。DDS/DAC组合形成了一个数字可编程的高频模拟输出合成器,能够在高达400 MHz的频率上生成频率灵活的正弦波形。

用户可以访问控制DDS的三个信号控制参数:频率、相位和幅值。DDS通过其32位累加器提供快速跳频和频率调谐分辨率。在1 Gsps采样率下,调谐分辨率为~0.23 Hz。DDS还能实现快速相位和振幅切换能力。

AD9910通过串行I/O端口编程其内部控制寄存器进行控制。AD9910包括一个集成的静态RAM,以支持频率、相位和/或幅度调制的各种组合。AD9910还支持用户定义的、数字控制的数字斜坡操作模式。在这种模式下,频率、相位或振幅可以随时间线性变化。对于更高级的调制功能,包括一个高速并行数据输入端口,以实现直接的频率,相位,幅度或极性调制。

二、寄存器配置

1.SPI串行接口

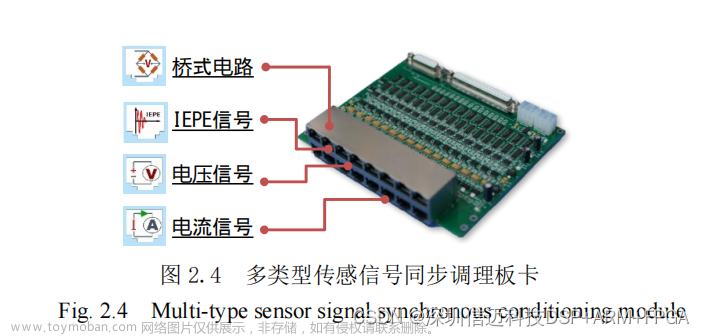

AD9910串行端口是一个灵活的同步串行通信端口,可以方便地连接到许多工业标准的微控制器和微处理器。串行I/O与大多数同步传输格式兼容。看完器件手册后,这种寄存器配置时序就是一种SPI时序。我的项目由于是后期只需要写入寄存器,不需要读取,故将SDIO引脚作为单向输入引脚,而且项目开始时也没有接SDO引脚,所以不能读取寄存器值。后期调试中必须确认数据是否正确写入寄存器,又将SDO数据输出引脚接入。这样和csn、sclk组成了标准的SPI接口,对应关系如下:

| I/O接口 | 描述 |

|---|---|

| SCLK | 时钟 |

| CSN | 片选 |

| SDIO | MOSI,主输出从输入 |

| SDO | MISO,主输入从输出 |

注:详细的接口说明请查看数据手册。

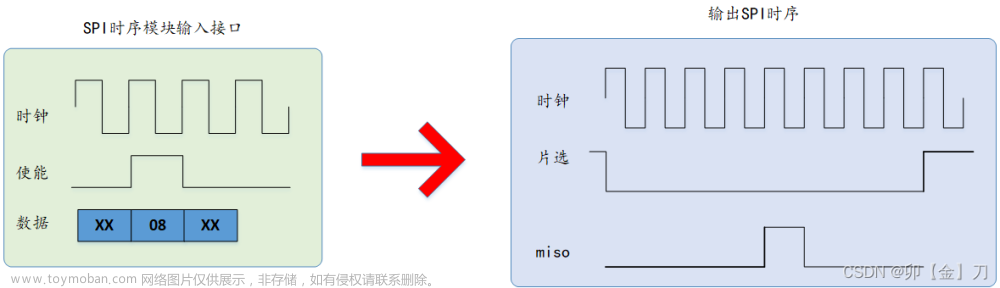

1.SPI读写时序

和其它的SPI时序类似,操作基本是“指令+数据”的形式。指令字节包含以下信息,如指令字节信息位图所示。

D7:决定在指令字节写之后是否发生读或写数据传输。逻辑1表示读操作。0表示写操作。

D4-D0:决定了在通信周期的数据传输部分访问哪个寄存器,即所操作的寄存器地址。

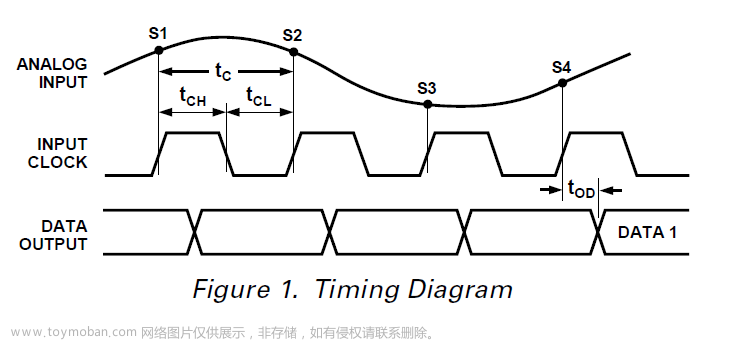

时序图如下:

关于spi读写时序,我在程序中使用了自己设计的一个代码,这段代码在实现时比较简单,只需要提供输入/输出字节数据和对应使能就可以实现spi读写时序。(有需要的小伙伴可以CSDN私信我,PS:有偿的吆!)

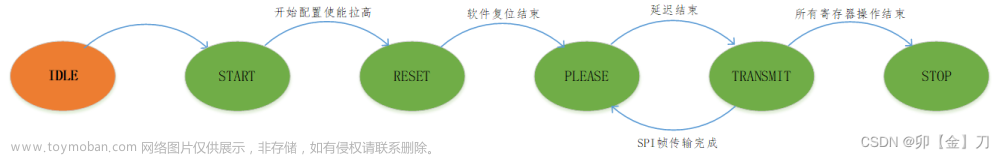

2.状态机设计实现寄存器读写

根据寄存器配置方法,芯片配置需要上电复位,寄存器写入延迟等要求,设计如下状态机:

| 状态机名称 | 描述 |

|---|---|

| IDLE | 空闲状态 |

| START | 起始状态 |

| RESET | 复位状态 |

| PLEASE | 复位状态 |

| TRANSMIT | 地址/寄存器数据传输状态 |

| STOP | 停止状态 |

状态图如下所示:

在实现寄存器配置的流程中,由上述状态机实现。当程序复位后,状态直接从空闲状态跳转到开始状态。当上层程序拉高开始使能后,就开始寄存器配置,此时状态跳转到复位状态。在复位状态,复位时长为2ms。之后状态跳转到请求等待状态,该状态会有一个计数器等待延迟。当延迟达到后状态跳转到spi指令数据传输状态,开始写、读寄存器。之后再跳转到延迟等待状态。当所有的需要配置的寄存器都操作完之后就跳转到停止状态。结束寄存器配置。并输出使能告诉上层模块配置完成。

3.单频调制模式

在上述寄存器配置完以后,就可以使用单频调制模式简单的输出频率了。具体怎么配置,需要配置哪里的寄存器手册里由详细说明,这里不再赘述。

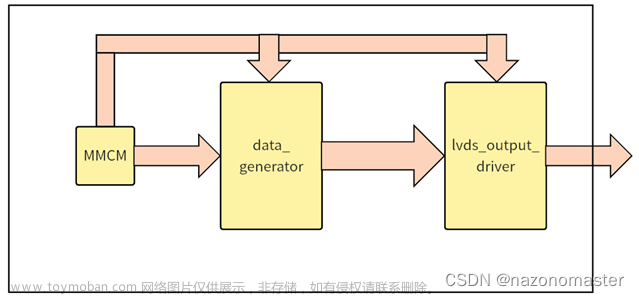

三、并口时序控制

并行端口的主要信号控制时序如下图所示,只有在发送使能拉高时,输入数据才有效,并且在时钟的上升沿将数据锁存到器件中。在并行数据端口调制模式中,调制的DDS信号控制参数直接由18位并行数据端口提供,由16位数据字和2位目的字组成。而DDS的频率控制字却有32位,故要想精确的让DDS产生准确频率的信号,就必须使得频率控制字为2的整数倍关系,由于DDS的系统频率和解码FFT的系统频率相同,进而计算出的各个频率对应的频率控制字为n*2^21 (n=1,2,3…),这样只需要将频率控制字的高16位给到DDS就可以精确输出对应频率的正弦波。具体的频率控制字事先计算好存储在rom中,通过和源数据的映射关系,在控制程序中调用。

注意:当TxENABLE引脚为false时,设备内部会清除输入的16位数据字,或者它保留TxENABLE切换到false状态之前数据端口上的最后一个值(基于数据汇编程序的设置保持最后一个值位)。CFR2[6]:对应数据汇编器保留最后值的设置情况,当该位为0时,当TxEnable为假时,并行端口的数据会被忽略,且内部路径也会被清零。当为1时,当TxEnable为真时,并行数据端口数据汇编器强制保持从并行端口收到的最后值。

四、锁相环倍频器

内部锁相环(PLL)提供了使用参考时钟频率的选项,该频率明显低于系统时钟频率。锁相环支持广泛的可编程倍频系数(12~127)实际测试发现根本达不到最大倍数以及可编程电荷泵电流和外部环路滤波器组件(通过PLL_LOOP_FILTER引脚连接)。这些特性为锁相环增加了额外的灵活性,

允许优化相位噪声性能和频率计划开发的灵活性。锁相环还配有PLL_LOCK引脚。

锁相环的输出频率范围(fSYSCLK)被内部VCO限制在420 MHz≤fSYSCLK≤1ghz范围内。此外,用户必须将VCO编程为六个操作中的一个使fSYSCLK在指定范围内。

其中最主要的配置为:文章来源:https://www.toymoban.com/news/detail-431551.html

- 频率范围:VCO_SEL=CFR3[26:24];

- PLL倍频倍数:N=CFR3[7:1](该参数特别不准,不是你实际配置倍数,我是多次实验后根据输出频率,频率控制字反推回系统频率的,这里有点坑人,手册没有细说。)

总结

在实现ad9910的驱动程序编写中,最困难的是寻找合适的系统时钟频率,由于手册没有说明,而且倍频倍数N的参数设置好像不是真实的倍数,导致我只能一遍遍的修改输入参数,来看到底哪个倍数是合适的。不过最终调试下来还是收获很大。如果由想需要我的程序源码的小伙伴可以私信我,百度网盘分享给你。PS:创作不易,有偿的吆,介意的朋友请绕道,谢谢!!!文章来源地址https://www.toymoban.com/news/detail-431551.html

到了这里,关于用FPGA驱动AD9910输出跳频信号的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!