FPGA开发离不开IO约束和时序约束,IO约束用于确定输入/输出端口的物理端口和电气特性,与芯片和电路设计有关。而时序约束则用于设定FPGA设计中的时序特性,以确保系统能够在预期时钟频率下正常运行。本文将介绍vivado中常见的设置约束的方法。

一、IO约束

IO约束,实际上是将工程的输入输出端口与芯片的引脚关联起来,所以需要参考芯片手册和实际电路设计。在vivado中通常有两种加入IO约束的方式:

1、通过GUI界面设置IO约束

(1)创建vivado工程,并添加HDL文件。

(2)点击“Run Synthesis”,执行综合,等待综合完成。

(3)点开 “Open Synthesized Design”,等待打开综合结果。

(4)点开vivado菜单栏右上角的,窗口选择“I/O Planning”。

(5)vivado出现“IO Ports”窗口,根据电路图和芯片手册,定义引脚位置和电气标准。

(6)设置完后,按快捷键“ctrl + s”保存,填入约束文件名。

(7)在“source”窗口,点开“Constraint”下的“constrs_1”可看到创建的约束文件,点开即可看到约束的内容。

2、直接创建xdc文件并加入IO约束

可通过点击“source”窗口的“+”创建xdc文件。

(1)引脚分配设置

“pin name”是芯片的引脚,ports是工程中定义的模块名

set_property PACKAGE_PIN <pin name> [get_ports <ports>](2)引脚电气标准设置

“IOSTANDARD”是电气标准,如LVCMOS18、LVCMOS12、LVCMOS33

set_property IOSTANDARD <IO standard> [get_ports <ports>](3)引脚驱动能力设置

set_property DRIVE <2 4 6 8 12 16 24> [get_ports <ports>](4)引脚抖动设置

set_property SLEW <SLOW|FAST> [get_ports <ports>](5)引脚上拉设置

set_property PULLUP true [get_ports <ports>](6)引脚下拉设置

set_property PULLDOWN true [get_ports <ports>]二、时序约束

FPGA时序与资源的平衡是永恒的话题,时序约束是非常重要的,实际上是设定整个FPGA工程的时序特性,比如整个工程模块的运行的时钟频率,这样就能让编译器根据设定约束在FPGA中布线,如果时序不满足,整个FPGA系统可能运行的状态不稳定,达不到设计要求。

1、通过GUI界面设置时序约束

(1)点开 “Open Synthesized Design”,等待打开综合结果,再点开“Open Synthesized Design”选项,单击“Edit Timing Constraints”。

(2)打开了“Timing Constraints”,点击“+”。

(3)弹出“create clock”,单击“source objects”右侧“ … ”按钮。

(4)弹出“specify clock source objects”,点击”find”。在“result”窗口中选择“clk”,单击右侧的“→”,将其添加到“selected”窗口中,再点击set。

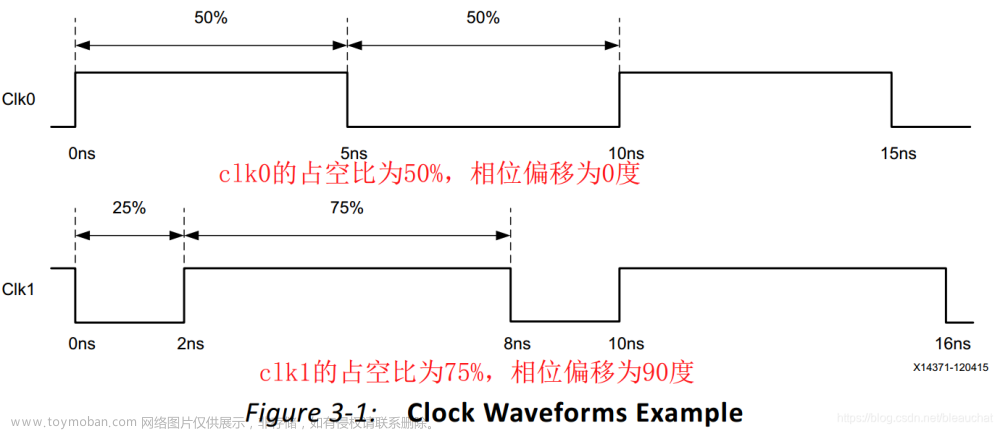

(5)返回“create clock”,设置时钟周期和占空比,点击“OK”。

(6)按“Ctrl + s”保存,再打开top_io.xdc的窗口,可看到新增了时序约束。

2、直接创建xdc文件并加入时序约束

时序约束命令

create_clock -period 10.000 -waveform {0.000 5.000} [get_ports clk]三、总结

本文介绍了常用的设置IO约束与时序约束的方法,大家可以参考下,掌握配置约束文件的方法,使用正确的I/O约束方法和语法可以确保FPGA设计的正确性和可靠性。

本文将不断定期更新中,码字不易,点⭐️赞,收⭐️藏一下,不走丢哦

本文由FPGA狂飙原创,有任何问题,都可以在评论区和我交流哦

学习资料分享,github开源代码:“FPGA知识库”文章来源:https://www.toymoban.com/news/detail-431763.html

您的支持是我持续创作的最大动力!如果本文对您有帮助,请给一个鼓励,谢谢。文章来源地址https://www.toymoban.com/news/detail-431763.html

到了这里,关于Vivado约束添加方法:一文全面解析IO和时序约束的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!